接口电路中的抗干扰技术

2010-12-11李秀莲孙定浩

李秀莲,孙定浩

(北京控制工程研究所,北京100190)

接口电路中的抗干扰技术

李秀莲,孙定浩

(北京控制工程研究所,北京100190)

设计两种将星上计算机控制器指令信号输出端与部件输入端连接的接口电路.它能抵抗从计算机控制器指令信号输出端发出的宽脉冲干扰,并能将控制器指令信号变换为部件所需的驱动信号.文中给出一些解析结果,可用来根据抗干扰要求和驱动要求计算接口电路中各主要元器件的参数值.

接口电路;抗干扰技术

本文讨论的接口电路是指星上控制器指令信号经过整形后的电压信号输出端VA到驱动电路输入端的这部分电路.通常,驱动电路中被VA直接驱动的是晶体管或达林顿晶体管.以往的接口电路一般由两个电阻组成(基极泄漏电阻和将VA与基极连接的限流电阻)[1].按常规,为防止印制板上通过寄生电容耦合到晶体管基极的微秒级以下的干扰,泄漏电阻接≤0.1μF的旁路电容[2].近年来随着星上总体测试新需求的提出,抗干扰能力的要求也不断提高,提出克服毫秒级的脉宽干扰信号的要求,常规的接口电路不再适用.

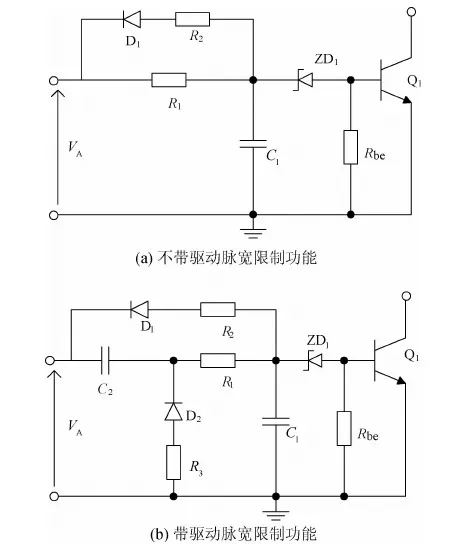

本文设计了如图1所示的接口电路(其中Q1是继电器驱动电路中被驱动的晶体管,Rbe是泄漏电阻)试图满足这种需求.图1(a)不限制驱动基极的电流脉宽,即驱动电流与VA同时为零.图1(b)限制驱动基极电流的脉宽;当VA超过设定的脉宽,基极电流幅值逐渐衰减为零.文中给出了根据抗干扰要求和驱动要求计算接口电路中主要元器件参数的解析表达式.通过选择恰当的元器件参数,可以抵抗不同宽度的毫秒级的脉冲干扰.

图1 抗宽脉冲干扰接口电路

1 两种接口电路

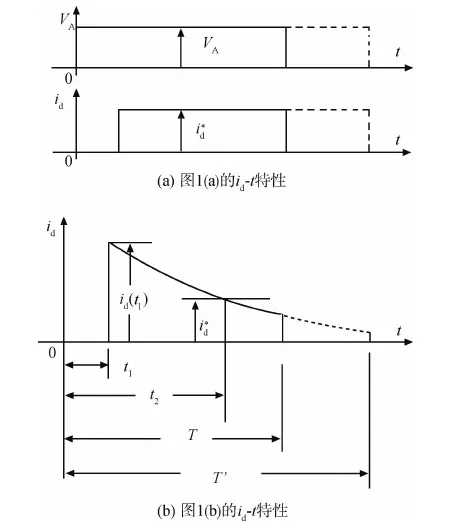

图1示出的两种接口电路.干扰脉冲(与VA等幅、脉宽小于设定值t1)经R1和C1(图1(a))或C2、R1和C1(图1(b)),在C1上转化为一个指数上升的电压;ZD1是为了使Q1保持断开状态在C1两端允许电压的最大值(本文推荐值为VA/2,以后简称“门限”);D1和R2是当干扰消失(VA=0)后,释放C1存储电荷的通道,为再次承受干扰脉冲作准备;C2为隔直电容,用来限制驱动电流的宽度为t2-t1( 图2(b)),其目的是防止VA出现长时间处于高电平的故障状态;C2的放电通道是D2和R3.

图2 图1的id-t特性

2 元件模型和等效电路

将图1(a)和 (b)中串联的稳压管ZD1和被驱动晶体管Q1的b-e极用以下模型表征:

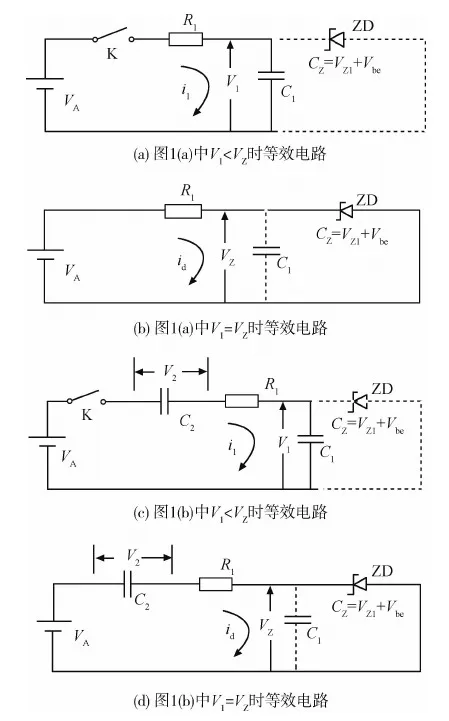

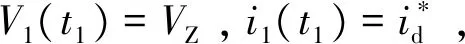

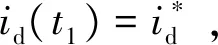

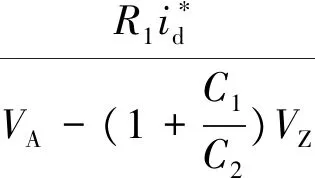

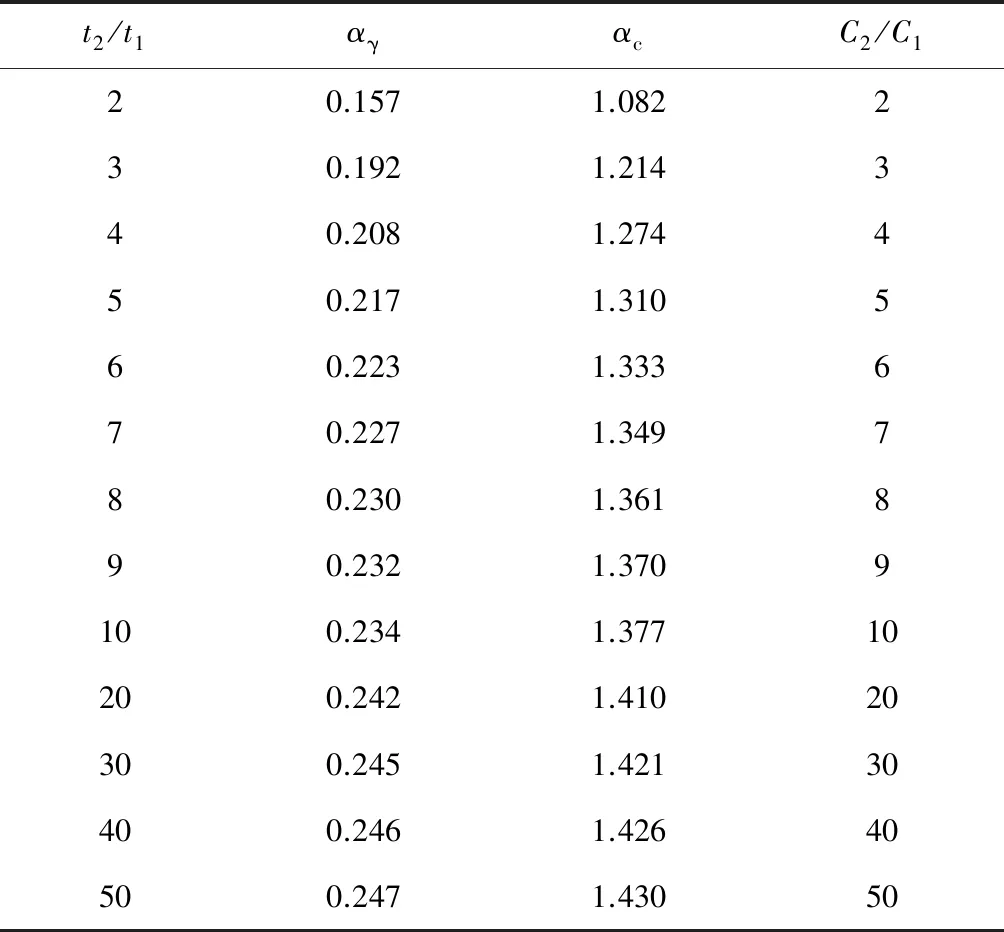

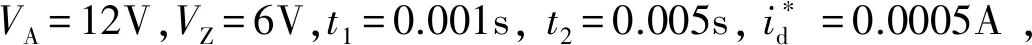

其中,id是通过ZD1和Q1基极的电流,V1是加在这两个串联元件两端的电压,VZ是ZD1的稳压值VZ1和Q1的b-e极导通电压Vbe之和(VZ 设VA在t=0~T之间为高电平,此时图1(a)、(b)的等效电路为图3(a~d).设t=0时,V1(0)=V2(0)=0. 3.1图3(a、b)解析结果 图3 VA高电平时图1的等效电路 设K在t=0时接通,图3(a)中i1(t)和V1(t)满足以下方程 解(3)~(5)方程得 式(9)中对数函数的值为负,故C1> 0 .图1(a)按式(8)(9)设定R1、C1值,则实现图2(a)的id-t特性. 3.2图3(c、d)解析结果 设K在t=0时接通,图3(c)中i1(t)、V1(t)和V2(t)满足以下方程 由式(12)得 式(13)、(14)的解是 令t=t1时V1(t1)=VZ得 当t>t1,V1=VZ,由图3(d)知id(t)和V2(t)满足以下方程 解式(17)~(19)得 由式(20)得 将式(16)代入式(22)得 由式(16)可得 因式(24)中自然对数函数的值应为负,因此比值C2/C1应满足条件 即 现对比值C2/C1作两种选择以进一步讨论式(23)和(24). 第一种选择:设C2/C1=t2/t1,VZ/VA=0.5,由式(23)(24)得 其中, 表1列出不同t2/t1值时αγ和αc值. 第二种选择:设C1/C2=2t2/t1,VZ/VA=0.5,由式(23)、(24)得 表1 C2/C1=t2/t1时αγ和αc的计算值 其中, 表2 C1/C2=2(t2/t1)时和的计算值 C2=5×0.252=1.26μF, 若选C2/C1=2t2/t1,由式(31)、(32)和表2得 C2=10×0.17=1.7μF. 以上这两组数据都是工程易实现的.比较这两组数据可以推论,若进一步提高C2/C1和t2/t1的比值,C1将减小,R1和C2将加大. 本文以理想元件模型、起始条件V1(0)=V2(0)=0得式(8)、(9)和式(23)、(24),在选择器件参数时提出了计算方法,具有理论指导意义.在实际应用中,应考虑在重复出现干扰脉冲时V1(0)≠0、V2(0)≠0情况,还应考虑其他综合因素.为此,可将这些式中的t1值改为适当大于要求的抗干扰脉宽. 对于接口电路应注意分析Q1基极在控制器指令输入出现干扰时的工况.在图1接口电路中,由于用ZD1提升Q1基极抗干扰门限,则具有这样的特性:只要干扰在ZD1的阴极产生的电位低于这个门限,Q1基极的电位恒保持为零;既不会因这个干扰的存在降低Q1基极抗其他干扰的“能力”,这是本设计的一个重要考虑.若用一个电阻代替ZD1,Q1基极电位则随C1电位上升而提高,基极抗其他干扰的能力下降. [1] 童诗白.模拟电子技术基础[M].北京:高等教育出版社,1980 [2] 常玉燕.日本电子电路精选[M].北京:电子工业出版社,1989 Anti-InterferenceTechniqueforInterfaceCircuits LI Xiulian,SUN Dinghao (BeijingInstituteofControlEngineering,Beijing100190,China) Two kinds of interface circuits to interface the output terminator of the computer controller with the input terminator of a component in a spacecraft are designed in this paper.The circuits possess the function of anti-interference wide impulse and convert the computer controller signal to the driving current required by the component.Some detailed analytical results derived from this paper can be used to calculate parameter values of main elements in the circuits according to the requirements for anti-interference and driving. interface circuit; anti-interference technique 2010-05-05 李秀莲(1961—),女,山西人,高级工程师,研究方向为电子线路设计(e-mail: lixiulian@hotmail.com ). TN78 A 1674-1579(2010)04-0042-043 等效电路分析

4 结 论