TD-LTE系统中咬尾卷积码译码器的FPGA实现

2010-11-05李小文

林 丹,李小文

(1 重庆邮电大学 计算机学院,重庆 400065;2 重庆邮电大学 通信学院 重庆 400065)

0 引言

LTE采用下行正交频分多址(OFDM),上行单载波频分多址(SC-FDMA)的方式[1]。OFDM是LTE系统的主要特点,它的基本思想是把高速数据流分散到多个正交的子载波上传输,从而使子载波上的符号速率大大降低,符号持续时间大大加长,因而对时延扩展有较强的抵抗力,减小了符号间干扰的影响[2]。在LTE系统中,为了获得正确无误的数据传输,要采用差错控制编码技术。

很多数据通信标准采用卷积码作为前向纠错的方法[3]。采用这种编码方式的数据通常都使用Viterbi译码器进行译码,Viterbi译码器受格形状态概率和分支度量的约束。传输的数据通常由一串0比特结尾,以强制编码器回到0状态,这样译码器能从已知的状态开始译码,但是信道必须传输额外的符号[4]。

另一种方法是保证格形起始和终止于某个相同的状态,称之为咬尾技术,它具有不要求传输任何额外比特的优点。咬尾在几种流行的通信标准里使用,如IEEE802.16,LTE等。

本文介绍了在FPGA中实现的咬尾卷积码的Viterbi 译码算法。算法在整体延迟一段时间后,正确输出译码结果。

1 咬尾卷积码

咬尾卷积码的约束长度为7,编码率为1/3。卷积码的编码器配置如图1所示。

编码器的移位寄存器的初始值应当设置为输入流的最后6位信息比特,这样移位寄存器的初始和最终状态保持一致。若用表示编码器的6个移位寄存器,则移位寄存器的初始值应当设

咬尾试图解决传输多余的终止比特的问题。在包传送之前,包的最后Z个数据比特用来初始化编码器移位寄存器,也就是编码器的起始状态和终止状态由包指定。这也隐含了在传输第一个符号前整个数据包对于编码器来说必须是可用的。

另一种方法是先用开始的Z个数据比特初始化编码器,在这个时间内不传输任何输出符号,然后余下的(N-Z)个数据比特进行编码并传送,开始的Z个比特紧跟在最后进行编码。这种方式同样使编码器的初始状态和终止状态相同。这种方法的优点是在编码开始前不需要获得整个数据包,但是接收器接收到的编码后的序列不是正序。

咬尾技术具有以下优点:

●不影响编码率,总的传输比特为N/R;

●不影响卷积码的错误校验属性。

这项技术也有以下缺点:

●译码延迟增加了,因为必须确定正确的起始状态和回溯的初始状态;

●接收器复杂度略微增加。

2 实现

2.1 传统viterbi译码

Viterbi译码算法[5]是由Viterbi于1967年提出的降低计算复杂度的算法。它是计算网格图上在时刻 到达各个状态的路径和接收序列之间的相似度,或者说距离,去除不可能成为最大似然选择对象的网格上的路径,即,如果有两条路径到达同一状态,则具有最佳度量的路径被选中,称为幸存路径。对所有状态都进行这样的选路操作,译码器不断在网格上深入,通过去除可能性最小的路径实现判决,从而降低译码器的复杂性。

图1 1/3编码率的咬尾卷积编码器

Viterbi译码算法一般的实现流程如图2所示。由图2可以看出Viterbi算法的主要实现过程可分为4大部分:分支度量计算(BMC);加比选(ACS);存储幸存路径存储器(SSM);输出判决(OD)。

图2 Viterbi译码算法处理流程

在某些应用中,Viterbi译码是根据接收到的符号逐数据块进行译码,与邻数据块之间是相互独立的,即在每个数据块内进行译码,各数据块之间相互独立[6]。

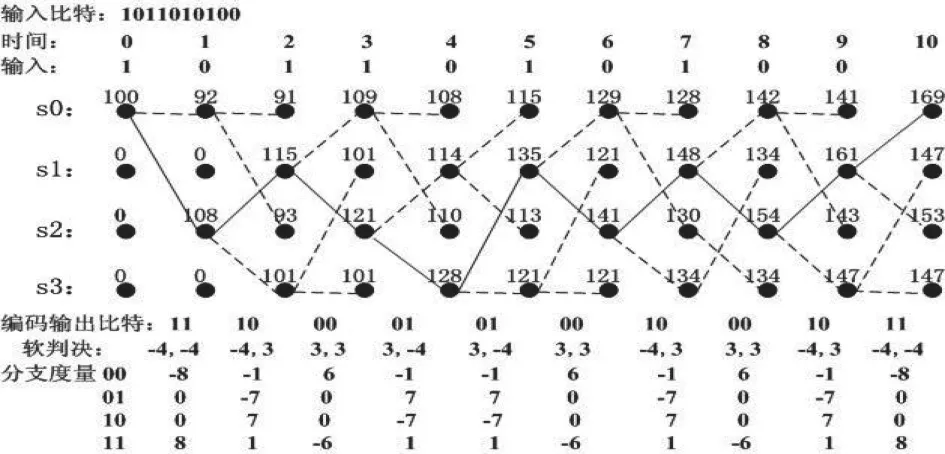

从图3我们可以清楚的看到,对输入的数据通过编码器进行卷积编码,到最后的输出译码结果,总过经历了以下几个过程:

(1)对输入的数据进行卷积编码,编码速率为1/2,即每输入一个比特编码输出两个比特。

(2)将每次编码输出的两个比特量化为相应的数值,通过每一组数值计算出该组4个状态(s0,s1,s2,s3)的分支度量值,即BM值。

(3)进行加比选(ACS)运算,同时保存路径信息。如图2,首先在0时刻给4个状态(s0,s1,s2,s3)赋初始路径向量值(PM):假如起始点为状态s0,则状态s0的初始路径向量值为PM0=100(该数值根据实际的情况来定,如回溯深度和分支度量值等,以便计算),状态s1,状态s2,状态s3的初始路径向量赋值为PM1=PM2=PM3=0。

(4)ACS过程。因为到达每一个状态的有两条路径(见图3),例如到达状态s0(00)的两条路径分别是s0(00)和s1(01),从中选出到达s0路径度量值最大的一条路径作为幸存路径。如图 2, 若 从 0时 刻 到 1时 刻 :BM0=-8,BM1=0,max{PM0+BM0,PM1+BM1}=PM0+BM0=92,所以1时刻到达状态s0的保留路径为0时刻从状态s0来的路径,从而更新1时刻s0的PM0=92,同时由于1时刻到达s0的是“0”路径,所以保存的该时刻s0的路径信息是0(若是“1”路径,则保存的该时刻s0的路径信息为1),以此类推可求出该时刻到达状态s1,s2,s3的幸存路径,存储该路径信息,更新其路径度量值PM。

(5)输出判决(OD),即回溯过程,就是根据回溯深度以及ACS过程中所保存的PM值和幸存路径信息进行相应的算法回溯出译码结果。

图3 Viterbi译码实现过程

2.2 咬尾卷积码的viterbi译码实现

在多数的咬尾应用里,在传输之前使用数据包的最后Z个比特来对编码器状态进行初始化,这样在一个数据包内编码器具有相同的起始和终止状态,对于最佳译码来说,译码器的应该从这个状态开始构建格形,否则,由于在包的开始阶段进行错误校正会降低似然度,从而导致BER增加。

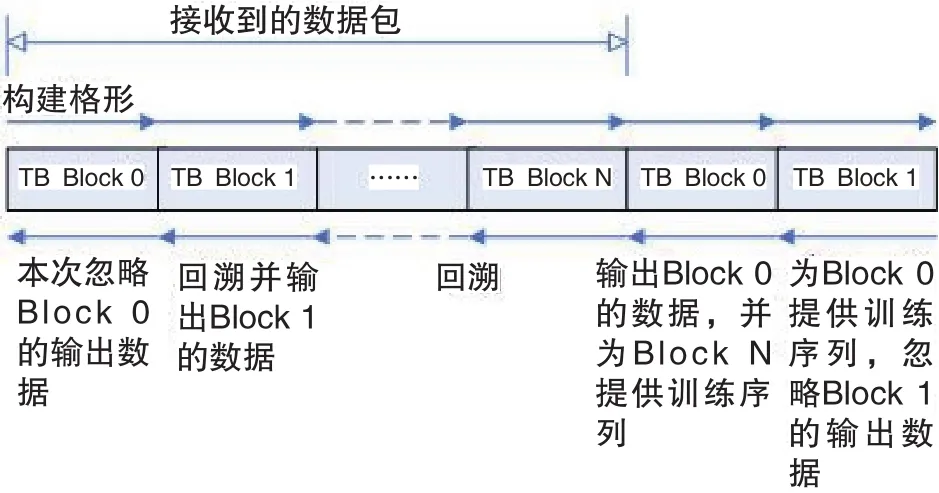

如果一个数据包内有多个回溯长度,一种方法是在包的末尾译码第一个TB块(传输块)。假定数据包终止于正确状态,TB块 0的格形构建开始于正确的起始状态,如图4所示,这个例子假定一个数据包包含了(N+1)个回溯长度。

图4 咬尾卷积译码

在数据包的开始阶段,TB块0用来确定TB块1的正确起始状态。由于在构建格形时并不知道从哪一个状态开始,因此此时译码的TB块0可能是不正确的,先忽略TB块0的数据输出。……

在末尾重新插入块0,则块N可以作为训练序列,为块0提供正确的起始状态。这种方法明显地为块0增加了额外的译码延迟。除了起始和终止的数据块外,其他的数据块都是按正常方式解码,每个块的终止状态都自动地为下一个块提供起始状态。

另一种方法是先输入数据块N,忽略输出数据。这种技术给格形结构的TB块0提供了正确的起始状态。这个块之后紧跟着块0到块N的数据。TB块0在末尾处再次输入以给TB块N的译码提供训练序列。这种方法的优点在于译码器端所有的数据都是以正确顺序输出。缺点是必须等待所有的包被接收完才能开始译码。

若一个数据包只含有一个回溯长度的数据,那么可以把块0通过译码器3次,则以上的方法同样有效。第一次给格形结构确定正确的起始状态,第二次构建格形,第三次进行正确的训练以使回溯开始于正确的状态(见图5)。

图5 单个数据块

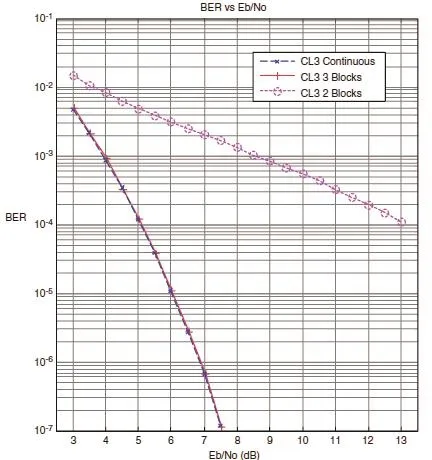

TB块0必须通过3次,若只通过了2次,则会增加BER,导致几乎所有的包都错误解码。在第6节的性能分析中的曲线显示了其性能。

3 仿真结果

使用verilog语言[7]在ISE[8]中进行综合、实现,布线后的时序仿真图如图6,图6为正确的维特比译码时序仿真图,输入的比特序列为一串随机数,经过卷积编码后输入到Viterbi译码器,最后输出的译码序列与输入序列一致。本译码器实现了正确的译码功能。

图6 时序仿真图

4 性能分析

图7显示了一个32个符号的数据块,约束长度为3。图中咬尾编码的数据块通过译码器3次的曲线,与一个标准连续流(非咬尾)译码器几乎相同。数据块通过译码器两次的曲线显示相当坏的BER性能。对于更大的约束长度,由于选择正确起始状态的似然性的降低会使性能更差。

图7 BER性能

[1] 3GPP TS 36.201 v8.1.0: LTE Physical Layer-General Description(Release 8)[S]. 2008-05;7-8.

[2] 3GPP TS 36.211 v8.3.0: Physical Channels and Modulation (Release 8)[S]. 2008-05;71.

[3] 郑宇驰,周晓方,闵昊.OFDM 系统中Viterbi译码器的设计及FPGA验证[J].复旦大学学报,2005,44(6):923-927.

[4] Bill Wilkie and Beth Cowie.Viterbi Decoder Block Decoding-Trellis Termination and Tail Biting.XAPP551(1.0) February 14,2005.

[5] 张宗橙.纠错编码原理和应用[M].西安:西安电子科技大学出版社,2003.

[6] Martin Röder and Raouf Hamzaoui.Fast Tree-Trellis List Viterbi Decoding[J].IEEE Trans Communications,2006,53(3):453-460.

[7] 夏宇闻.verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008.

[8] EDA先锋工作室.Xilinx ISE 9.X FPGA/CPLD设计指南[M].北京:人民邮电出版社,2007.