基于SPI接口和FIFO缓冲器的大容量高速实时数据存储方案

2010-09-30李明磊潘文亮

李明磊,潘文亮

(中国科学院南海海洋研究所,广东广州510301)

基于SPI接口和FIFO缓冲器的大容量高速实时数据存储方案

李明磊,潘文亮

(中国科学院南海海洋研究所,广东广州510301)

以海洋湍流观测样机中的数据存储接口电路为例,介绍一种基于C8051单片机的SPI(串行外设接口)、FIFO(先入先出)缓冲器IDT72v01和闪存M25P64的大容量高速实时数据存储方案。该方案具有简易实用、运行稳定、低功耗、易扩展的特点,已成功应用于已开发的湍流监测仪器样机。

大容量存储;高速;SPI;FIFO

引言

现代海洋仪器工作过程中,由于长时间以及高速数据采集的工作配置,对存储器容量、存取速度以及稳定性都有了更高的要求。如果是以电池供电的自容式系统,还常常需要降低系统功耗,延长电池续航时间。随着硬件技术的发展,出现了文件格式为FAT16或FAT32的微型移动硬盘,CF卡、SD卡、TF卡等大容量微型存储设备,嵌入式单片机技术也为这些设备的应用提供了良好的硬件支持。但是这些设备要求的功耗相对比较大,适合于电池舱容量大或其他供电方式的仪器,并且电路、程序设计比较复杂,写入速率低,仅适用采样率比较低的海洋仪器。本文提出一种基于C8051单片机的SPI接口、FIFO缓冲器IDT72v01和大容量闪存M25P64的低功耗、大容量高速实时数据存储方案。

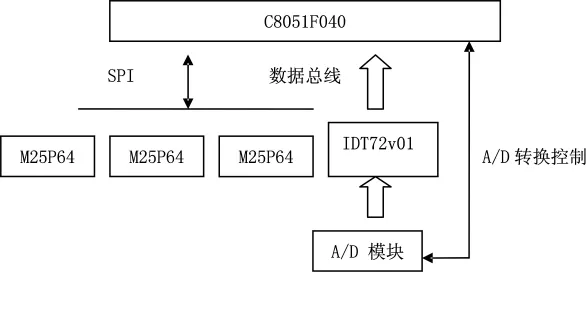

1 系统硬件结构

系统结构图如图1所示,存储部分硬件由FIFO芯片、大容量闪存M25P64和微处理器组成。FIFO缓存输入端为A/D转换模块,它负责把A/D转换后的数据写入缓存。实际应用中,这部分可根据需要(转换精度,速率等)变更,本文不做详细介绍。在本方案中,考虑到Flash芯片的性能,充分利用M25P64的页编程(一次写入256 byte数据)特性,选用存储空间为512*9 bit的FIFO芯片IDT72v01。数据转换点按时间顺序写入FIFO,达到一定容量后以块形式读出。这有别于一般应用中,通常通过485/232总线把数据发送到MCU再转存。MCU频繁进入串口中断,造成CPU使用效率低下。当采样率调高的时候,存储容易出错。系统工作过程为:系统启动后,首先对硬件初始化,然后启动数据采集系统把数据存到IDT72v01,当数据占据IDT72V01一半空间的时候,IDT72v01发出信号给单片机,单片机把数据取出,通过SPI接口,存储到闪存M25P64中。

图1 系统结构图

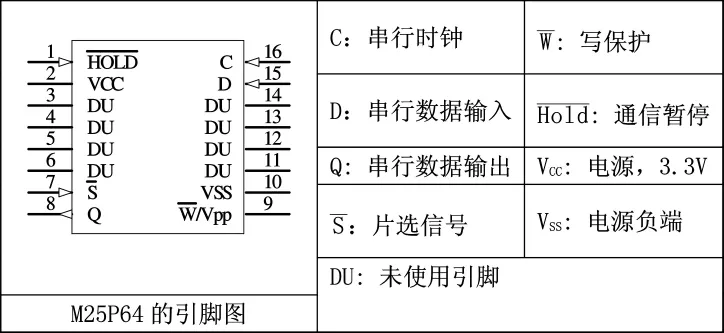

1.1 海量存储器M25P64的特性及硬件连接

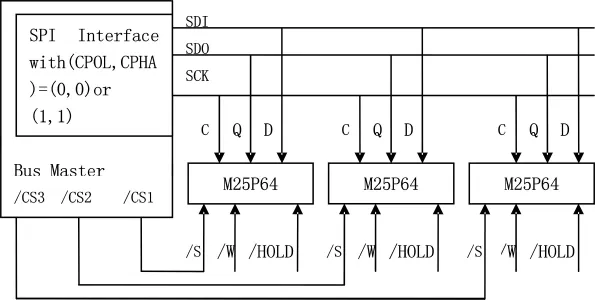

M25P64是意法ST公司生产的低功耗、用于嵌入式系统的大容量串行Flash存储器。M25P64的存储空间为64 Mbit,由32768个页面组成,每个页面为256字节。芯片支持页编程(256 Bytes);支持扇区擦除(512 Kbit)和块擦除(64 Mbit)。最高时钟频率50 MHz;可循环使用100 000次;保存数据年限超过20 a。功耗方面:2.7~3.6 V的工作电压;15 mA典型编程/擦除电流;4 mA典型读电流(20 mHz时钟频率);50 μA典型Standby电流。它具有超薄双面封装VDFPN8和贴片SO16两种封装。芯片引脚及说明见表1。工作方式上,芯片工作于3/4线串行总线方式,与同系列的芯片复用串行总线,可扩展更大容量的存储空间,芯片的读写电路接口见图2所示。

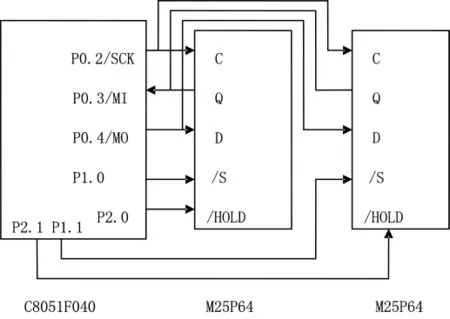

在本方案中,C8051F040片上集成SPI控制器,它的I/O口P0.2可复用为时钟输出连接到M25P64的时钟输入,P0.3复用为MISO(主控制器输入)连接到M25P64的数据输出,P0.4复用为MOSI(主控制器输出)连接到M25P64的输入端。然后使用其他I/O口控制M25P64的片选和通信状态--为高阻态或正常工作状态。笔者在实际设计中采用了一片C8051F040控制3片M25P64,总容量扩展到192 Mb。为简化起见,图3给出与两片M25P64之间的接口电路图。

表1 M25P64芯片引脚及说明

图2 M25P64与SPI总线控制器的接口电路图

图3 C8051F040和M25P64接口电路图

1.2 FIFO芯片IDT72V01的硬件接口

FIFO(First In First Out)简单说就是指先进先出。作为一种新型大规模集成电路,FIFO芯片以其灵活、方便、高效的特性,逐渐在高速数据采集、高速数据处理、高速数据传输以及多机处理系统中得到越来越广泛的应用。IDT72v01是一种高速、低功耗、双端口存储器,它内部存储空间为512*9 bit。采用9 bit的数据格式,第9位为数据奇偶校验位,在数据通信的时候可以起到抗干扰的作用。芯片容量为l K×9 b,输入/输出端口由单独的时钟和使能信号控制,具有“空”、“满”、“半满”和“几乎空、几乎满”标志。IDT72v01的9位输入/输出端口由单独的时钟和使能信号控制。输入端口由写使能信号(W)控制,当写使能W为低时,数据被连续写入FIFO存储器中。同样,输出端口由读使能信号(R)控制。IDT72v01还有一个复位端(/RS),当/RS为低时,IDT72v01的各个标志位全部回到原始状态。

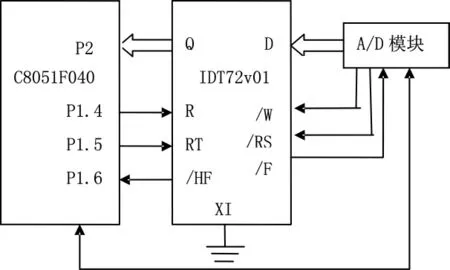

图4 C8051F040与IDT72v01硬件连接图

在本方案,把FIFO的“半满”(/HF)接到单片机输入引脚,这样单片机可实时查询FIFO缓冲器状态;把”R”和”RT”接到单片机输出引脚,单片机通过设置输出引脚电平时序实现缓冲器读操作。

2 系统软件设计

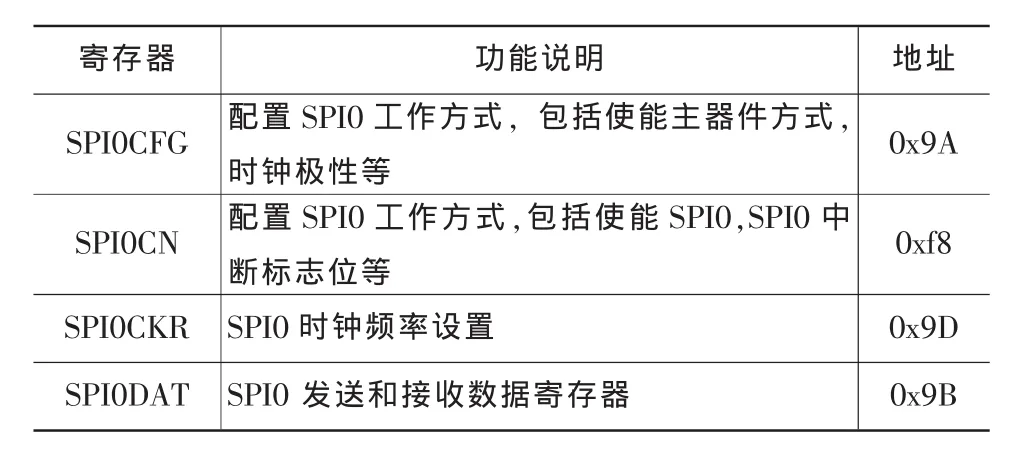

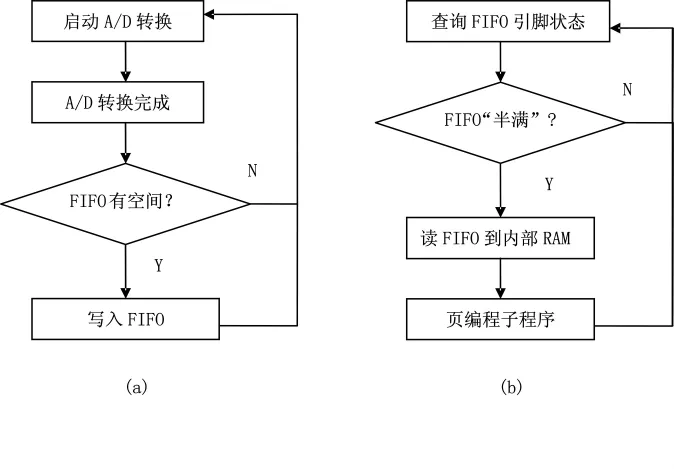

系统软件设计分为两部分,AD存储部分和海量存储部分。AD存储部分主要为FIFO写入端操作流程(见图5(a)),在“满”标志无效的情况下,A/D转换完成后把数据存储到FIFO缓存即可,相对比较简单。海量存储部分则比较复杂,系统上电后,C8051F040对它集成的SPI控制器(如表2所示)进行初始化,使它在电气特性上与M25P64接口兼容—包括时钟频率、极性、工作方式等。对于M25P64的操作,实际应用中将一些常用的操作编写为子程序,在需要时调用。根据图3接法和表3命令集,编写扇区擦除子程序,读操作子程序和页编程操作子程序,限于篇幅,略去。如图5(b)所示,单片机实时查询/HF状态,当它为低有效时,把缓存FIFO数据读出,以页编程写入M25P64。

表2 C8051F040 SPI控制寄存器

3 结语

图5 程序流程图

该方案充分利用单片机的SPI接口,在极少占用单片机引脚的情况下,实现了大容量数据存储器的扩展。利用FIFO缓冲器实现不同时钟域传输的数据匹配,实现了高速传输,提高了系统性能。由于采用基于C8051单片机的SPI接口、FIFO缓冲器IDT72v01和大容量闪存M25P6的设计,本方案可以满足海洋环境监测系统对于大容量高速实时数据存储的要求,已成功应用于湍流观测仪器样机。经实验室多次实验,数据存储完整准确。在容量要求方面,如果需要更大容量的存储空间,在该系统基础上略加改进,增加信号线,扩展更多的M25P64芯片则可使该系统适用于有更大存储空间要求的系统。

表3 M25P32命令表

[1]张培仁.基于C语言C8051F系列微控制器原理与应用[M]北京:.清华大学出版社,2007.

[2]潘琢金.C8051F040/1/2/3/4/5/6/7混合信号ISP FLASH微控制器数据手册.新华龙电子有限公司.

[3]ST Microelectronics.M25P64 Datasheet,2008.

[4]Integrated Device Technology.IDT72V01 Datasheet,2003.

Abstract:Taking the data storage in the ocean turbulence surveying prototype for example,a large-capacity high-speed real-time data storage scheme is introduced,which is based on the SPI interface embedded in C8051 MCU,the dual-port FIFO buffer IDT72v01 and the large-capacity flash memory M25P64.This data storage scheme has the characteristics of easy configuration,low power consumption and high reliability.It has been used for ocean turbulence surveying prototype successfully.

Key words:mass-storage;high-speed;serial peripheral interface;first-in first-out

Real-time and Large-capability Storage Scheme Based on SPI Interface and FIFO Cache

LI Ming-lei,PAN Wen-liang

(South China Sea Institute of Oceanology,CAS,Guangzhou Guangdong 510301,China)

P71,TP3

B

1003-2029(2010)02-0030-03

2009-12-16

国家高技术研究发展计划(863计划)“十一五”资助项目(2007AA09Z104)。

李明磊(1981-),男,广西容县人,博士研究生,主要从事海洋监测技术研究。