基于Verilog的全数字锁相环的设计

2010-09-15刘永勤

刘永勤

(渭南师范学院物理与电子工程系,陕西渭南 714000)

基于Verilog的全数字锁相环的设计

刘永勤

(渭南师范学院物理与电子工程系,陕西渭南 714000)

文章介绍了全数字锁相环的基本结构和工作原理,提出了一种基于 verilog的全数字锁相环的设计方法,并利用 QuartusII6.0软件对设计进行了时序仿真.

全数字锁相环;Verilog;FPGA

0 引言

锁相环路是一种反馈控制电路,锁相环的英文全称是 Phase-Locked Loop,简称 PLL.目前锁相环在通信、信号处理、调制解调、时钟同步、频率综合和自动化控制等领域应用极为广泛,已经成为各种电子设备中不可缺少的基本部件.随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理.因此,对全数字锁相环的研究和应用得到了越来越多的关注.

1 全数字锁相环的结构及基本原理[1]

所谓全数字锁相环,就是指应用于数字系统的 PLL,也就是说 PLL中的各个模块都是以数字器件来实现的.一阶全数字锁相环的基本结构体系如图 1所示.主要由数字鉴相器、脉冲加减电路、变模可逆计数器以及除N计数器四部分构成.变模计数器和脉冲加减电路的时钟分别为 Kclk和 IDclk.本设计中两个时钟使用相同的系统时钟信号.全数字锁相环根据输入信号和时钟输出信号之间的相位误差信号送入鉴相器,并对相对误差进行平滑滤波,由 K变模计数器产生控制信号,数控振荡器根据控制信号不断反馈调节,使输出信号的相位不断跟踪输入信号的相位,最终达到锁相的目的.

2 实现方案

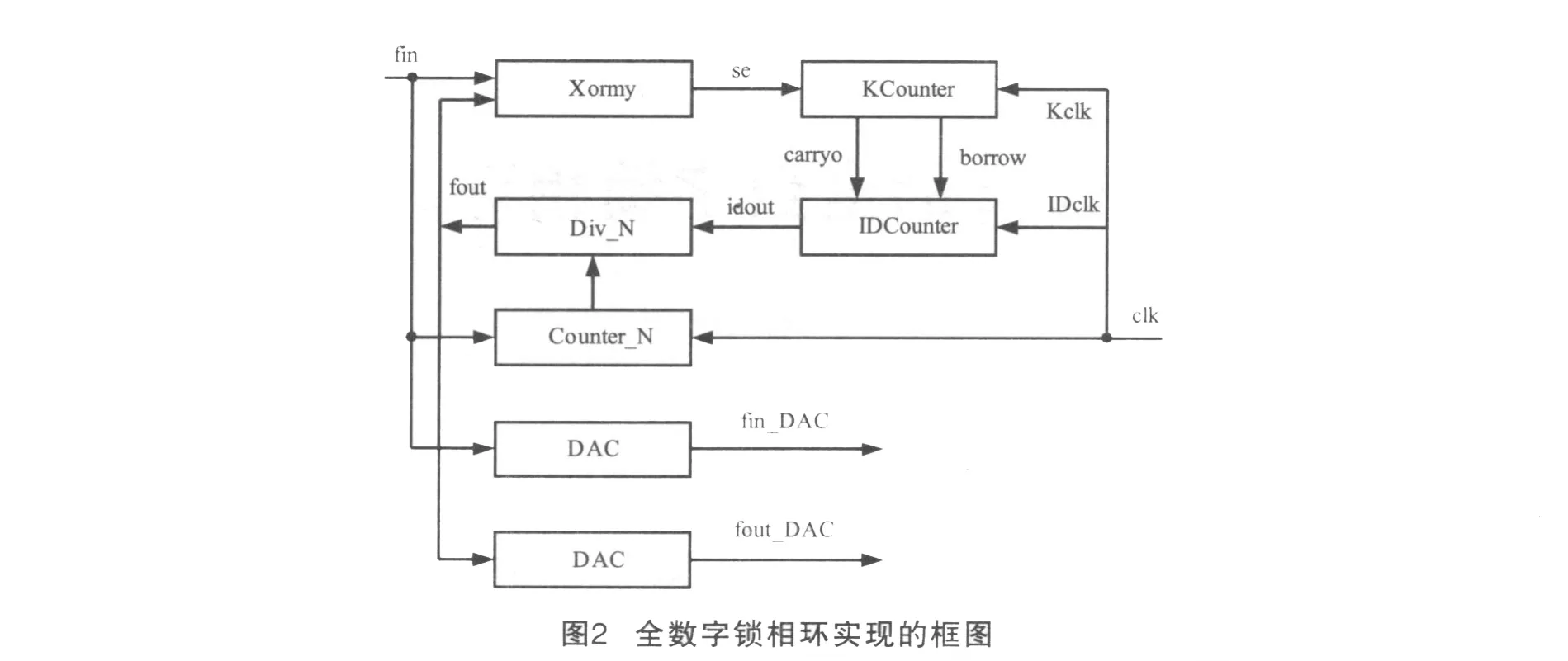

鉴相器采用异或门鉴相器,数字滤波器是一个模值可变的加减计数器,数控振荡器是一个脉冲加减模块,再用 N分频器 (div_N)对脉冲加减模块 ( IDCounter)的输出 idout分频,其中 N分频器的参数 N来自与N参数计数器(Counter_N),N参数计数器对输入信号给出相应的分频参数.

另外两个 DAC模块把输入信号 fin和输出信号 fout转换成模拟波形来观察验证.本次全数字锁相环的框图如下:

3 全数字锁相环的实现

(1)数字鉴相器的设计

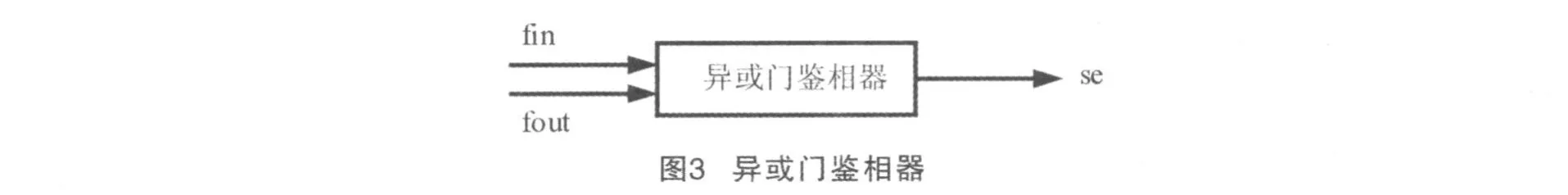

本设计选用异或门数字鉴相器.异或门数字鉴相器的主要任务是用来比较输入信号和输出信号之间的相位差Φse=Φfin-Φfout,并输出一个误差信号 se作为 K变模可逆计数器的计数方向控制信号.环路相位锁定时,误差信号 se是占空比为 50%的矩形波,此时的对应的相位差为π/2.下图为鉴相器模块.

(2)数字环路滤波器的设计

数字环路滤波器的主要作用是抑制噪声及高频分量,并且控制着环路相位校正的速度与精度.数字环路滤波器由变模可逆计数器 Q构成.在 ud的控制下,当 j=0时,Q对时钟进行“加”计数;当 j=1时,Q对时钟进行“减”计数.可逆计数器的模数 K可以通过 Ka、Kb、Kc、Kd四个输入端进行预置,当 Ka、Kb、Kc、Kd在 0001~1110取值时,相应模数 K的变化范围是 23~216.K变模可逆计数器的模值 K对全数字锁相环的性能指标有很大的影响.在初始时刻,计数器被置初值为 K=28,这样锁相环的捕捉速度较快.

(3)数控振荡器的设计

在全数字锁相环中,数控振荡器由脉冲加减电路实现,根据数字滤波器的给出的进位脉冲信号和借位脉冲信号进行输出脉冲的调整[2-3].当无进位/借位控制信号时,脉冲加减电路其实就是对外部时钟进行 2分频,当有进位控制信号时,则在输出信号中插入半个脉冲,以提高信号频率;当有借位控制信号输入时,则在输出信号中减去半个脉冲,以降低输出信号频率.经过这样不断的调整和跟踪,使输出信号最终锁定在输入信号的频率和相位上.

(4)N分频参数的设计

为了使锁定频率范围更宽,这里采用了动态N分频.原理就是对输入信号周期用高频时钟进行测量,得到高频时钟的长度之后再量化然后给出N值,N的值与高频时钟长度比例关系,高频时钟长度越长,N值越大.

(5)除N计数器的设计

N分频器的设计相对简单,其功能是将脉冲加减器输出的经过了调整的本地时钟进行 N分频,以减小同步脉冲输出误差,得到整个环路的输出信号 fout.

(6)全数字锁相环的顶层模块

全数字锁相环的顶层模块主要是把前面设计的几个模块连接起来[4].

全数字锁相环顶层模块端口设计如下:

4 全数字锁相环的时序仿真

采用QuartusII6.0软件进行时序仿真:

从时序仿真图可以看到,se在十个周期内输出方波,说明输出 fout的频率在几个输入 fin周期内可以跟上 fin的频率,这时的相位差为 90度.

5 结束语

本文介绍了一种利用 Verilog语言设计一阶全数字锁相环的方法,并在QuartusⅡ6.0软件环境下成功进行了时序仿真.该全数字锁相环具有电路结构简单、容易控制、环路性好等优点.本设计中变模可逆计数器的模值 K可以任意改变,用来控制DPLL的捕捉和锁定时间.除N计数器中分频器的分频值也可任意改变,用以跟踪不同输入频率的信号.

[1]胡春华,石玉.数字锁相环原理与应用[M].上海:上海科学技术出版社,1990.

[2]邵帅,李曼义,刘丹飞.全数字锁相环及其数控振荡器的 FPGA设计[J].现代电子技术,2008,31(10):1-6.

[3]黄智伟,王彦,陈琼,等.FPGA系统设计与实践[M].北京:电子工业出版社,2005.

[4]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[责任编辑 牛怀岗]

The Design of DPLL Based on Verilog

LIU Yong-qin

(Department of Physics and Electronic Engineering,Weinan TeachersUniversity,Weinan 714000,China)

In this paper,the basic structure and working principle ofADPLL are introduced firstly.Besides,the method of design ofADPLL based on verilog is put forward.At last,the design ofADPLL is timing simulated with QuartusII6.0 software.

DPLL;Verilog;FPGA

TP311.1

A

1009—5128(2010)05—0049—03

2010—06—30

刘永勤 (1981—),男,甘肃平凉人,渭南师范学院物理与电子工程系教师.研究方向:电路与系统.