通信分析仪中实时频率模板触发捕获技术研究

2010-06-20郭强胜秦开宇阎啸

郭强胜,秦开宇,阎啸

(电子科技大学空天科学技术研究院,四川成都 610054)

0 引言

本文介绍了一种基于Xilinx FPGA 的数字频率模板触发技术的算法实现,此设计可在无缝采集的同时进行实时同步FFT变换,即使在数据率最快的情况下也不会造成数据的丢失。同时可设置成在模板边界外面的信号“突入”边界时触发,也可设置成在模板边界内部的信号“突出”边界时触发。由于进行FFT变换是以帧为单位的,所以此时触发产生的时间分辨率为一帧的时间长度,即有效采样速率的1024个采样点时间。

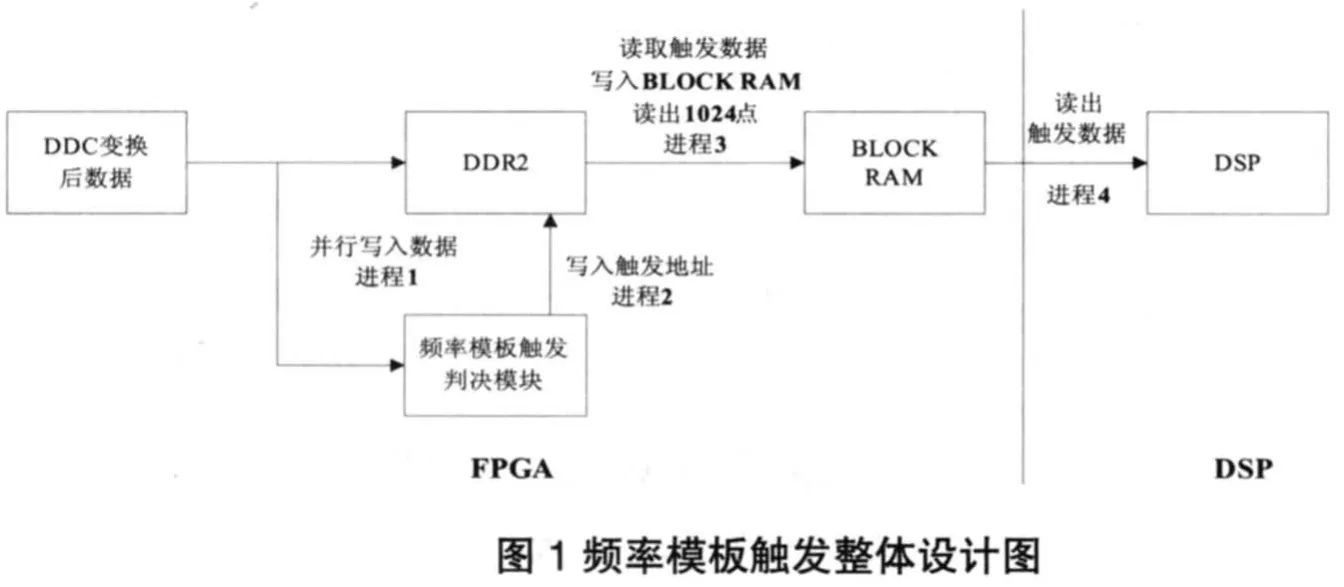

1 频率模板触发的整体设计

在通信分析仪中,数字下变频(DDC)后的数据同行送入内存管理模块和频率模板触发判决模块,在内存管理模块进行数据的无缝实时的存储,在频率模板触发判决模块内部进行快速的实时的FFT变换。如图1所示,在频率模板模块第一步进行无缝实时的FFT分析,第二步是将变换后的频域数据和频率触发模板做比较,当满足触发条件时,判决模块把送出触发信号和触发地址,频率模板触发也可设置触发延迟,根据触发延迟冻结存储器。然后在DSP的控制下,将读取数据分帧通过EMIF采用中断的方式送入DSP做后续处理。

2 频率模板触发的硬件结构设计

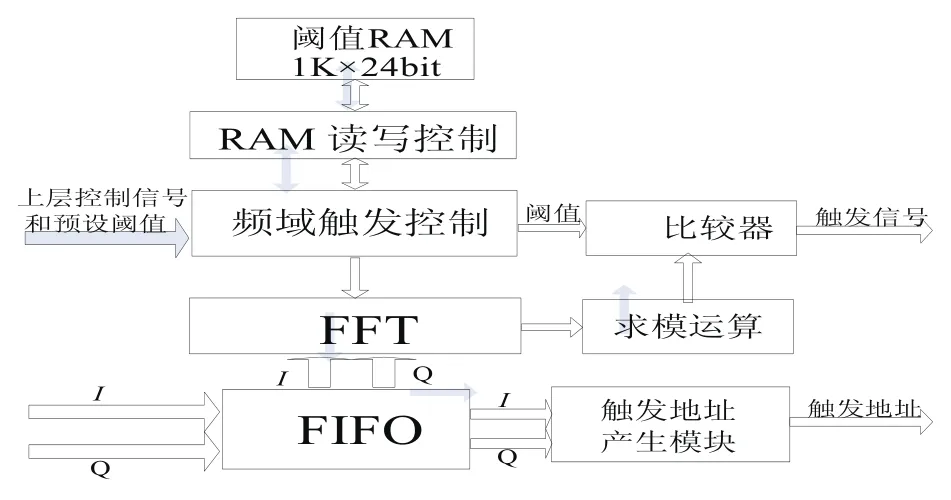

频率模板触发单元以数据帧为单位处理数字下变频器输出的两路基带正交信号。在把1024个I、Q数据对送入大容量的DDR2存储器的同时,也把基带正交信号送入容量大于4个1024点数据对的FIFO中,在DDR2内完成无缝采集,避免数据丢失。当FIFO内的数据个数大于1024时,就马上从FIFO中读出1024个I、Q数据对,通过FFT变换将其变化到频域。然后将1024个频谱数据与根据用户设置的频率模板产生的频谱阈值比较,当满足触发条件时从而产生触发信号,同时触发地址产生模块可产生满足触发条件时的触发地址。如图2所示,频率模板触发单元主要由硬件FFT变换器、FIFO、求模运算器、阈值RAM、RAM读写控制器、比较器、地址产生和频域触发控制几部分构成。

图2 频率模板触发单元功能框图

3 循环可变延时数据深存储机制

循环可变延时数据深存储机制在频域模板触发捕获中主要负责对基带I/Q信号数据的存储进行管理,保证触发时刻和触发前后的信号时域数据能够可靠存储并用于后续高精度信号分析。

当频率模板定义后,模板触发算法连续检测DDC输出正交基带I/Q信号特征变化。同时,时域基带I/Q信号在循环可变延时数据深存储机制的管理下,循环存入由外部高速存储器构建的大容量DDR2存储器中。在满足触发条件时,存储机制冻结DDR2中的内容,不再接收或清除任何数据。后级信号处理单元从DDR2中读出缓存的时域基带I/Q信号用于后级信号实时多域分析。

为达到能够捕获触发前和触发后发生的事件的目的,在触发数据存储机制中增加了可变触发延迟。触发延时P定义了触发事件对应基带I/Q信号样值在DDR2中存储的相对位置,它表示预触发数据在整个存储器中缓存信号数据所占的百分比。当没有延迟时,触发事件导致存储器立即冻结,此时存储器中包含触发时刻的基带I/Q信号样值和触发前采集的共N个样点,即只存储触发前的事件;当触发延迟设置为与存储器长度相同时,在触发事件发生后的N个基带I/Q信号样值将进入存储器,然后存储器冻结,即此时存储器中仅存储触发后的事件;当触发延迟设置为内存长度的50%时,那么存储器中一半基带I/Q信号样值是触发之前的样点,一半是触发之后的样点。

通过对大容量高速存储器的地址管理,来构建实时多域联合触发捕获中的DDR2存储器。DDR2数据存储示意图如图3所示。

图3 DDR2数据存储示意图

假设DDR2存储器能够存储M帧时域基带I/Q信号样值。触发延时P定义了存储在存储器中的数据帧有M*P%是触发前的数据帧, (1-P%)*M是触发后的数据帧。地址计数器在实时多域联合触发检测启动时清零,并对写入FIFO中的基带I/Q信号样值进行地址计数。当触发信号有效时,计数器的当前计数值为C。存储器地址由存储容量M、触发延时P和地址计数值C共同决定。在实时多域触发信号有效时,数据存储及地址产生机制如下:

(1) 当P>(C/M)*100%时,则基带I/Q信号样点继续存入DDR2中,地址计数器从C开始继续计数直至计满,即计至M。冻结存储器内数据。

(2) 当P<(C/M)*100%时,则将地址计数器计数值强制设为M*P,基带I/Q信号样点继续存入DDR2中,地址计数直至计至M。冻结存储器内数据。

(3) 如果P=100%,即保留触发前的数据帧。地址计数和存储机制与1相同。

(4) 如果P=0,即保留触发后的数据帧。这种情况直接将地址计数器清零,基带I/Q信号样点继续存入DDR2中,然后地址计数器计满即可。

4 硬件结构设计实现

4.1 FFT实时变换

(1)FFT核介绍

FFT COKE 接口定义如表1所示。

表1 FFT CORE接口定义表

XN_RE输入为24 bits的I路信号,XN_IM输入对于24 bits的Q路信号;在流水I/O 模式下,START信号在拉高后3周期,FFT CORE开始接受I/Q数据,频率模板触发的FFT运算过程开始;UNLOAD信号用于在突发I/O模式下的按正常顺序输出数据,在流水I/O 模式下该信号不是必须,在设计中未使用;NFFT用于在线配置FFT的转换长度,在设计中由于FFT转换长度固定为1024,没有使用该信号;NFFT_WE是NFFT的写使能信号,在设计中未使用;FWD_INV是用于指示FFT CORE工作于快速傅立叶变换或者快速傅立叶变换的反变换模式,FWD_INV为1时FFT CORE工作于快速傅立叶变换模式,FWD_INV为0时FFT CORE工作于快速傅立叶变换的反变换模式,FWD_INV_WE为FWD_INV的写使能信号,高有效;SCALE_SCH为FFT CORE的压缩因子,在流水I/O模式下转换长度为1024时,其数据宽度为10 bits,为避免产生数据溢出,在频率模板触发设计中将其设置为10’b1010101010,相当于将计算结果除以1024;SCLR为异步复位信号在FFT CORE初始化的时候使用;CE为时钟有效信号;CLK为FFT CORE的输入时钟;XK_RE为经过FFT变换后输出数据实部,由于采用了固定值压缩模式,数据位宽和输入数据位宽相同为24 bits;XK_IM为经过FFT变换后输出数据的虚部,数据位宽也是24 bits;XN_INDEX是输入数据的索引,表示输入数据在其帧中的次序,其数据宽度为10 bits;XK_INDEX是输出数据的索引,表示输出数据在其帧中的次序,其数据宽度为10 bits;RFD指示FFT CORE的数据输出状态,在输出经过FFT变换后的数据时为高;BUSY指示FFT CORE的工作状态,在FFT CORE正在计算时为高;DV表示输出数据有效;EDONE表示FFT变换即将处理完成,在DONE信号前一个周期;DONE表示FFT变换完成,DONE将会在FFT变换完成后变高一个周期;BLK_EXP表示每个数据的压缩量,在设计中未使用;OVFLO是溢出指示信号,在FFT CORE计算发生溢出时为高。

(2)FFT核测试验证

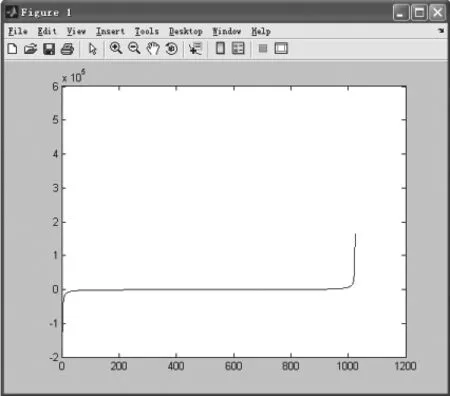

FFT测试向量采用累加形式,这种测试向量最易生成,在MATLAB编程验证中也相对易于实现,其快速傅立叶变换后结果的最大值出现在输出第一个数据,利于检查时序。

(a) 数据输入:数据实部为0-1023,虚部为1-1024;

(b) MATLAB实部仿真程序:

a=0:1:1023;b=1:1:1024;X=a+b*i;Y=fft(X,1024);y r=real(X);yi=imag(X);t=1:1:1024;plot(t,yr);仿真结果如图4所示。

图4 MATLAB验证FFT运算实部仿真图

图5 MATLAB验证FFT运算虚部仿真图

(c) MATLAB虚部仿真程序:

a=0:1:1023;b=1:1:1024;X=a+b*i;Y=fft(X,1024);y r=real(X);yi=imag(X);t=1:1:1024;plot(t,yi);仿真结果如图5所示。

(d) Modelsim 检验

在程序设计中,由于输入数据是24bit,转换长度为1024,在不压缩的情况下输出数据为35bits。在设计中采用的压缩因子为10'b1010101010,相当于除以1024。FFT CORE运算Modelsim仿真结果如图6所示。

图6 Modelsim验证FFT CORE仿真图1

图6显示了经过FFT变换后的初始段数据,由计算可知FFT变换的第一位是实部数据累加和,为(0+1023)×1024/2=523776,除以1024结果为511,和仿真结果一致,虚部数据位(1+1024)×1024/2=524800,除以1024结果为512。第二位数据由Matlab仿真数据可以看出实部数据为 ,除以1024为-165,这和Modelsim仿真的FFT CORE运算结果完全一致,同时注意到DONE信号为高后一个周期数据经过FFT变换后的数据开始输出,这为以后的频率模板触发判决模块设计提供了很大的方便。

图7显示了经过FFT变换后的末尾段数据,末尾数据除了最后几位外其余都接近于0,由计算可知FFT变换的最后一位实部数据为 ,除以1024为162,虚部最后一位数据为 ,除以1024后得164,这和Modelsim仿真的FFT CORE运算结果完全一致。另外可以发现在本帧数据计算完全后,FFT CORE立即输出了下一帧运算结果,这样完全可以满足频率模板触发所需要的实时性。

图7 Modelsim验证FFT CORE仿真图2

4.2 频率模板触发判决模块

在FFT CORE完成运算后,结果分为实部和虚部两路输出,但是频率模板触发判决门限设计上只是关心其幅度信息。因此在和触发门限比较前需要将实部和虚部数据做平方和然后再开方的处理,然后与从上层发下来的频率模板进行比较判决。

频率模板触发判决状态机设计如下:

系统重新发送命令和数据完成复位后进入状态0;

状态0:触发有效信号和触发地址清0,进入状态1;

状态1:IQ数据无缝连续的输入到FFT单元,在fft_done信号有效的情况下跳入状态2,否则等待;

状态2:表示本帧的第1位到第1023位数据经过快速傅立叶变换后的幅度值的判决过程,都是将其幅度值和对应的频率模板触发门限作比较,如果相邻的两次比较值是异号,进入状态3,否则进入状态1继续等待下一帧比较;

状态3:表示本帧的满足出发的条件,锁存次帧所对应的地址并同时发出触发完成信号。进入状态4;

状态4:根据触发条件满足时的内存写入地址和频率模板触发控制帧送入的频率模板触发前读取帧数和频率模板触发后读取帧数计算出需要读取初始读地址和末尾读地址,同时停止快速傅立叶变换以节省系统资源,进入状态5;

状态5:等待内存写入地址为频率模板触发末地址,此时内存已经采集完毕,触发写已完成,内存由写状态切换到读状态。

4.3 触发地址产生模块

数字下变频(DDC)后的数据源源不断的同步送入内存和FFT模块。图8所示,在FFT模块中,每完成一帧1024点变换后就会产生fft_done信号。因为频率模板触发的地址分辨率单位是帧。触发地址产生模块利用这跟信号线,每次在其上升沿触发的地址就累加1024作为此时的地址,直到产生触发完成信号就锁存此时的地址。

图8 触发地址产生仿真图

4.4 触发比较器模块

当频率模板已经设置好了以后,把FFT产生的数据进行求模运算后与模板进行比较。在比较的时候,本论文的特点是突入和突出模板都可以触发采集,所以需要两个比较器,在相邻两个比较值为异号的时候触发采集,同时送出触发信号的此时的触发地址。如图9所示,fft_Subtracter_P_OUT_1和fft_Subtracter_P_OUT_2为异号的时候,满足触发条件。该触发判决比较器是本文的一个创新点,可以同时完成同时完成“突入”和“突出”触发,而不需要从上层软件再此下发命令来区别两种触发。

图9 频率模板触发完成信号仿真图

5 频率模版触发整体模块验证

在本文的验证中,采用频率模板触发方式对含有同频干扰的QPSK调制跳频信号进行触发捕获。其中,QPSK信号中心频率为1.5GHz,信号码率500KHz,幅度为-30dBm,跳频频率间隔为2.5MHz,跳频驻留时间为375us。设置中心频率设置为908MHz,实时分析带宽为20MHz。在实时频谱分析模式下,被测信号光谱图如图10(a)所示。从频谱图中可以看到被测信号在实时分析带宽内连续跳变,而同频干扰的存在难以识别和精细分析被测信号。采用时间-频率模板触发模式对跳频频点为1.495GHz和1.505GHz的被测QPSK跳频信号进行触发捕获,结果如图10(b)所示。从图中可以看出,只有落入频域模板以外并满足触发间隔的对应跳频频点的信号被捕获。从而验证了该实现方法的正确性。

图10 采用频率模板触发方式对QPSK跳频信号触发捕获实测图

[1]樊光辉,许茹,王德清.基于FPGA的高速流水线FFT算法实现[J].电子工程师,2008, 34(3):40.

[2]Rong Yu, Zhu En. Design of high-performance FFT butterfly unit[J].JOURNAL OF SOUTHEAST UNIVERSITY (Natural Science Edition), 2007,37(4).

[3]刘祖深. 频谱分析仪全数字中频设计研究与实现[J].电子测量与仪器学报, 2009(23):39-44.

[4]秦开宇,周琳,王天平,吴绍炜. VXI射频实时频谱分析仪模块数字中频技术研究[J].仪器仪表学报,2005(1):17-22.

[5]史兴海, 陈殿仁, 赵爽, 富强, 王大宇.基于FPGA的高速DDS设计与仿真[J].长春理工大学学报,2009, 32: 85-87.

[6]谭磊,陈文正。高速定点快速傅立叶变换处理器的设计与实现[J].浙江大学学报:工学版,2005(3).

[7]钱永.实时频谱仪原理及应用案例集汇编[M].Tektronix Inc., 2007.

[8]程佩青.数字信号处理教程 [M].2版. 北京:清华大学出版社,2003.