基于Logistic映射的混沌跳频信号发生器设计与实现*

2010-05-18禹思敏

李 伟,禹思敏

(广东工业大学 自动化学院,广东 广州 510006)

跳频通信系统以其抗干扰能力强、组网灵活等优点,在军事与民用通信领域得到了广泛的应用[1]。跳频图案的选择是跳频通信技术的核心。现有跳频序列(如m序列、RS码序列等)均存在复杂度低、保密性较差等缺点[2]。

混沌序列以其对初始条件敏感性、类随机性、宽带谱和冲击式的相关特性等特点,在扩频通信系统中展现出良好的应用前景[3]。但纯粹的混沌序列作为跳频序列过于单一。为提高混沌跳频系统跳频图案的复杂度,可将数字混沌序列的当前时刻值与前两时刻的值进行逻辑运算来产生1个新的序列,并通过m序列的值来控制运算关系和前2个时刻值的系数,从而生成一种复杂度更高的用于混沌扩频的数字序列。利用MCS-51单片机作为跳频图案的生成平台以及锁相环电路构成频率合成器,实现了跳速 1 000跳/s、频点数为 256、频率范围在15 MHz~17.5 MHz的混沌跳频信号发生器,实验结果证实了这一方法的可行性。

1 Logistic映射

已知Logistic映射的迭代方程为

概率密度函数为[4]

其自相关函数为

其互相关函数为

根据上述式(3)和式(3)得出Logistic映射的自相关和互相关特性,如图1所示。

图1 Logistic-Map的相关特性

2 混沌跳频序列的产生

在Logistic映射的基础上,将当前时刻Logistic映射混沌序列的值x(i)与前2个时刻的值 x(i-1)、x(i-2)通过逻辑运算f(*)后,得到1个新的伪随机序列{FH(i)},作为系统的跳频图案。其数学表达式为:

其中运算关系f(*)及 m1、m2由 m序列来确定。

本文选用1个r=5 的 m 序列 M(i)=[m0,m1,m2,m3,m4],由此确定时刻 x(i)与 x(i-1)和 x(i-2)的运算关系,如表1所示。

表1 逻辑运算关系判定表

m序列的m1和m2位的值则分别作为前2个时刻值的系数,而m0位仅在构成移位寄存器时有用,如表2所示。

表2 m序列值与FH(i)的关系

采用r=5的1个本原多项式(45)8构成m序列[5]。本原多项式的数学表达式为:

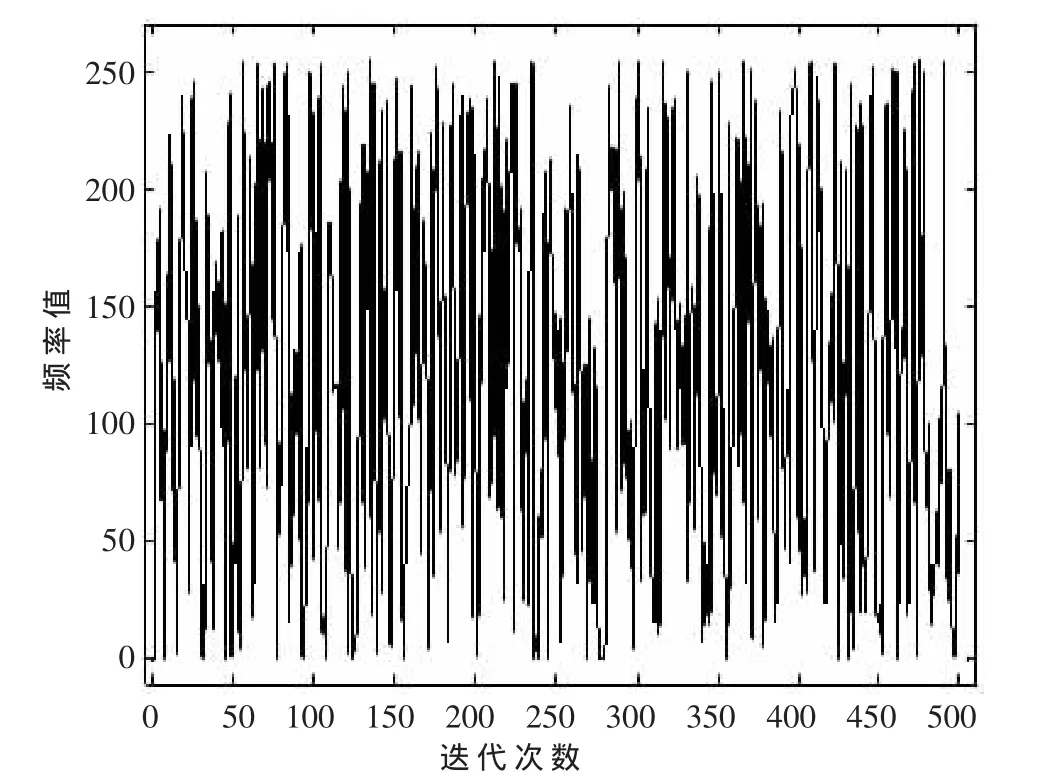

根据表2中的对应关系,可利用m序列和Logistic-Map数字混沌序列产生1个新的更为复杂的序列{FH(i)},其时域波形图如图2所示。

图2 序列{FH(i)}的时域图

由于序列{FH(i)}是由Logistic映射混沌序列的当前值与前2个时刻的值通过逻辑运算得到的,通过这种方法可增加序列的复杂度,但其自相关和互相关性能略有下降,如图3所示。

3 跳频信号发生器的硬件实现

本文采用MCS-51系列单片机硬件平台作为跳频图案的发生平台,所产生的跳频序列值作为分频比控制频率合成器的输出频率,系统的整体硬件原理图如图4所示。下面针对图4中所示的跳频信号发生器硬件部分进行具体的分析与设计。

图3 序列{FH(i)}的相关特性

跳频信号发生器需要较高的频率跳变速率,这就要求系统产生跳频序列的速度尽可能快。考虑到产生跳频序列的程序大小,单片机可通过单片运行的方式工作,并选用最高工作频率33 MHz。

通过单片机迭代计算的混沌序列值以BCD码的形式送入可编程分频器芯片TC9198P,作为频率合成器的分频比(N)。当 MODE值取“L”时为双计数器模式,0~6位吞吐计数,7~17位可编程计数;当 MODE值为“H”、D17值为“L”时,0~15位进入二进制可编程计数模式。当MODE与D17值同为“H”时,芯片处于BCD码型可编程模式。MODE引脚的值为“H”时,D16引脚无效。这里采用BCD码型可编程模式,将MODE、D17引脚置为高电平。

跳频系统要求频点数为256,相邻频点的步进值为10 kHz。可将标称值为10.24 MHz的晶振频率通过4 060芯片1 024分频后,作为频率合成器的基准频率。

锁相环芯片74HC4046作为频率合成器的核心部件,集成了鉴相器和压控振荡器,其工作频率可达30 MHz左右。

74HC4046中有3种类型的相位比较器:XOR型、JK触发型和PFD型。跳频信号发生器系统要求的频率变化范围较宽,XOR型和JK触发型鉴相器难以满足大范围的频率捕捉、锁定的要求。PFD鉴相器能达到无限捕捉范围,完全可以满足系统的要求。

混沌跳频信号发生器的工作频率范围是15 MHz~17.5 MHz。R1与R2的值共同决定锁相环的有效工作范围,在保证(R2/R1)的值大于10的条件下,选取R1=7.6 kΩ,R2=100 kΩ。锁相环的中心频率(ω0)和压控振荡器的中心频率均可选为17 MHz左右。电容C1的值决定压控振荡器的中心频率(自由振荡频率),可确定为50 pF左右。

图4 跳频信号发生器的硬件原理图

线性低通滤波器在整个环路中的作用非常重要,它直接影响这个锁相环路的阻尼因子(ξ)、自然频率(ωn)、捕捉时间(Tp)、锁定时间(TL)和锁定范围(ΔωL)等因素。根据系统要求,选用无源超前滞后滤波器。

[6]可知,锁相环路系统参数如本征频率、阻尼因子、捕捉时间、锁定时间和锁定范围可由下式确定:

式(7)中,UB为电源电压,K0为压控振荡器增益,Kd为鉴相器增益,Δω0为初始频偏,τ1=R3C,τ2=R4C。当锁相环用做频率合成器时,由于要求大范围的快速锁定,必然会降低输出频率的准确度。经综合考虑,这里参数选为:τ1=5×10-6,τ2=5×10-4。

4 跳频图案产生单元的软件设计

跳频图案的产生过程可大致分割为几个模块,如图5所示。

在Logistic映射方程中,参与运算的均为(0,1)之间的小数,而单片机并不适于处理浮点数,因此,可以通过线性映射 X(n)=65 536×x(n)将(1)式化为如下形式:

通过变换,Logistic映射方程的值域变为(0,65 535)。为加快程序运行速度,可通过按位逻辑运算替代乘、除运算,根据式(8)迭代计算出Logistic映射序列的值。

图5 跳频图案产生过程模块图

依据式(5)所示逻辑关系生成m序列,查表2确定运算关系f(*)和系数 m1、m2。同理,通过数字混沌序列当前值与其前2个时刻的值进行相关性运算,得跳频序列{FH(i)}的值。

跳频系统的频点数为256,为1个8位二进制数的表数范围,故将前面算得的序列值的低8位取出,作为跳频频率控制码。由于可编程分频器处于BCD码型可编程计数状态,故要将取出的8位二进制数转换成BCD码的形式。

由于系统的输出频率范围是 15 MHz~17.5 MHz,故在输出之前要将原来的序列值以BCD码的形式加上1 500。

图6 单片机主程序流程图

单片机送出跳频序列值的时间间隔Δt要大于锁相环的最大锁定时间TLmax,才不会造成因为数据传输过快,而锁相环未及时锁定所带来的较大频率误差。比较Δt和TLmax的值可知,在计算出FH值并将其送出后要进行一定时间的延时。

混沌跳频信号发生器系统的单片机软件的总体流程如图6所示,其中判断运算关系及确定运算系数的具体流程如图7所示。

图7 运算关系f(*)及系数的判定过程

在跳频系统中,仅单独选用混沌数字序列作为跳频图案的复杂度不高。本文在Logistic混沌映射的基础上,通过数字混沌序列当前值与前2个时刻值的逻辑运算,并由m序列控制其运算关系及系数,可产生1个复杂度更高的新的序列作为系统的跳频图案。在混沌跳频器的设计与技术实现方面,利用MCS-51单片机作为跳频图案的生成平台以及锁相环电路构成频率合成器,实现了跳速 1 000跳/s、频点数为 256、频率范围在 15 MHz~17.5 MHz的混沌跳频信号发生器,实验结果证实了这一方法的可行性。

参考文献

[1]李文化,王智顺,何振亚.用于跳频多址通信的混沌跳频码[J].通信学报,1996,17(6):17-21.

[2]凌聪,孙松庚.Logistic映射跳频序列[J].电子学报,1997,25(10):79-81.

[3]孙剑,罗汉文,宋文涛.有限精度混沌映射跳频多址序列[J].通信技术,2000(1):32-34.

[4]王亥,胡健栋.Logistic-Map混沌扩频序列[J].电子学报,1997,25(1):19-23.

[5]田日才.扩频通信[M].北京:清华大学出版社,2007:67-84.

[6]ROLAND E B.锁相环设计、仿真与应用[M].北京:清华大学出版社,2007.