基于FPGA的中频采集系统设计

2010-04-26黄建国

姜 磊,黄建国,李 力

(电子科技大学自动化工程学院,四川 成都 611731)

1 引 言

目前,数据采集系统大多采用DSP作为核心控制芯片,控制ADC、存储器和其他外围电路工作。但是DSP的各种功能要靠软件的运行来实现,执行的速度和效率较低,软件运行时间在整个采样时间中占很大的比例。而FPGA(现场可编程门阵列)有着DSP无法比拟的优势。FPGA时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高。该文设计了一种基于FPGA的中频数据采集系统,实现了FPGA内部逻辑设计在中频采集系统中的应用。

2 中频采集系统硬件设计

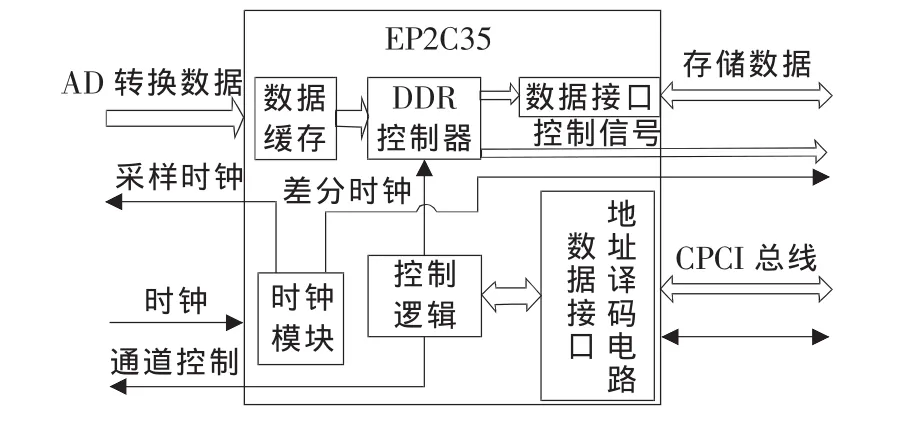

该中频采集系统用于对前端下变频模块输出的中频调制信号进行高速数据采集,同时实现数据的总线上传,即将数据通过CPCI总线上传给计算机进行数据处理与分析。其硬件系统构成主要包括信号调理通道、模数转换电路、FPGA控制电路、存储电路、CPCI接口电路、晶振电路以及电源管理电路等。控制计算机通过CPCI总线与FPGA进行通信,将控制命令发送给FPGA。FPGA的译码控制逻辑收到传来的数据后,读取控制数据,以确定要执行的操作,如信号衰减、信号放大、开始采集等。在FPGA内部逻辑的控制下,数据存入存储器,并通过总线送到上位机待分析处理。系统硬件结构如图1所示。

该中频采集系统采用FPGA作为整个系统的控制核心。CycloneII EP2C35F672I8是Altera公司生产的一款具有较高性价比的FPGA芯片,它采用Stratix架构,使用90 nm工艺生产,具有33216个LE,105个M4K单元,4个PLL以及14DQS/DQ8模块。另外,其I/O管脚可以直接与系统中使用的其他芯片相连而不需要进行电平转换。该款FPGA的内部资源以及管脚数量能够完全满足此案的设计需求,故选用该款FPGA作为主控逻辑芯片。

信号调理通道可以实现对信号10 dB、20 dB的衰减和10倍放大,可通过FPGA进行控制,将信号调理在ADC转换的电压范围内。ADC选用ADI公司推出的高速、低功耗的AD9430,采样时钟最高可达210MHz,分辨率12位,支持差分输入电压,范围为-768~+768 mV。存储器采用了Micron公司的DDR SDRAM芯片MT46V32M16。MT46V32M16为16位数据宽度,存储容量为512 Mb,差分时钟输入,突发传输长度可配置为2,4,8,最低工作频率为75MHz。CPCI接口芯片选用PCI9054。

图1 中频采集系统硬件结构示意图

3 中频采集系统逻辑设计

3.1 总体逻辑设计

作为整个系统的控制核心,FPGA起着前端通道控制、数据缓存、数据存储控制、总线接口控制的作用。FPGA通过CPCI总线接口接收来自上位机发送的命令,控制前端信号调理通道,使信号调整在ADC检测的范围内。上位机发送开始采集的命令后,FPGA开始将ADC采集到的数据读入内部,但是由于前端ADC输出的数据流为200MB/s的12位数据,这与后端的DDR SDRAM存储器240 MB/s的存储速率不匹配,不能直接存储,所以先将数据在FPGA内部FIFO中做缓存,同时内部的DDR SDRAM控制模块将缓存的数据存入外部DDR SDRAM中,一共存储64MB不间断的数据。当外部存储器存满后,将发送满信号给上位机,告知上位机数据可以读取。这时,上位机就会发送读数据命令。同样,存储器读数据的速率与CPCI总线40 MHz传输的速率不匹配,FPGA也将存储器中的数据分若干次读进内部的缓存FIFO中,每次FIFO写满后发中断给上位机,上位机接收到中断后就使用DMA方式将数据从FPGA缓存FIFO中读出数据,直到将存储器中的数据读完为止,整个数据采集过程结束。FPGA内部总体逻辑示意图如图2所示。

3.2 译码及控制逻辑

上位机对硬件电路的操作都是通过对PCI9054进行地址译码实现的,所以首先要分配地址空间,以区分对硬件中不同功能电路的操作。操作人员通过上位机把相应的操作命令发下来,经过PCI9054桥接芯片后送给FPGA内部的地址译码电路,地址译码电路将相应的操作命令转换为对应的控制信号送给相应的功能电路,实现对模块的控制。设计中利用可编程逻辑器件实现地址译码电路的设计。

3.3 数据缓存

数据缓存是数据流处理上一个关键的部分,是实现数据流无缝存储的前提。由于前端ADC采集速率达200MHz,存储器不能实时将数据存储,需将数据先做缓存处理。该采集系统的数据缓存采用“乒乓操作”。乒乓操作是在输入数据流选择单元和输出数据流选择单元按节拍相互配合切换,将经过缓冲的数据流没有时间停顿地送到运算处理单元,进行运算和处理。把乒乓操作模块当作一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。

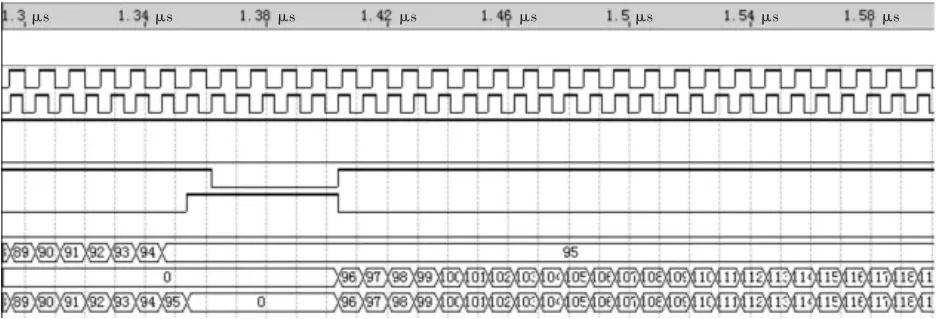

该设计中采用异步FIFO作为数据缓存单元,来匹配乒乓操作前后端数据流速率不同的问题。如图3所示,实际电路中将前端ADC采集的200MHz的数据流,降频为两个100MHz的数据流,每个100MHz的数据流需要两个FIFO进行乒乓操作,故电路中需要4个异步FIFO进行乒乓操作,其中每个FIFO的大小设置为4K×12bit。调试中需要注意的是数据的切换及衔接问题,保证数据流的连续性。乒乓操作仿真波形图如图4所示。其中为了仿真方便,异步FIFO的大小设置为32×12 bit,数据经过乒乓操作缓冲后输出是连续的。

图2 FPGA逻辑示意图

图3 乒乓操作示意图

图4 乒乓操作时序仿真波形图

3.4 数据存储

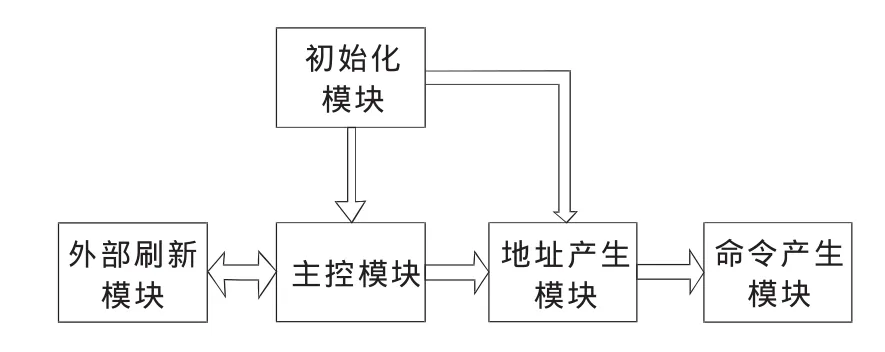

数据存储是该设计的重点和难点,也是数据采集的核心部分,FPGA逻辑实现主要由DDR SDRAM控制器和接口模块组成。DDR SDRAM控制器的功能是根据DDR SDRAM的工作原理,控制DDR SDRAM正确的工作,将前端AD采集的数据正确的存入DDR SDRAM中,并能够正确的读入上位机进行分析。存储器控制模块主要包括初始化模块、外部刷新模块、主控制模块、地址产生模块及命令产生模块5个部分。其结构框图如图5所示。

图5 DDR SDRAM控制器组成框图

初始化操作主要确定DDR SDRAM的CAS潜伏期(CL)、突发传输模式、突发长度(BL)等。刷新模块根据DDR SDRAM工作时钟为120 MHz的情况设计为两种刷新模式,一种是空闲状态的短刷新,刷新时间83μs;另一种为读写满4行的长刷新,刷新时间为333μs。这样的设计完全满足DDR SDRAM手册规定的64ms对所有行刷新一次的要求。主控模块主要完成DDR SDRAM的读写控制。在对DDR SDRAM进行读写操作之前,都要经过激活状态,然后经过所要求的时间延迟后转入写或者读的状态,当一行读写完毕后,进入预充电状态。如果没有完成预设的读写深度,则再度重复进入激活状态,打开下一行,重复这一过程;如果达到了预设的读写深度,则转入长刷新状态,刷新结束后,如果外部有读写请求,就转入激活状态,重复上面的过程。所不同的是,在对DDR SDRAM进行写操作时,写深度为4行,即写满4行后进行一次长刷新;对DDR SDRAM进行读操作时,读深度为2行。

Altera公司的FPGA内部有专门的DDR SDRAM接口电路,并且其开发工具QuartusII软件也提供了宏功能模块alt_dq和alt_dqs,用户只需要正确的设置参数,就可以生成所需要的接口模块,并且可以更好地满足DDR SDRAM的时序要求。

3.5 总线传输

数据及控制信号通过CPCI总线与上位机进行连接。其中控制信号与数据的传输方式有所不同,控制信号使用CPCI总线的单次写方式,而采集数据由于数据量较大,不能采用单次读的方式,需要使用CPCI总线的DMA数据传输模式。进行DMA数据模式传输是PCI9054的一大特点。DMA是Direct Memory Access(直接内存访问)的缩写,是一种不通过CPU而直接从内存进行数据传输的数据交换模式,可以大大节省系统资源。

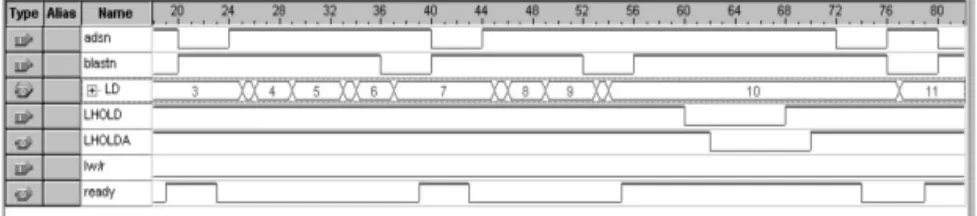

图6 DMA传输时序图

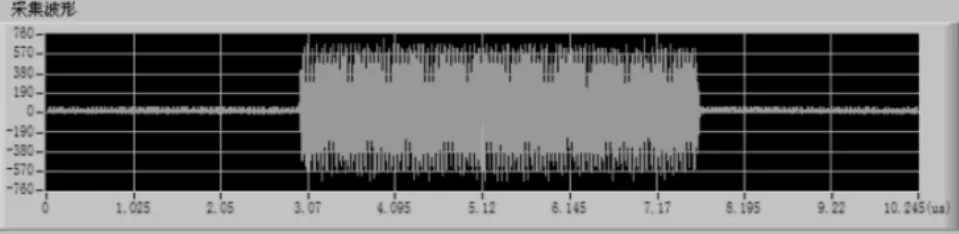

图7 数据采集波形

图8 中频信号解调结果

当数据写满外部DDR SDRAM存储器后,数据状态寄存器置1,通知上位机数据已准备好,可以读取上位机则发出读命令给DDR SDRAM控制器。DDR SDRAM控制器接收到读命令后,从DDR SDRAM存储器中读取数据写到FPGA内部的缓存FIFO中,缓存FIFO大小设置为1K×32bit。待缓存FIFO写满后发出中断给上位机,上位机接收到FIFO的满中断就开始以DMA数据传输模式传输数据,DMA设置传输数据大小为1K×32bit,由于是对FIFO操作,可以忽略地址信号。当数据传输完毕时,停止DMA传输,DDR SDRAM控制器检测到FIFO空信号后又继续从DDR SDRAM存储器中再读取1K×32bit的数据存入FIFO,重复之前的操作,直到将存储器中64M×8bit的数据全部读完,上位机停止读数据的操作。图6为使用QuartusII中SignalTapII工具采集的DMA传输时序图。

4 实验分析

在实际的实验中,输入信号使用Agilent的E4438C矢量信号源模拟60 MHz的中频调制信号,调制方式为 ASK 方式,脉宽为 4 μs,周期为 20 μs,信号功率为10 dB。上层软件设置前端固定衰减10 dB,然后发出采集命令。待底层硬件采集完成后,上层软件自动将数据通过CPCI总线读入计算机的内存中并进行显示与分析。图7是通过上层软件显示的采集到的ASK调制信号波形结果。图8是上层软件使用采集数据对中频信号解调的结果。实验结果说明,该系统较好地完成了大容量中频数据采集的功能,可以满足上层软件分析的需要。

5 结束语

该设计以一片Alatra公司的FPGA芯片EP2C35F672I8为核心,配以外围的信号调理电路、模数转换电路、存储电路、CPCI接口电路,实现了中频调制信号的数据采集及存储,并完成了与上位计算机的通信。该系统控制逻辑全部在一片FPGA芯片内部实现的,发挥了FPGA的优势,提高了系统的稳定性、集成度,增强了抗干扰能力。利用多片ADC器件流水采样的方法,完全可以实现更高速更大容量信号的数据采集,这在高速大容量数据处理中具有较大的实用价值。

[1] 冯 萍,李秀华.基于FPGA的高速高精度数据采集系统的研究[J].中国科技信息,2008(21):105-106.

[2] 张会新,吴学庆,蒋绍凤,等.基于FPGA的多通道同步数据采集存储系统[J].电子设计工程,2009,17(7):68-70.

[3] 王 超.FPGA在实时信号采集系统中的应用[J].计量与测试技术,2008,35(5):47-49.

[4]王 钿,卓兴旺.基于Verilog HDL的数字系统应用设计[M].北京:国防工业出版社,2006.

[5] 吴继华,王 诚.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005.

[6] 吴继华,王 诚.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005.

[7] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[8] 林 生,金京林.数字设计原理与实践[M].北京:机械工业出版社,2003.

[9]李广军,林水生.微机系统原理与接口技术[M].成都:成都电子科技大学出版社,2005.

[10]马明建.数据采集与处理技术[M].西安:西安交通大学出版社,2006.