TOF测量系统读出电子学时钟插件设计

2010-03-24尹春艳周家稳杜中伟刘树彬

尹春艳 安 琪 周家稳 杜中伟 刘树彬

(中国科学院核探测技术与核电子学重点实验室,物理电子学安徽省重点实验室,中国科学技术大学近代物理系 合肥 230026)

粒子物理研究中,飞行时间(TOF)测量是鉴别粒子的重要方法,目前已达到ps量级的测量精度。在大型物理实验装置中,如中国 BEPC II的 BES III[1]、美国BNL的STAR[2]、欧洲核子中心LHC的ALICE[3],TOF探测器读出电子学的核心都是基于HPTDC(High Performance Time-to-Digital Converter)的时间测量,精度达到25 ps。读出电子学系统的时钟插件能协调系统各部分工作,是电子学系统的基准信号,影响整个TOF读出电子学系统的工作和性能。

系统时钟性能的评价,以信号完整性理论为基础,以时钟抖动[4,5]和时钟偏差为性能评价指标。日本KEKB的Belle探测器,用频率为508 MHz的射频模块产生系统时钟,周期为16 ns,抖动<20 ps[6];上海光源(SSRF)的时钟系统、光纤系统和束流脉冲系统则要求总时钟抖动<100 ps[7];北京 BESIII的TOF电子学系统,要求输入HPTDC的时钟信号抖动<20 ps[8]。由此可见,读出电子学系统的高性能运行对时钟系统时钟信号的精度要求之高。

中国科学院近代物理研究所在 ECR离子源原子物理束流线上,用反应显微成像谱仪研究离子与原子分子碰撞,产物粒子与附近三块靶发生撞击,测量碰撞过程中的粒子飞行时间。重离子加速器冷却储存环(HIRFL-CSR)CSRm内靶实验中,用重离子束流进行强子物理研究,测量多丝漂移室、飞行时间墙和中子墙处粒子的飞行时间。两项实验的飞行时间测量读出电子学系统集成于尺寸为3U和6U的读出电子学PXI机箱中,基于工作在甚高精度模式下的HPTDC芯片,测量精度25 ps,除去电缆等因素引入的噪声,系统时钟周期-周期抖动的均方根经验值不大于20 ps。

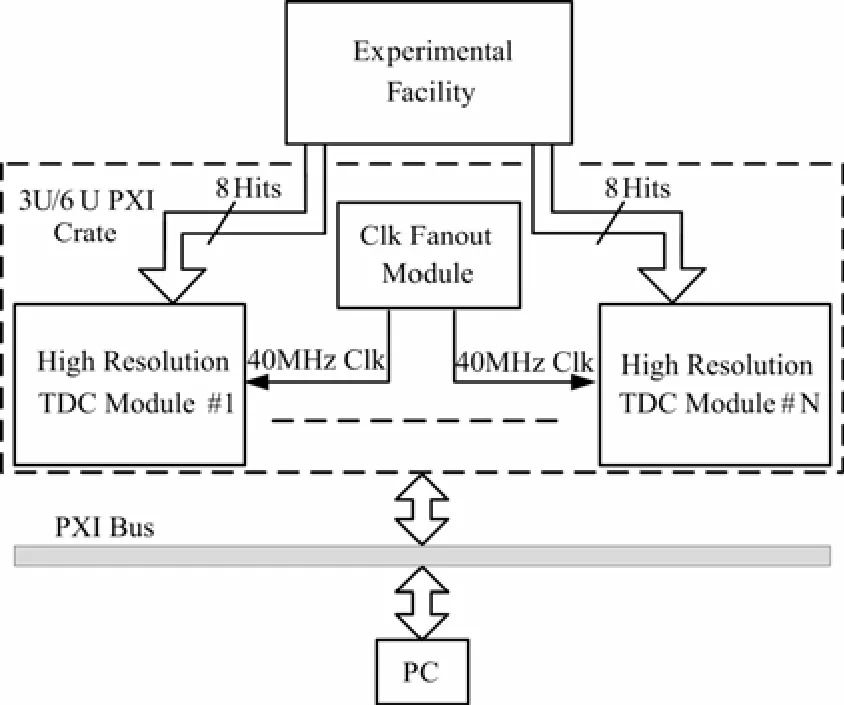

两个飞行时间测量读出电子学时钟插件位于PXI机箱中,使用同轴电缆完成与飞行时间测量电子学插件间的信号传输(图1)。

图1 飞行时间测量读出电子学系统结构图Fig.1 Block diagram of the time-of-flight readout system.

两系统读出电子学时间测量指标相近,对其时钟系统的指标要求也一致,因此,设计采用的技术路线类似。本文介绍这两个系统中时钟插件的设计、测试结果,并对结果进行分析。

1 飞行时间测量读出电子学时钟插件设计

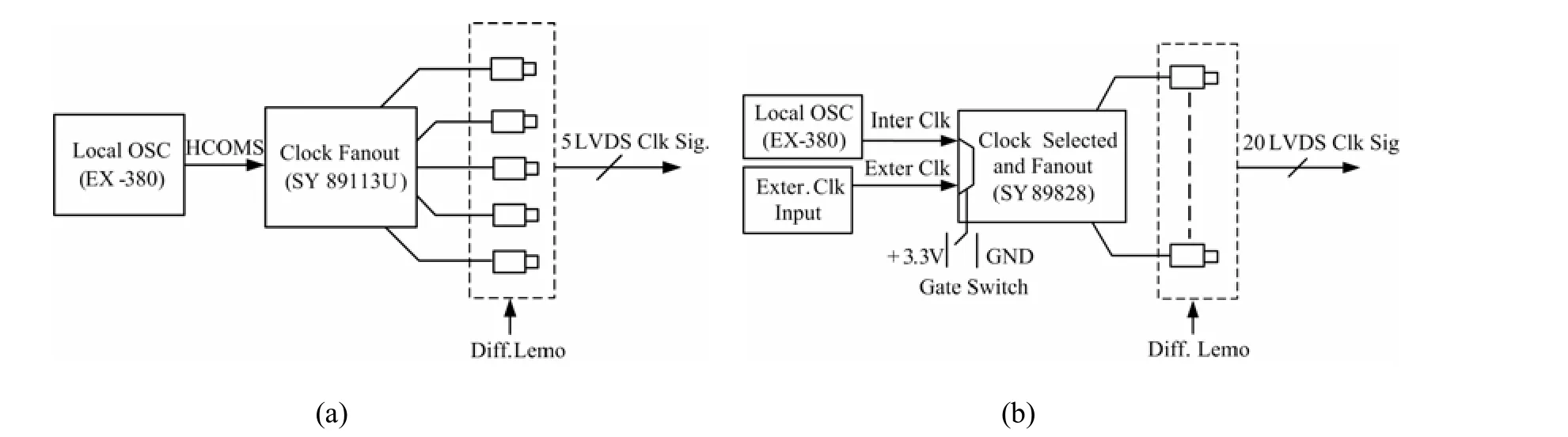

读出电子学时钟插件分别集成于3U和6U PXI插件上,输出多路频率为40 MHz的高质量时钟信号,时钟插件由时钟源、时钟扇出芯片和输出连接器组成。

时钟源的精度决定输出信号的质量,美国Vectron公司的EX-380温度补偿晶振可为时钟插件提供高质量的时钟源信号:其输出信号周期-周期时钟抖动<8 ps(RMS),输出信号上升/下降时间<5 ns;温度为–20℃~70℃时,其温度稳定性为±0.1 μg/g (读出电子学系统系长期运行设备,须考虑时钟源的工作稳定性和温度漂移);在 25℃温度下,其功耗<0.35 W。

时钟扇出芯片接收一路或两路时钟源信号,扇出多路时钟信号。设计要求扇出芯片具有较小的通道间时钟偏差,且引入时钟抖动小。为保证信号传输的强抗干扰能力,并减小功耗,我们采用低电压差分信号(LVDS, Low Voltage Differential Signal)驱动输出的扇出芯片。LVDS驱动器为电流输出型,经接收端100 Ω匹配电阻产生350 mV电压,其特点为:(1) 摆幅低(~350 mV),功耗低;(2) 差分数据传输,对共模输入噪声信号的抵抗能力强,信号噪声和电磁干扰(Electro Magnetic Interference,EMI)都大为减少;(3) 具有较慢的边缘速率(~1 V/ns,在满足波特率前提下尽量减少EMI);(4) 低摆幅驱动信号,实现高速信号传输[9]。根据扇出数的不同,3U时钟插件用SY89113[10](驱动12路输出)时钟扇出芯片,6U时钟插件用 SY89828[11](驱动20路输出),均系美国Micrel公司产品。两款芯片周期-周期时钟抖动指标均<1 ps (RMS),通道间的时钟偏差分别<25 ps和 50 ps。对应LVDS传输,时钟插件的输出连接器选用差分LEMO接头。

为确保高质量差分的时钟信号传输,PCB设计充分考虑信号完整性原则,尽量保持差分线的长度及差分对走线阻抗一致。为避免过孔引入的阻抗不连续性,时钟插件差分对采用表层走线。3U和6U时钟插件各通道距扇出芯片距离差异大,为减小各差分对走线长度不同引入的通道间时钟偏差,对于较短差分对走线采用蛇形线。

图2(a)为 3U时钟插件的时钟部分设计框图,由SY89113U芯片将输入的一路时钟信号以5路的LVDS电平扇出;图2(b)为6U时钟插件的设计框图,由 SY89828芯片选择本地 EX-380晶振产生的40 MHz时钟信号或外部提供的高精度时钟信号,驱动输出20路LVDS电平的时钟信号。图3为两插件的实物照片。

图2 3U(a)和6 U(b)时钟插件的时钟部分设计图Fig.2 Block diagram of the clock modules in 3U (a) and 6U (b) clock modules.

图3 3U(a)和6U(b)时钟插件实物图Fig.3 Pictures of the 3U (a) and 6U (b) clock modules.

2 测量与分析

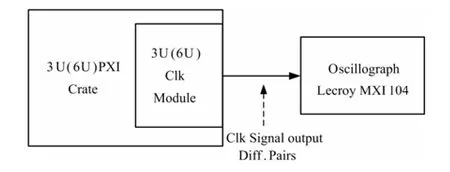

各通道时钟信号的时钟抖动和通道间时钟偏差,是时钟插件的重要指标,我们用美国 Lecroy MXI104示波器获取时钟信号的抖动与偏差指标,其带宽1 GHz,采样率5 GS/s(图4),由示波器数据用MATLAB软件分析抖动的统计特性。

图4 Lecroy MXI104示波器测试时钟抖动示意图Fig.4 Block diagram for testing clock jitter using Lecroy MXI104 oscillograph.

2.1 时钟信号抖动测试

时钟抖动是受外界噪声、串扰、电源电压等因素产生,为随机量。时钟抖动描述方式之一是周期-周期抖动,定义为后一输出时钟周期相对于前一输出时钟周期的变化量,因此,对足够多的信号周期内众多时钟抖动值进行信号分析才有实际意义。往往采用统计指标如标准偏差(对于高斯分布)、最大值、最小值、峰值等描述时钟抖动的统计特性[12]。

2.1.1 时钟抖动的统计直方图和高斯拟合曲线分析

用Lecroy MXI104示波器测量105个时钟信号,由周期变化量数据用MATLAB工具处理计算周期-周期时钟抖动的RMS值。所得6U时钟插件的统计直方图及高斯拟合曲线见图 5,可见时钟信号的周期-周期抖动符合高斯分布,RMS为11.30 ps。同法测得3U时钟插件各通道输出信号的时钟抖动小于11 ps,满足设计要求。

图5 6U时钟插件第11通道输出信号周期-周期时钟抖动的统计直方图Fig.5 Histogram of the clock jitter of Channel 11 in the 6U clock module.

2.1.2 各通道时钟抖动性能的一致性

测试了3U时钟插件的5个通道与6U时钟插件的20个通道的时钟抖动性能,其中6U插件分别用本地晶振和外部时钟(3U时钟插件输出的时钟信号)作为时钟源。3U时钟插件各通道抖动一致性如图6(a)所示,各通道输出信号的周期-周期时钟抖动为10.6–11 ps。图6(b)、6(c)为6U时钟插件分别用本地晶振和外部输入时钟源时的各通道抖动一致性,各通道周期-周期时钟抖动分别集中于10.6–12 ps和10.4–12 ps间,均小于20 ps,符合设计要求。

图6 3U和6U时钟插件各通道抖动一致性曲线,其中6U时钟插件用内部晶振或外部输入时钟源Fig.6 Clock jitter curves of the 3U module, and the 6U module using internal or external clock generator.

2.2 通道间时钟偏差测试与分析

插件通道间时钟偏差来自于扇出芯片输出管脚间的时钟偏差和信号走线长度差异,使用 Lecroy MXI104示波器,分别对3U和6U时钟插件两两通道间的相位偏差进行了测量,待测的两个通道分别用等长的电缆与示波器测试通道连接,并读出两通道的相位延迟,测试设备连接方式如图7所示。

图7 时钟插件通道间时钟偏差测试示意图Fig.7 Block diagram for testing skew between two channels of the clock modules.

由于电缆和示波器测量通道的不一致性将引入误差,使时钟偏差偏离实际值。如图 7,插件通道间的时钟偏差为(A–C),但插件到示波器的引线电缆和示波器通道延迟使两个通道的总延迟分别为B、D,示波器读数实际是引入了B、D的影响。为消除此误差,我们先对两个时钟扇出通道测得Skew 1,再将两根测试线在时钟插件通道端调换重复测试得Skew 2。

由图 7 可知:Skew 1=(A+B)–(C+D),而 Skew2=(C+B)–(A+D),则两被测通道时钟偏差值(A–C)=(Skew 1–Skew 2)/2。

按上述方法,我们分别以两个时钟插件的某一特定通道为基准,测试其余通道与基准通道的相位偏差。实际测试3U时钟插件时,以通道5为基准,测试其余通道与其相位偏差。针对3U插件的测试数据见表1。

表1 3U时钟插件各通道与第5通道时钟偏差统计Table 1 Skews among Channel 5 and other channels of the 3U clock module.

表2 6U时钟插件各通道与第11通道时钟偏差统计Table 2 Skews among Channel 11 and other channels of the 6U clock module.

由表1,3U时钟插件通道5与其余通道时钟偏差最大值为27.36 ps,最小值为–23.47 ps,所有通道的相对时钟偏差不大于51 ps,此偏差来自扇出芯片输出管脚间的时钟偏差和信号线长度差异。例如:通道1和通道2间测得时钟偏差50.83 ps,其中扇出芯片输出管脚间的时钟偏差<25 ps;两个通道信号线长度差为6.35×10–3m,对应46.25 ps时钟偏差(长1 inch,特征阻抗为50 Ω,PCB走线产生信号延迟~185 ps[13])。

测试6U时钟插件时,以通道11为基准,测试其余通道与其相位偏差。针对6U插件的测试数据列于表2。

由表2,时钟信号通道11与其余通道时钟偏差的最大值为53.71 ps,最小值为–86.78 ps,所有通道的相对时钟偏差不大于141 ps,此偏差来自扇出芯片输出管脚间的时钟偏差和信号线长度差异。例如:通道1和通道6间测得时钟偏差140.5 ps,其中扇出芯片输出管脚间的时钟偏差<50 ps;两通道信号线长度差为 1.6×10–2m,对应时钟偏差为116.55 ps。

3 结论

为中国科学院近代物理研究所的反应显微成像谱仪和重离子加速器冷却储存环的内靶实验设计了两种高精度时钟插件,经测试,3U和6U时钟插件所有通道抖动分别小于11 ps和12 ps,3U和6U时钟插件各通道间相位偏差分别不大于51 ps和141 ps。基于3U PXI总线的高精度时间测量系统已在近代物理研究所反应显微成像谱仪中投入使用,时间精度符合设计要求,插件所提供的时钟保证了HPTDC高精度时间测量的需求。6U时钟插件的时钟抖动和时钟偏差测试结果均符合设计要求,即将安装到重离子加速器冷却储存环(HIRFL-CSR)工程的CSRm内靶实验读出电子学系统中。

1 LIU Shubin, FENG Changqing, AN Qi, et al.IEEE Trans Nucl Sci, 2010, 57(2):419–427

2 Schambach J, the STAR Collaboration TOF Group.Proposed STAR Time of Flight Readout Electronics and DAQ, Computing in High Energy and Nuclear Physics,LaJolla, California, 2003

3 CERN/LHCC 2002–016, ALICE Addendum to the Technical Design Report of the Time of Flight System(TOF), ISBN 92-9083-192-8, 2002, 61–70

4 ITU-T Recommendation O.171(04/97).Timing jitter and wander measuring equipment for digital systems which are based on the plesiochronous digital hierarchy, 1997

5 杨俊峰.高速数字串行通信中的时间抖动研究: 博士论文.合肥:中国科学技术大学, 2005 YANG Junfeng.Study on the jitter performance of high-speed digital serial communication based on electronic signal:Doctoral thesis at University of Science and Technology of China, 2005

6 Furukawa K, Suwada T, Kamikubota N, et al.The timing system of KEKB 8-GEV linac.International Conference on Accelerator and Large Experimental Physics Control Systems, 2003, 130

7 Liu D K, Leng Y B, Cheng W X, et al.SSRF Timing system.Second Asian Particle Accelerator Conference,2001

8 LI Hao, LIU Shubin, FENG Changqing, et al.TOF Clock System for BES III.IEEE Transactions on Nuclear Science, 2010, 57(2):442–445

9 Altera.Board Design Guidelines for LVDS Systems,2000.http://www.altera.com / literature/wp/wp lvdsboard.pdf

10 SY89113 Datasheet Micrel, Inc., 2005

11 SY89828 Datasheet Micrel, Inc., 2002

12 Nelson Soo.Jitter measurement techniques, application brief AB36, 2000

13 William R, Blood Jr.MECL system design handbook.Fourth ed.Printed in U.S.A: Motorola Semiconductor Products Inc, 1988