时间和功耗双随机化的 AES抗差分能量攻击设计

2010-03-20严迎建朱巍巍

严迎建,刘 凯,任 方,朱巍巍

(解放军信息工程大学电子技术学院,郑州 450004)

时间和功耗双随机化的 AES抗差分能量攻击设计

严迎建,刘 凯,任 方,朱巍巍

(解放军信息工程大学电子技术学院,郑州 450004)

分析了时间随机化技术的不足以及掩码技术(功耗随机化)的缺点,在完全防御差分能量攻击的基础上进行基于抗差分能量攻击的设计,提出一种时间和功耗双随机化的电路结构,将其应用在AES算法中,并在FPGA密码芯片、示波器和PC机组成的功耗采集分析平台中进行了验证.结果表明,该电路具备较强的抗差分能量攻击能力.

差分能量攻击;时间随机化;功耗随机化;AES算法

能量攻击技术最早由 Kocher等[1]提出,已成为攻击智能卡等密码芯片的一种有效手段.相对于其他的旁道攻击技术而言,由于功耗信息采集的设备相对比较简单,能量攻击成为最易实施的(针对密码实现的)攻击技术之一,其危害远大于传统的攻击手段,对密码芯片自身的安全构成巨大威胁.

能量攻击主要分为简单能量攻击(simple power analysis,SPA)和差分能量攻击(differential power analysis,DPA)2大类,由于差分能量攻击采用统计手段进行功耗分析,能消除噪声干扰,对密码芯片带来很大威胁.针对差分能量攻击带来的威胁,各种防御措施得到了广泛的研究.相比其他防护技术而言,随机化技术容易实现且可以应用在各种算法中,对故障攻击、时间攻击和高阶差分能量攻击等也有一定的防护作用.随机化技术应用于抗差分能量攻击时通常分为时间随机化和功耗随机化.

时间随机化将每次密码芯片运算中的操作随机地分布在时间域上,使得功耗信号的统计分析变得十分困难,但时间随机化只能增加差分能量攻击的难度,不能完全抗差分能量攻击.功耗随机化使得每次密码芯片运算中操作的功耗都不依赖于输入(密钥),它通常采用掩码技术来实现,但掩码技术需要针对不同的密码算法设计不同的掩码算法,掩码算法的开发周期长且实现时要占用大量的资源.针对 2种随机化技术存在的问题,本文提出了一种时间和功耗双随机化的密码芯片抗功耗分析电路.

1 差分能量攻击原理

差分能量攻击需要重复采集大量的功耗数据并对其统计分析得出密钥.利用某个状态字节的值作为区分函数,借鉴基于汉明重量的功耗模型[2-4]中提到的功耗与状态字节中 1的个数成正比,本文假设状态字节为 1的时候功耗为 P+a,状态字节为 0的时候功耗为 P.差分能量攻击如图 1所示.

图1(a)中每行表示一组明文加密得到的一组功耗数据,猜测值即表示攻击者利用猜测密钥得到的算法的中间值,攻击者利用猜测值将功耗数据分为 2组,在分组后的数据分析阶段,攻击者首先求出各组的功耗均值,再由 2个功耗均值求差.

当攻击者猜测到错误密钥时的差分能量攻击如图 1(b)所示,攻击者利用错误密钥得到的猜测值不符合芯片运算值,在他用猜测值对功耗数据进行分组的时候,相应地将 2组有差异的功耗数据打乱,攻击者最后得到的差分功耗不为 a.由于功耗数据是基于猜测密钥运算的中间值进行分组,每个猜测密钥对应一个分组,而只有正确密钥可以将2组具有差异的功耗数据区分开,因此,密钥猜测正确时的差分功耗值最大.

图1 差分能量攻击Fig.1 Differential power attack

2 基于随机化的抗 DPA技术

2.1 时间随机化抗 DPA的基本原理

能量攻击之所以能成功,是因为在密码芯片运行时相应的运算操作都出现在固定的时间点上.如果能随机地移动这些运算操作在时间域里的位置(即时间随机化),那么,功耗信号的统计分析将变得十分困难[5].

采用能量攻击方法对时间随机化的电路功耗进行分析,结果如图 2所示.假设插入随机延迟后区分函数对应位置处的运算可能出现在 A点或 B点,A点在时间轴上位于 B点的前面,为密钥猜测正确的情况,第 1行所示运算出现在时间 B点,A点的值还保持上一次的运算结果不变,用 X(未知数据)表示.由于 A点没有运算功耗为0,B点的功耗与攻击者猜测的值相同,第2行与第1行类似.第 3行运算出现在时间A点,那么,到达时间点 B的时候,运算已经完成,芯片中运算的中间值不变,由于B点没有运算功耗为 0.

时间随机化只是将原来的差分尖峰分散在不同的时间点上,如果将每条功耗曲线在各个时间点上的差分尖峰加起来,攻击者可以分析得出正确密钥.但这只是理想环境下的测量,实际测量中要受到测量环境中各个因素(噪声)的影响,为了使实验结果与理论分析相符合,通常采取增加功耗样本数量的方法来消除噪声的影响.因此,可以看到时间随机化技术增加了差分能量攻击的难度.

2.2 功耗随机化抗 DPA攻击的基本原理

能量攻击成功的另一个原因是攻击者可以根据密码芯片基本逻辑单元的特征(各种功耗模型)预测某个密钥相关操作的功耗.如果使得操作的功耗随机产生,那么攻击者根据自己的猜测将得到错误的密钥,从而有效地保证了密码芯片的安全.利用差分能量攻击分析功耗随机化[6]的密码芯片如图 3所示.

功耗随机化后实际值变成了随机数,攻击者在密钥猜测正确时不可能将密码芯片的功耗分为 2个有最大差异的集合,相反在猜测到某个错误密钥时可能将密码芯片的功耗信息分为 2个有最大差异的集合,并且可能是几个错误密钥都将密码芯片的功耗信息分为 2个有最大差异的集合,因此,攻击者无法获得正确密钥.

实现功耗随机化的常用技术—掩码技术[6]就能获得防御效果,由于掩码技术需要针对特定的密码算法设计相应的掩码算法,掩码算法设计难度高并且不能通用,掩码技术在硬件实现时耗费资源多,并且掩码技术不能抗高阶差分能量攻击[7].功耗随机化的另一种实现方式—并行冗余操作[8]相当于功耗掩盖,无法抵御大数据量的攻击.因此,迫切需要一种通用、简单并且防护全面的实现方式.

2.3 时间和功耗双随机化的电路结构

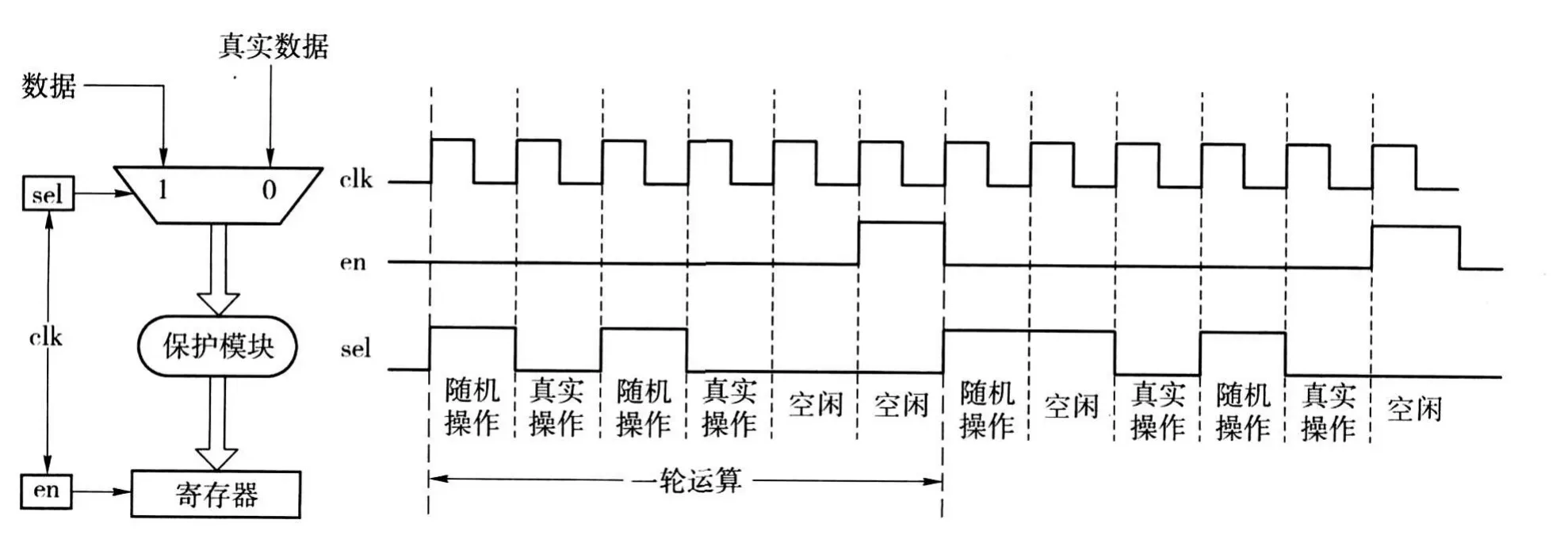

结合时间随机化和功耗随机化的思想设计了一种时间和功耗双随机化的电路,它弥补了时间随机化的不足,可以应用在各种密码算法的硬件实现中,电路结构如图 4所示.

图4 时间和功耗双随机化的电路结构Fig.4 The circuit of time randomization and power randomization

sel信号控制数据选择器,0输入端输入真实的运算数据,1输入端输入随机操作的随机数.在每轮运算的开始,由 sel选择随机数输入到被攻击模块中,即在每轮运算的开始部分随机数输入被攻击模块进行操作,在每轮运算的最后 1个周期中 sel固定为 0,此时被攻击模块对数据路径中运算的正确数据进行操作.在 1轮运算中,除第 1个和最后 1个 clock周期外,其他部分为随机运算部分,随机运算部分根据随机控制端 sel的值随机选取真实数据或随机数据执行运算.下面以图 4中第 1轮运算为例,第 1个 clock周期执行随机数据,第 2个clock周期执行真实数据,第3个 clock周期执行随机数据,第 4个clock执行真实数据,第 5、6个 clock周期密码操作电路单元为空闲状态.

时间和功耗双随机化的电路不仅使得真实操作在时间上随机执行,并且每次加/解密运算在同一时间点处的功耗无法预测,从而使差分能量攻击失去效果.

2.4 基于时间和功耗双随机化的 AES密码芯片设计实现

将时间和功耗双随机化的电路应用于 AES密码芯片中,把 AES算法中字节代替、行移位、列混合和密钥异或操作都嵌入图 4所示的保护模块中,不论攻击者选择哪个操作的输出作为区分函数都将失去攻击效果.将上述设计用 Verilog语言描述后在 ModelSim仿真工具中得到如图 5所示的仿真结果,椭圆标记为芯片输出的加密结果.

图5 时间和功耗随机化的AES加密仿真结果Fig.5 The encryption simulation of AES on time randomization and power randomization

AES算法 1轮运算包括 7个 clock周期,每轮运算中除了第 1个 clock周期和第 7个 clock周期中的sel信号分别固定为 1和 0之外,其他 5个 clock周期中的 sel信号都由随机函数产生.可以肯定每轮开始的第 1个 clock周期先对随机数进行运算,但由于 SEL信号可能在第 6个 clock周期或者前几个周期已经被置低,正确数据的运算不一定在每一轮最后的第 7个 clock周期才开始.

3 结果分析

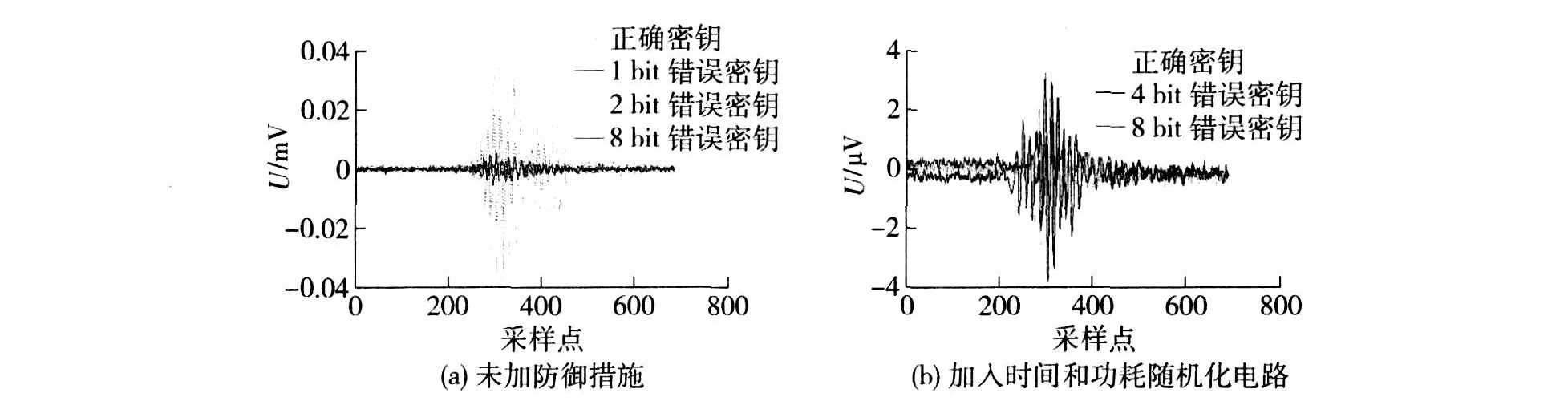

为了观察时间和功耗双随机化的 AES抗 DPA的效果,选择 AES第 1轮运算中的 S盒作为攻击点,利用改进的基于汉明距离功耗模型的区分函数对未加任何防御措施的AES做差分能量攻击.分析结果如图6(a)所示.截取 AES第 1轮运算的差分功耗曲线,1 bit错误密钥表示和正确密钥相差 1位的错误密钥,可以看出,1 bit错误密钥和 8 bit错误密钥差分后的结果几乎为 0,2 bit错误密钥的差分功耗还有一定的尖峰,但正确密钥差分后的尖峰最高.

图6 AES的差分能量攻击结果Fig.6 Differential power attack on AES

接下来采用和图 6(a)所示结果相同的明文、密钥以及区分函数对时间和功耗双随机化的 AES进行差分能量攻击.分析结果如图 6(b)所示.

进行差分后在其他位置没有高于噪声的尖峰出现,图中只列出第 1轮运算中第7个 clock对应位置处的差分功耗曲线,相对于图 6(a)所示的差分功耗,图 6(b)中的差分功耗尖峰缩小了 1个数量级,并且分辨不出正确密钥的差分尖峰,攻击者无法分辨出正确密钥.对于实验中其他位置没有明显尖峰出现是因为实际测量中要受到噪声的影响,一个信号是否可以表现出自身的特性通常基于信号和噪声的比例来衡量,所以实际测量和理论分析会有一定的差距,实际测量中分散在时间域上的某些个点的功耗在差分后不容易被观察到.

4 结束语

设计的时间和功耗双随机化的电路结构简单、资源代价小,且扩展性(时间随机化的范围)强,方便应用于各种密码算法.同时,该电路不仅可以应用于密码芯片抗能量攻击中,还可应用于密码芯片的抗故障攻击、时间攻击和高阶差分能量攻击中.

[1]KOCHER P,JAFFE J,JUN B.Differential power analysis[C]∥Proc.Advances in Cryptology(CRYPTO'99),Germany:Berlin Springer,1999:388-397.

[2]MESSERGES T S,DABBISH E A,SLOAN R H.Investigations of power analysis attacks on smartcards[C]∥Usenix Workshop on Smartcard Technology,Chicago:Illinois,1999:151-162.

[3]AKIH IKO S,KOKI A.Algorithm-level evaluation of DPA resistance to cryptosystems[J].Electrical Engineering in Japan,2008,165(3):1221-1228.

[4]CLAVIER C,CORON JS,DABBOUSN.Differential Power Analysis in the Presence of Hardware Countermeasures[C]∥CHES 2000,Berlin:New York Springer,2000:252-263.

[5]韩军,曾晓洋,汤庭鳌.基于时间随机化的密码芯片防攻击方法[J].计算机工程,2007,33(2):2-8.HAN Jun,ZENG Xiao-yang,TANG Ting-ao.Modeling timing random ization in cryptographic chip against power analysis attack[J].Computer Engineering,2007,33(2):2-8.(in Chinese)

[6]GOLIC JD,TYMEN C.Multip licativemasking and power analysis of AES[C]∥Workshop on Cryp tographic Hardware and Embedded Systems-CHES 2002,Berlin:New York Springer,2002:198-212.

[7]MESSERGES T.Using Second-Order Power Analysis to Attack DPA Resistant Software[C]∥Workshop on Cryptographic Hardware and Embedded Systems-CHES 2000,Berlin:Berlin Springer,2000:238-251.

[8]GOUBIN L,PATARIN J.DES and differential power analysis-the duplication method[C]∥Workshop on Cryptographic Hardware and Embedded System s-CHES 1999,Berlin:Berlin Springer,1999:158-172.

(责任编辑 张士瑛)

Design of AESon Time Randomization and Power Randomization Based Differential Power Analysis Resist Countermeasure

YAN Ying-jian,LIU Kai,REN Fang,ZHU Wei-wei

(Institute of Electronic Technology,the PLA Information Engineering University,Zheng Zhou 450004,China)

The problem which time random ization can't defend differential power analysis completely and the defect of the MASK technique which is usually implemented for the power randomization is analyzed.Based on the absolutely resist differential power analysis,the design should focus on the resource and commonness,the paper propose a time and power randomization circuit,AES algorithm containing this circuit is implemented and is testified in the power collection and analysis system.The result of differential power analysis p rove the design to be practical to resist DPA.

differential power analysis;time randomization;power randomization;AES cryptography

TP 309

A

0254-0037(2010)05-0659-05

2009-12-10.

国家“八六三”计划基金项目资助(2008AA 01Z0103).

严迎建(1973—),男,河南扶沟人,副教授.