基于System Generator数字中频接收机的设计

2010-03-14吴尽昭

冯 昭,吴尽昭

(电子科技大学 光电信息学院,四川 成都 610054)

1 引言

在传统数字信号处理系统的设计中,需要先用Matlab等仿真软件进行建模仿真,得到理想的方针结果后,再根据仿真过程,使用硬件描述语言(VHDL,Verilog HDL)[1]创建工程,最后完成硬件仿真。Xilinx公司提供的DSP设计开发工具System Generator和MathWorks Matlab的Simulink是无缝链接的。利用System Generator进行系统级建模的工程中可以包含多种元素,比如数据流、HDL模块以及Xilinx模块等,通过Simulink中调用System Generator Blockset中的模块箱结合,将系统级设计和DSP算法开发相链接。通过软件仿真后可以直接生成硬件代码,下载到硬件环境中进行测试。这样使得那些即使不熟悉FPGA的DSP系统设计工程师及算法工程师也能够设计、仿真和验证DSP系统。

2 基于System Generator的DSP系统开发流程

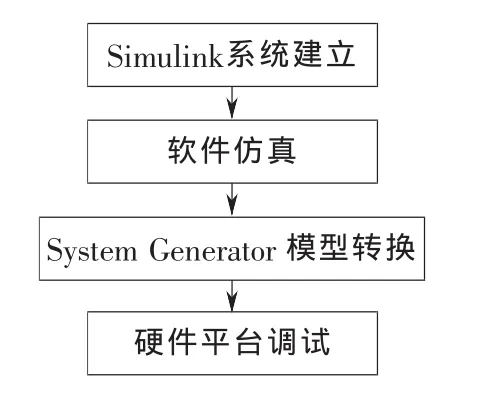

在Simulink的可视化环境中,根据系统设计功能将Xilinx模块链接成所设计的系统,并定义合适的系统参数;而后运用System Generator将Simulink模型转换成硬件可执行模型,将系统定义的参数对应至硬件实现的实体以及输入输出端口,并会自动完成综合、仿真与实现。整个开发流程分为Simulink系统建立、软件仿真、System Generator模型转换及硬件平台调试4个步骤。

在Simulink可视化设计环境中,重要的是:在Simulink环境中实现定点算法,根据系统设计功能将Xilinx模块连接成设计系统,并定义合适的系统参数;而后利用System Generator将Simulink模型转换为可执行的硬件模型,将系统定义的参数对应到硬件实现的模块、输入/输出端口等属性;最后将设计生成可对器件编程的比特流文件,将其下载到目标芯片中。因此,典型的开发流程如图1所示,其中System Generator会自动为FPGA的综合、HDL仿真以及实现生成命令文件[2],用户只需完成Simulink设计以及比较最终的RTL输出结果。整个开发流程都是在可视化的环境中完成的。

图1 基于System Generator的DSP系统卡发流程

3 基于System Generator数字中频接收机的设计

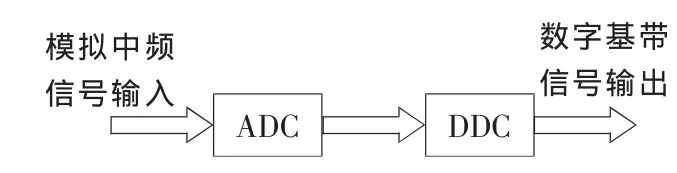

数字中频接收机系统由模数转换器(ADC)、数字下变频器(DDC)组成,如图2所示。其中,ADC主要完成对模拟中频信号进行采样,得到数字化的中频信号,DDC将感兴趣的信号转换至基带,同时做采样率变换及滤波处理,得到正交I,Q信号送后续的数字信号处理器进行基带信号处理[3]。

图2 数字中频接收机系统

在本文涉及的数字中频接收系统中,输入信号的中心频率为46MHz,采样率为180 MHz,带宽为20 MHz的信号,把中心频率搬至0 MHz,然后抽取下变频和滤波模块实现6倍抽取,把采样率变为30 MHz的正交基带信号。

3.1 数字下变频器设计

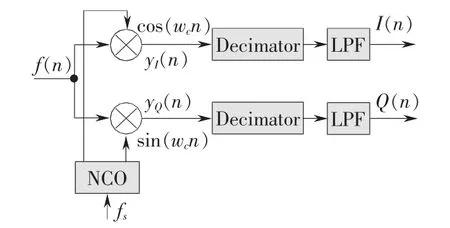

DDC是整个中频数字化接收机的核心,DDC克服了模拟下变频中存在的混频器的非线性和模拟本振的频率稳定度、边带、相位噪声、温度漂移、转换速度等问题,其频率步进、频率间隔也具有理想的特性,因而得到了广泛的应用。DDC由数控振荡器(NCO)、混频器、抽取器和低通滤波器(LPF)组成[4],如图3所示。

图3 DDC结构框图

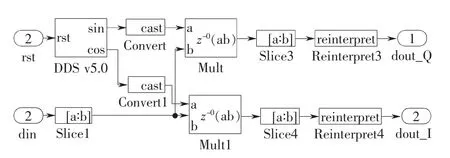

3.2 NCO及混频器设计

数控振荡器是决定数字中频性能的主要因素之一。NCO的目标是产生频率可变的正交正余弦样本。在FPGA中,NCO一般采用直接数字频率合成(DDS)的方法来实现[5]。DDS技术与传统的锁相频率合成器相比,有以下几项优点:1)DDS较于模拟VCO的相位噪声减少许多;2)DDS只需通过改变频率字就可以提供精确的信道间隔;3)DDS提供了几块的信道转换速度,不必像VCO那样通过负反馈来稳定频率。4)DDS可以在数字域对输出信号进行各种调制,只需把相关的数据写在ROM中即可[6]。System Generator Blockset中有高性能的DDS可以直接调用。本设计调用的是DDS v5.0,其自身时钟频率设置为180MHz,动态范围36 dB,输出的正交正余弦信号的频率为46MHz。基于System Generator的NCO及混频器设计模型如图4所示。

图4 NCO及混频器设计

3.3 抽取器及低通滤波器的设计

抽取器(Decimator)完成信号采样率的降低和滤波功能。在多级滤波器级联结构中,通常第一级以较高的比率进行抽取,而后面的滤波器采用低抽取率并完成整形,总的抽样率为各级抽取率之积。高抽取率的抽取滤波器可以选用积分梳状滤波器(CIC)。这种滤波器在抽取率大于10的情况下是最有效的,但是它同时引入了有用信号的通带频谱的衰减。解决办法是在CIC滤波器之后级联一级或两级滤波器来进行补偿,然后再进行整形。当前最常采用的是半带抽取低通滤波器[7]。CIC在实现滤波时无需乘法运算,只需要延迟期和累加器,对于一个窄带信号,在多级抽取结构中把速率最高的第一级用CIC实现,可以极大的降低运算量。CIC滤波器很适合作抽取器前的抗混叠滤波器,通过CIC滤波并抽取后把高的数据率降到较低的数据率,易于后继的半带滤波器(HB)抽取和FIR滤波[8]。HB计算效率高,实时性强,因此把HB滤波器放在第二级。最后一级使用FIR滤波器实现低通滤波器,滤掉带外的杂波。

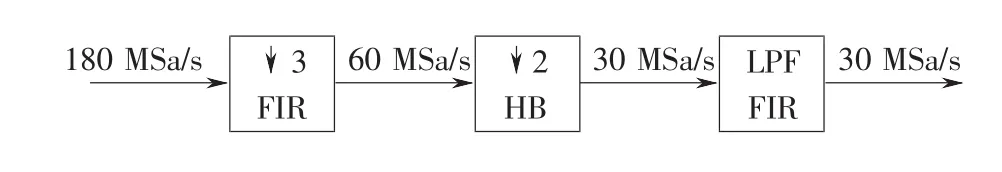

如果需要进行高倍的采样率变换,那么CIC将是非常合适的,无论是在实现性能或是资源节省方面,CIC都将优于FIR[9]。在本设计中,中频信号的采样率是180MSa/s(兆采样/秒),基带信号的采样率是30 MSa/s,只需要6倍的采样率变化,而且带宽为20 MHz,不是窄带信号,因此使用FIR作为第一级的抽取滤波器。抽取器及低通滤波器的结构如图5所示。

图5 抽取器及低通滤波器结构图

基于System Generator的FIR滤波模块主要采用IP核设计,而对于基于IP核设计的FIR滤波器来说,一般可以直接采用FIR Compiler产生系数,也可以由Matlab产生的系数文件再装载到IP核中。后一种方法的优点在于可选的滤波器设计方法更对,且可以先对设定系数的滤波器进行仿真,初步检验一下其滤波效果,这样可以大大减少系统设计的时间[10]。在设计滤波器时,首先根据各级滤波器的滤波特性,使用Matlab的滤波器设计工具FDAtool(Filter Design&Analysis tool)计算出抽取系数并进行量化,然后调用Xilinx的IP核FIR Compiler v4.0,对各项参数进行设置并导入量化后的系数,就可以得到理想的FIR滤波器。图6所示为基于System Generator的数字中频接收机原理图。

图6 基于System Generator的数字中频接收机原理图

3.4 仿真结果及分析

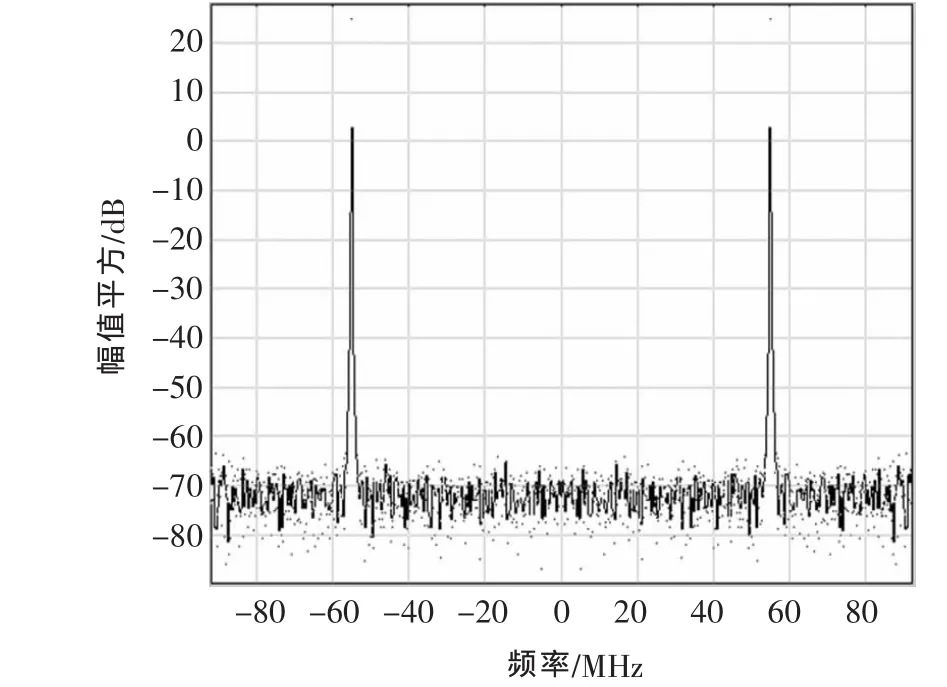

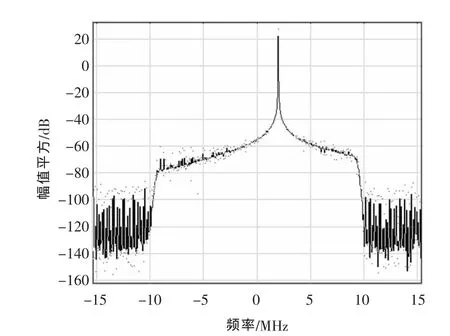

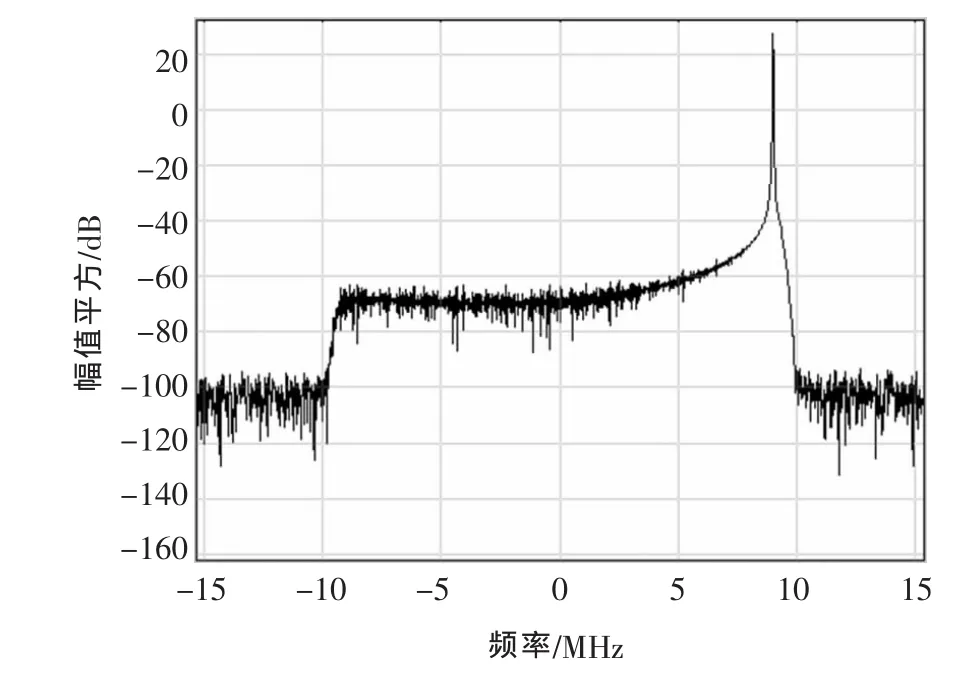

仿真采用单音信号作为输入信号,分别使用频率为48 MHz,55 MHz,位宽为 11 bit,采样率为 180 MSa/s 的信号输入,输入信号的频谱如图7,图8所示。经过下变频,抽取及低通滤波后的采样率为30 MSa/s的基带信号频谱分别如图9、图10所示。

图7 11 bit位宽48 MHz单音信号频谱

图8 11 bit位宽55 MHz单音信号频谱

图9 48 MHz单音信号输入的输出信号频谱

图10 55 MHz单音信号输入的输出信号频谱

由图7~10可以看出,输入48 MHz的中频单音信号与55 MHz的单音信号经过DDC处理后的信号频率分别为2 MHz与9 MHz,信号频谱下移了46 MHz。而采样率由180 MSa/s变至30 MSa/s,说明本接收机系统成功实现的20 MHz带宽信号的46 MHz下变频及6倍抽取的采样率变换。

4 小结

通过对基于System Generator的数字中频接收机的设计,详细说明了如何利用System Generator在Matlab下设计数字信号处理系统。使用System Generator进行设计,可以实现在Matlab上的可视化设计方法,各种常用的DSP处理模块如FIR,DDS等都可以直接调用,在保证了性能的情况下,缩短了系统开发周期。使用本方法可以快速构建DSP系统,并在不具备外部硬件测试平台的情况下,使用JTAG口读取数据进行分析,进行软硬件联合仿真,相对于传统的开发方式来说,具有很大的优势。

[1]陈美燕,王丹.基于Verilog HDL的信号处理板卡中双向端口的设计[J].电视技术,2008,32(S1):62-64.

[2]Xilinx.System Generator for DSPReference Guide[EB/OL].[2010-01-01].http://www.xilinx.com/support/documentation/sw_manuals/xilinx11/sysgen_ref.pdf.

[3]陈宝龙.基于FPGA的数字中频接收机的研究[D].江苏:南京理工大学,2008.

[4]王水,吴继华.用FPGA实现数字中频[J].电子设计技术,2007,14(9):169-170.

[5]何勤,束永江.一种通用中频数字化接收机的实现[J].现代电子技术,2009(11):94-95.

[6]赵国栋,郭德淳.基于FPGA的数字中频接收系统[J].军民两用技术与产品,2006(1):43-47.

[7]CARDELLS T F,VALLS C A.Optimized FPGA-implementation of quadrature DDS[C]//Proc.IEEE International Symposium on Circuits and Systems.[S.l.]:IEEE Press,2002:369-372.

[8]肖乾友,黄晓革,骆志敏.一种数字中频接收机的设计与实现[J].电讯技术,2006(4):123-127.

[9]崔文.基于FPGA的数字上下变频器的研究与实现[D].西安:西安电子科技大学,2006.

[10]李振军,曾凌云,郑善贤.基于FPGA的中频数字接收机设计与实现[J].计算技术与自动化,2009,28(2):50-53.