LTE系统的CRC校验算法研究及DSP实现*

2010-01-27罗友宝李小文谷向阳

罗友宝,李小文,谷向阳

(重庆邮电大学 通信与信息工程学院,重庆 400065)

LTE系统的CRC校验算法研究及DSP实现*

罗友宝,李小文,谷向阳

(重庆邮电大学 通信与信息工程学院,重庆 400065)

通过对两种常用CRC校验算法的研究分析,为TD-LTE测试仪表系统选择了一种最优的CRC校验算法,并在TMS320C64xDSP中实现。将CRC校验程序在CCS3.3中运行,其结果验证了算法的可行性、高效性。

长期演进;循环冗余校验;查表法;块异或长除法;DSP实现

循环冗余校验码[1]CRC(Cyclic Redundancy Check)是数据通信领域中最常用的一种差错校验码,其特征是信息字段和校验字段的长度可以任意选定。

为了完成信号传输过程中误码检测,获得正确无误的传输数据,LTE(Long Term Evolution)系统针对不同的数据传输采用了多种格式的循环冗余码,以适应系统高速率高性能的需求。

1 LTE系统中的循环冗余码

LTE作为准 4G技术,以正交频分复用 OFDM(Orthogonal Frequency Division Multiplexing)和多输入多输出MIMO(Multiple-Input Multiple-Out-put)技术为基础,下行采用正交频分(OFDM)多址技术,上行采用单载波频分(SC-FDMA)多址技术,在 20 MHz频谱带宽下能够提供下行100 Mb/s与上行50 Mb/s的峰值速率。

LTE TDD(亦称 TD-LTE)系统采用了 4种格式[2]的CRC:CRC24A、CRC24B、CRC16、CRC8。其生成多项式如下:

其中长度为24的CRC24A和CRC24B主要用于共享信道数据传输[3],长度为 16的 CRC16主要用于下行控制信道和广播信道数据传输,长度为8的CRC8主要用于CQI(Control quality information)信息的传输。

2 CRC算法分析及选择

CRC的校验原理非常简单,它要求发送方和接收方采用同一个生成多项式 g(x),且g(x)的首位和末位的系数必须为l。编码时将待发送的数据t(x)除以g(x),得到的余数作为CRC校验码添加到t(x)的后面;译码时将接收到的数据 r(x)除以g(x),如果余数为0,则说明校验正确,否则校验失败,从而判断数据帧是否出错。在工程应用中,常用的CRC校验算法主要有两种:查表生成法和块异或长除法。

2.1 查表生成法

查表算法的思路是先离线计算数据信息的所有余式,把它们置于一个称为“余式表”的表格中,供随时读取和调用[4]。算法描述如下:

(1)离线计算出数据的CRC余式表。

(2)初始化 CRC码为:RnH=RnL=0。

(3)读取信息的当前字节M,计算I=M+RnH,用I作为索引查表得出rnH和rnL。

(4)计算新的 CRC校验码:RnH=RnL+rnH;RnL=rnL。

(5)如果信息没有处理完毕,则转入步骤(3);否则CRC计算完成,结果为RnH和RnL。

这种算法的优点是运算量小、速度快、效率高;缺点是可移植性较差,且要事先计算出余式表,而不同长度的生成多项式的余式表不同,因此余式表会占用系统较大的存储空间,增大系统资源开销。

2.2 块异或长除法

块异或长除法是依据CRC校验码的产生原理实现的。算法描述如下:

(1)初始化,将寄存器初始化为 0。

(2)在信息比特后添加CRC长度个0,最终作为 CRC添加的空间。

(3)读取一个数据块(块的大小由处理器的字的单位长度决定)。

(4)判断块的最高位是否为‘1’,若为‘1’则数据块与生成多项式做一次异或操作。

(5)将数据左移一位,如果当前块的剩余比特等于CRC生成多项式的长度,则转入步骤(3);否则转入步骤(4)。

(6)如果所有数据都已经操作完毕,则计算结束,寄存器中的值为最终求得的CRC。

这种算法的优点是算法简单、容易实现、修改灵活、可移植性好,对任意长度的生成多项式都适用;但因为它一次只能处理一位数据,因此计算效率低,运算量大。

如前所述,在TD-LTE系统中采用了4种格式的CRC,如果采用查表算法,则需要建立 4张查找表,会占用系统较大的存储空间,且程序移植性差;如果采用块异或长除法,则又会出现计算效率低,运算量大的问题。

综上分析,结合项目需求及系统硬件配置,考虑到系统所采用的高效DSP处理器——TMS320C64x(主频最高可达到1.2 GHz)可以弥补块异或长除法的低效性,系统最终采用块异或长除法来实现。

3 CRC算法的DSP实现

3.1 硬件简介

TMS320C6000系列DSP是TI公司1997年2月推向市场的高性能 DSP,综合了目前 DSP性价比高、功耗低等优点。TMS320C64x系列在TMS320C6000 DSP芯片中处于领先水平,它不但提高了时钟频率,而且在体系结构上采用了VelociTI甚长指令集VLIW(Very Long Instruction Word)结构[5],片内有 8个独立功能单元的内核,每个周期可以并行执行8条32 bit指令,最大峰值速度4800 MIPS,2组共64个32 bit通用寄存器,32 bit寻址范围,支持8/16/32/40位的数据访问,片内集成大容量SRAM,最大可达8 Mbit。由于其出色的运算能力、高效的指令集、大范围的寻址能力,使其特别适用于无线基站、测试仪表等对运算能力和存储量有高要求的应用场合。

3

.2 CRC校验的DSP实现

因为系统采用了4种格式的CRC,如果对每种格式进行单独实现,不仅任务繁琐,而且增加了系统的代码量,更给代码测试和维护增加了难度。因此本实现采用统一实现,即同一个程序,支持系统中的所有CRC格式,仅需在程序头部增添一点格式判断的代码即可。

虽然TMS320C64x DSP处理器的字长为 32 bit,但是为了兼容4种格式的CRC,最终决定数据的分块长度为半字,即16 bit,这样做的目的就是为了支持CRC24,因为TMS320C64x DSP的寄存器在用作逻辑移位寄存器使用时,其有效长度为40 bit。

根据LTE协议,输入数据按大端模式输入。为了处理方便,每次读入半字都将其倒序,采用低端对齐的方式进行CRC除法,因此,CRC多项式也必须经过倒序。最后生成的CRC也是倒序的,需要再次倒序,然后进行加扰[2](如果必要的话),最后添加到输入数据后面。倒序可使用指令“BITR”,简单易行。

输出数据仍为大端模式。由前面所述可知:CRC8的生成多项式倒序值为 0x1b3;CRC16的生成多项式倒序值为 0x10811;CRC24A的生成多项式倒序值为0x1be64c3;CRC24B的生成多项式倒序值为0x18c0003。

值得注意的是:输入数据后面应该多写入一个字的0,因为每次取半字处理,当剩余比特为最大15 bit且CRC为最长 24 bit时,组合起来也不会超过 40 bit,避免特殊性的出现,以便统一处理。同时完成CRC计算过后,可以直接将CRC添加到原数据之后,而不担心其会覆盖系统中的其他数据,引起不必要的错误。

图1为CRC计算及添加的程序实现流程。当CRC格式为 CRC16、CRC24A、CRC24B时,读取的第一个数据块(半字)在第一次内循环中将只作 16次的移位,而没有异或操作,表面上看在这里应该加一个判断,如果是这种情况则直接将数据右移 16 bit,然后接着处理第二个数据块。但这样会对后续的数据块造成麻烦,因为每个数据块到达此处都需判断一次,当数据量比较大时,会带来更大的开销,因此在程序流程中可以忽略此问题。

在接收端,CRC的校验与发送端的计算基本相同,只是由于LTE系统的特殊性,如果在发送端CRC曾被加扰过,则在接收端校验之前,应先从接收到的数据末尾截取出CRC进行解扰,然后再将解扰后的CRC添加回去,最后对整个接收数据进行CRC校验。如果CRC校验正确,则接收数据正确;否则接收数据错误,在此程序流程不再赘述。

4 性能分析

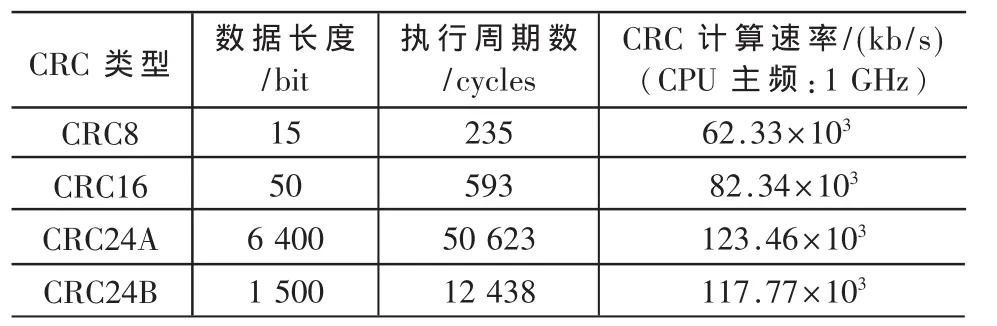

在DSP软件实现中,通过指令并行,尽量优化程序循环体[6],减少或消除程序中的“NOP”指令。对于不同格式的CRC,根据它们所用的环境以及数据的大致长度,通过程序仿真运行,可以得到统计结果如表1。

表1的数据长度仅为个别举例,但不失一般性。从表中可以看出,虽然块异或长除法的运算量较大,但是当运用TMS320C64x芯片实现时,由于处理器的超高主频,其计算速率也非常快,完全可以忽略它的计算量。因此,本实现采用块异或长除法不仅简化了程序实现方法,还减少了模块程序代码,节约了系统存储空间。

本文从理论分析出发,根据 TD-LTE系统特性,选择了一种最优的CRC校验算法,并在TMS320C64x芯片上加以实现,详细讲述了块异或长除法在DSP中的实现方法。程序运行结果表明,本实现能够满足LTE系统的需要,具有可行性和高效性。

表1 统计结果

[1]王新梅.纠错码原理与方法[M].西安:西安电子科技大学出版社,2003.

[2]3GPP TS 36.212 v8.7.0:Multiplexing and channel coding. (Release 8)[S].2009-05.

[3]Qualcomm Europe.Generator polynomial for transport block CRC[EB/OL].Http://www.3gpp.org,2007.10.

[4]张莉丽,张振权,刘仁.CRC查表生成算法汇编的实现及其优化[J].计算机应用,2005(4).

[5]Texas Instruments Incorporated.TMS320C64x/C64x+DSP CPU and Instruction Set Reference Guide[EB/OL].Http://www. ti.com.cn,2008.

[6]Texas Instruments Incorporated.TMS320C6000系列 DSP编程工具与指南[M].田黎育,何佩琨,朱梦宇,译.北京:清华大学出版社,2006:32-50.

Research and DSP realization of CRC algorithm in LTE system

LUO You Bao,LI Xiao Wen,GU Xiang Yang

(School of Communication and Information Engineering,Chongqing University of Posts and Telecommunications, Chongqing 400065,China)

:Based on the LTE(long term evolution)CRC(cyclic redundancy check)codes,this paper researched two algorithms which were used very common.It choosed the most suitable CRC algorithm for the TD-LTE test system,and realized the algorithm in the TMS320C64x DSP.The running results of the CRC check program in CCS3.3 verify that the selected algorithm is feasible and effective.

long term evolution;CRC;look-up-table;block-xor long division;DSP Realization

TN929.5

A

0258-7998(2010)09-0071-03

*国家科技重大专项项目“TD-LTE无线综合测试仪表开发”(No.2009ZX03002-009)

2010-04-22)

罗友宝,男,1985年生,在读硕士研究生,主要研究方向:TD-LTE系统物理层算法及 DSP软件开发。

李小文,男,1955年生,硕士生导师,教授,研究员,主要研究方向:TD-SCDMA移动通信系统开发及TD-LTE系统开发。

谷向阳,男,1985年生,在读硕士研究生,主要研究方向:TD-LTE协议栈MAC层协议研究。