BDTI研究认证以DSP为核心的FPGA设计的高级综合流程

2010-10-24伯克利设计技术公司BDTI总裁JeffBier伯克利设计技术公司DSP分析师JenniferEyreWhite

伯克利设计技术公司(BDTI)总裁 Jeff Bier伯克利设计技术公司DSP分析师 Jennifer Eyre White

近年来,高级综合工具(HLST)已成为在设计方案中使用或希望使用FPGA的工程师的必备工具。这种工具以应用的高级表示法(例如用C语言或MATLAB的M语言编写的表示法)为输入,并生成面向 FPGA的硬件实现的寄存器传输级HDL描述。

高级综合工具对两种类型的潜在用户非常有用,一是正在实现高强度数字信号处理(DSP)应用的 FPGA用户,二是正在实现高强度数字信号处理(DSP)应用的高性能DSP处理器用户。这是因为信号处理工作负载非常繁重,通常需要较高的数据速率和高级并行处理能力,这种需求往往适合采用HLST的FPGA来实现。

对目前的FPGA用户来说,HLST工具有望简化并加速设计进程。而对目前的DSP处理器用户而言,HLST则提供了一种独特且相当富有吸引力的作用,无需编写RTL代码就能移植到更强大的处理引擎FPGA上。

过去的高级综合工具都不能生成高效的RTL代码(就资源使用率而言)。大多数工程师都不愿牺牲手编的RTL代码的性能和效率,因此这种工具未能赢得较大市场份额。不过,最近出现的一些新鲜事例显示,面向赛灵思FPGA的新型HLST工具其效率和易用性都非常高。在这种情况下,潜在用户要如何去评判高级综合工具是否有使用价值呢?

为了回答这一问题,独立基准测试与分析公司BDTI于2009年制定了BDTI高级综合工具认证计划。其目标是为FPGA的HLST提供客观可信的数据与分析,确保潜在用户能快速了解其在高强度信号处理应用中的功能及局限性。评估时站在没有FPGA开发经验但却具有丰富DSP软件开发经验的工程师角度,这也反映了大量潜在受益于HLST的处理器用户的实际情况。

最初进行评估的两个HLST程序是Synfora的PICO和AutoESL的AutoPilot。2010年初,BDTI发布了首次评估测试计划的结果,其中的一些结果让许多FPGA和DSP处理器用户都感到吃惊。

采用HLST实现应用

采用HLST实现测试应用的步骤是,先对所需功能进行高级语言描述,高级综合工具由此生成RTL实现。随后赛灵思的RTL工具(集成综合环境(ISE)和嵌入式开发套件(EDK))将RTL实现转化为比特流形式的完整FPGA实现,用于对带有I/O和存储器的特定硬件平台上的特定赛灵思FPGA进行编程。本案例中使用的平台为赛灵思的XtremeDSPTM视频入门套件——Spartan®-3A DSP版本,这是一款基于Spartan-3A DSP FPGA的目标设计平台。

该评估本可以仅限于高级综合工具,忽略设计流程中的“RTL到比特流”部分的评估,但评估者认为,潜在用户应该了解从高级应用描述转变到FPGA实现的整个流程情况,而这项工作需要RTL工具以及高级综合工具,因此还是应对整个实现流程进行评估,不只是“C到 RTL”部分,还包含赛灵思RTL工具链。

在任何硬件目标上实现应用的第一步通常都是重建初始C代码。这里所说的“重建”是指重新编写初始的C代码(初始的代码主要是为了让代码变得更清晰,便于了解,而不是出于性能考虑),将其转变为更适合于目标处理引擎的格式(例如在DSP处理器上重新安排应用的控制流程,确保中间数据始终适应高速缓存要求)。就面向FPGA的高级综合工具而言,重建通常要提供应用表示法,确保工具能提取潜在的并行性,从而优化流水线实现。

一般而言,高级综合工具都不能自动进行重建,而是需要手工重建。事实上,设计人员可以不借助高级综合工具来进行重建。例如,在评估中使用Microsoft Visual Studio重建并验证C代码。相对于重建和语言翻译作为统一步骤出现的手编RTL代码而言,完全用C语言进行重建相对比较简单,出错的可能性也少,这是高级综合工具的一大优势。

重建高级代码后,用户让HLST综合生成RTL HDL代码所指定功能的硬件实现。赛灵思的RTL工具(ISE和 EDK)采用 HLST生成的 RTL代码,执行综合和布局布线任务,报告实现的资源利用率,并通知用户各种时序问题。

BDTI的工具认证计划

BDTI制定高级综合工具认证计划的目标就是进行两大关键点对比,以满足两类潜在HLST用户的需求。首先,希望比较基于HLST的FPGA应用实现和基于手编RTL代码实现的效率,这一信息对目前正在考虑是否要采用HLST加速开发时间的FPGA用户而言至关重要(就资源使用率而言)。其次,希望对用面向FPGA的HLST与用DSP处理器及相关软件开发工具实行同一工作负载时的性能与难度比较。这一对比可帮助DSP处理器用户估算出将技术移植到FPGA设计方案上的难度有多大。

用明确定义的样本应用(即“工作负载”)评估高级综合工具流程(包括相关的RTL工具)。上述应用(下一节将做简要说明)主要代表设计人员通常在FPGA上实现的高强度数字信号处理应用,对数据速率和计算强度均要求高。其他类型的应用产生的结果与这里给出的结果可能会有所不同。

用不同方法实现这两种应用。首先,将高级综合工具与赛灵思RTL工具结合使用,在目标FPGA上实现给定的工作负载。随后,采用传统的RTL设计方法,或者用DSP处理器配合其相关开发工具(取决于具体的工作负载),在相同的 FPGA上实现相同的工作负载。这样就能比较出采用不同工具与芯片组合实现的应用的结果质量与生产力。

评估工作负载

用于评估目的的两个应用是BDTI Optical Flow Workload和BDTI DQPSK Receiver Workload。

“光流法”是指一种分析场景中对象运动和对象特性(如边缘)的视频处理算法。BDTI Optical Flow Workload操作720 p分辨率(1 280×720逐行扫描)的输入视频序列并生成一系列双维矩阵,确定序列中的水平及垂直运动。在设计工作负载时集成了动态数据依赖性决策和阵列索引,从而确保为工具提供严格的测试。

BDTI Optical Flow Workload涉及两个操作点,每个操作点都使用相同的算法,但针对不同的标准优化。操作点1是固定工作负载,定义为60帧/s的720 p分辨率处理视频。其目的就是最大限度地减少实现指定分辨率所需的资源利用率(资源利用率指的是实现工作负载所需资源占可用处理引擎资源的比例)。

与此同时,操作点2的目的则是用所有可用资源来最大限度地提高吞吐量(以每秒帧数为单位)。

第二个工作负载BDTI DQPSK Receiver Workload为无线通信接收器基带应用,其中包含许多无线收发器中的传统通信模块。这是一种固定工作负载,只有一个操作点来处理输入流,输入流为复数调制数据,速率为 18.75 MS/s,接收器链的时钟速率为75 MHz。接收器可生成4.687 5 Mb/s的解调输出比特流。该工作负载的目的是最大限度地减少实现指定吞吐量所需的FPGA资源的使用。

对不同工作负载而言,存储器的使用与存储器的带宽要求差异较大。BDTI DSPSK Receiver Workload只需使用最小的存储器(因此无需外部存储芯片),而 BDTI Optical Flow Workload则需要存储4个视频帧(每帧 1 280×720像素)的历史记录,因此需要外部存储芯片来配合Spartan-3A DSP FPGA。Optical Flow Workload操作点1需要单一外部存储芯片与接口(带宽约为每秒 450 MB),而Optical Flow Workload操作点2通常需要两个外部存储芯片与接口,其带宽之和约为1.4 Gb/s。

就BDTI Optical Flow Workload而言,在典型的FPGA实现中,操作点1每个时钟循环处理一个像素,而操作点2每个时钟循环处理2个像素。BDTI DQPSK Receiver Workload实现每4个时钟循环处理1个输入样品。

度量指标和平台介绍

此前,虽然用手写RTL代码在FPGA上实现的较高要求应用通常能实现更优异的质量(即性能和效率较高),但工作效率不高;而用 DSP处理器实现的应用工作效率虽高,但结果质量差强人意。面向FPGA的高级综合工具旨在提供二者相结合后的最佳水平,既提供较高质量,又实现较高效率。因此在评估中考虑了两组度量指标:结果质量和可用性。

结果质量度量指标用于评估工作负载实现的性能和资源使用情况。BDTI Optical Flow Workload提供HLST-Xilinx流程和DSP处理器流程的结果质量度量指标。BDTI DQPSK Receiver Workload提供 HLSTXilinx流程以及赛灵思根据典型业界设计实践采用手写RTL设计的传统FPGA实现方案的结果流程,其中包括在适当的时候使用赛灵思CORE GeneratorTM知识产权模块。

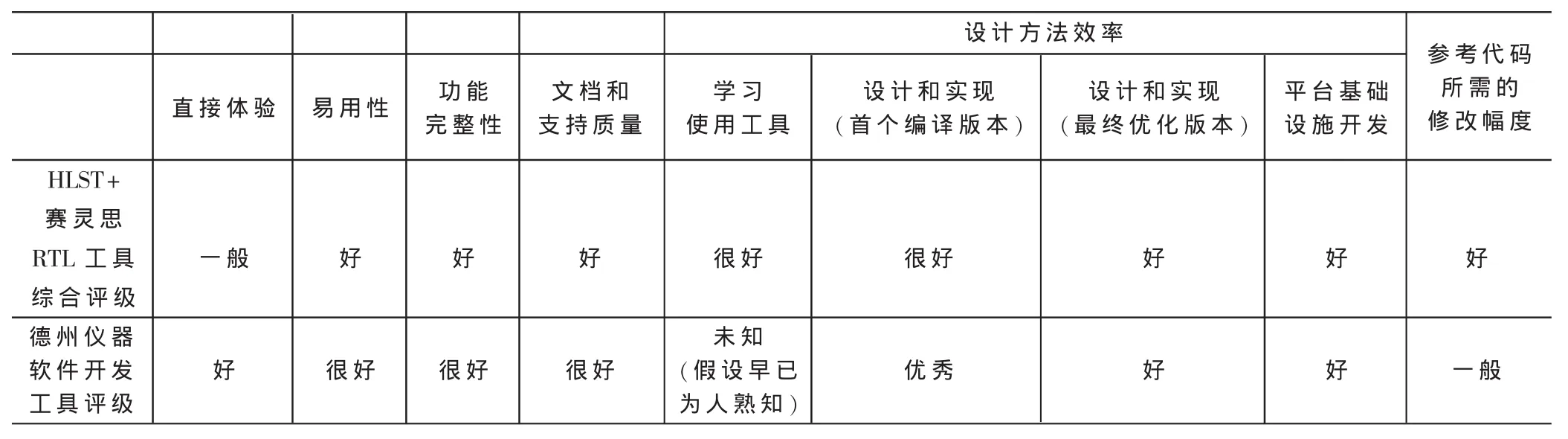

可用性度量指标用于评估HLSTXilinx设计方案的工作效率和易用程度,并以实现BDTI Optical Flow Workload的情况为参考依据。这些度量指标将面向FPGA的HLST和赛灵思工具流相对于使用DSP处理器及其相关软件开发工具链的工作效率和易用性进行比较。根据工具使用的9个方面量化评估可用性度量指标,其中包括直接体验、易用性、工具功能完整性、整体设计方法的效率以及文档与支持质量等。

就本次评估而言,目标FPGA为赛灵思Spartan-3A DSP 3400(XC3SD3400A);就 BDTI Optical Flow Workload而言,赛灵思XtremeDSP Video Starter Kit—Spartan-3A DSP Edition为目标平台。使用了赛灵思RTL工具,包括ISE和EDK工具套件(版本10.1.03,lin64)以及高级综合工具等。

本项目中的目标DSP处理器为德州仪器的TMS320DM6437。这款面向视频的处理器采用600 MHz TMS320C64x+DSP内核以及视频硬件加速器(硬件加速器不适用于 BDTI Optical Flow Workload,因此并未使用)。评估中采用了德州仪器的DM6437 DigitalVideo Development Environment作为目标平台,并采用了德州仪器的Code Composer Studio工具套件(版本为 V3.3.82.13,Code Generation Tools版本为 6.1.9)。

实现与认证进程

将两个工作负载的实现工作分配给两个芯片,并根据使用的芯片和工具链来选择采用赛灵思和BDTI不同的高级综合工具厂商。HLST厂商使用其自有工具以及赛灵思的工具实现两个工作负载,并将性能和资源使用结果提交给BDTI进行验证与认证。利用认证的结果生成了本文的结果质量度量指标。

与此同时,工程师接受了HLST厂商的培训,并分别用高级综合工具和赛灵思工具独立实现了BDTI Optical Flow Workload的某些部分。这一过程为BDTI提供了工具链易用性及其生成结果质量的第一手信息。此外还在DSP处理器上实现了BDTI Optical Flow Workload,而赛灵思则实现手写RTL FPGA版的BDTI DQPSK Receiver Workload(随后也经BDTI验证与认证)。

结果质量:性能和效率

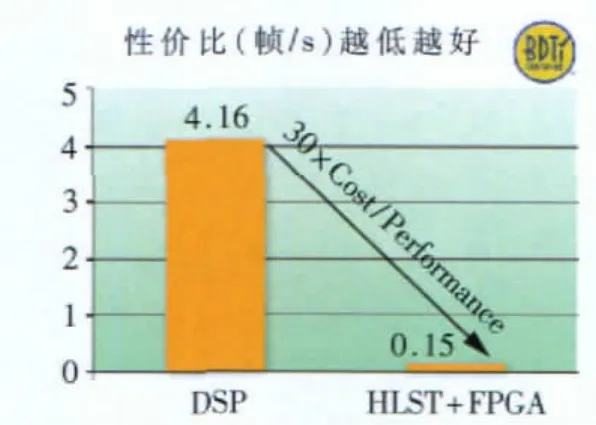

如图 1所示,使用HLST的Spartan-3A DSP FPGA在BDTI Optical Flow Workload视频应用上以720 p的分辨率获得了195帧/s的成绩,而同样情况下C64x+DSP处理器的成绩仅为5.1帧/s。前者的性能比后者高出约40倍。再分析一下芯片成本,图2所示的是相应的性价比优势,Spartan-3A DSP FPGA上使用HLST的BDTI Optical Flow Workload(720p)性价比优于 600 MHz TI C64x+架构的 DSP,FPGA实现方案大约有30倍的优势。显然,配合高级综合工具使用的FPGA能为某些类型的应用提供出色的价性比优势(更多详细结果请参见www.BDTI.com)。

图1 性能比较

图2 成本分析

此外还就BDTI DQPSK Receiver Workload对基于HLST的FPGA实现方案与采用手写RTL实现相同工作负载的效率进行了评估。再次发现,HLST的表现非常出色。如表1所示,AutoPilot和 PICO都能生成效率(即资源使用情况)相当于手写RTL代码的RTL代码。HLST和手写RTL的效率结果相当并非偶然。在评估工作开始时就为AutoESL和Synfora提供了手写RTL实现方案的资源使用示意图,这两家公司可能用该图作为其优化实现方案的目标 (不过我们也应当注意,这种信息并非是高效使用高级综合工具所必需的,而且HLST厂商并未获得RTL设计方案)。

使用AutoESL和Synfora高级综合工具的设计人员确认了资源使用情况的真实性。他们表示该工具所产生的结果优于通过手写RTL代码所能实现的结果,而且还减少了大量设计和验证工作——这是一个巨大的成就。

易用性度量指标

易用性度量指标主要用于评估高级综合工具流程相对于DSP处理器工具链的易用性。对每个易用性度量指标都相应给出优秀、很好、好、一般和差等评分。在打分时,要考虑完整项目的整体设计方法——先是C语言应用规范,最后是目标芯片(FPGA或DSP处理器)上的实时实现。易用性度量指标如表2所示。

表1 BDTI DQPSK Receiver Workload的资源使用情况

表2 HLST和FPGA工具与DSP开发软件的易用性度量指标对比

通常,PICO和 AutoPilot都便于安装和使用,甚至无需FPGA设计经验就能进行。与此形成对比的是,在安装和使用赛灵思的RTL工具时遇到了很大困难,最终还是决定邀请经验丰富的FPGA工程师协助设置运行在FPGA上的设计方案。例如,需要让FPGA工程师解读赛灵思RTL工具发出的错误消息,并将HLST生成的RTL模块与I/O和存储器模块连接在一起,以生成可在FPGA上运行的完整设计方案。总体而言,高级综合工具之外发生的设计问题相当难以解决。如果HLST用户没有RTL设计和工具技能,那么在设计流程的这一阶段就需要具有相关经验的工程师予以帮助。

不过,即便考虑到与流程中RTL-比特流部分相关的挑战,从表2中仍能看出,HLST-Xilinx工具链仍能够实现出色的易用性和生产力业绩,且并不比DSP处理器流程所产生的业绩差。总之,如果有经验丰富的 FPGA工程师帮助开展流程中的某些工作,则可发现在TI DSP处理器上实现 BDTIOpticalFlow Workload的工作量与采用两种HLST在赛灵思FPGA上加以实现的工作量基本相同。

上述结论意义重大,可能会让很多DSP软件工程师感到惊讶。在比较可编程DSP处理器和FPGA的使用时,开发时间对许多系统设计人员来说都是一大障碍。BDTI的评估显示,这种新方法在很大程度上为 BDTI Optical Flow Workload等应用消除了时间障碍。

HLST:规则改变者

BDTI早先对FPGA和DSP处理器进行的基准测试 (发表于2007年的“用FPGA完成DSP工作任务”报告中)显示,用传统RTL设计方法实现FPGA时,FPGA在某些应用中具有较大的性能和性价比优势。新的分析结果确认了上述性能优势,这表明FPGA配合使用高级综合工具也可实现类似的性价比优势。此外还发现,目前所评估的两种高级综合工具——Synfora的PICO和AutoESL的AutoPilot所实现的资源使用效率相当于通过手写RTL代码所实现的效率。尽管没有直接评估HLST相对于手写RTL代码的时间节约优势,但根据对目前HLST用户的采访结果可以相信时间方面的优势也会相当显著。

用传统手写RTL编码创建的FPGA设计方案通常比DSP处理器上用软件实现的同类应用花费更加多的工作量,这较好地解释了很多DSP处理器用户不愿意改变工作方法的原因。因此,本项目最令人惊讶的结果或许就在于,在FPGA上(用AutoPilot或PICO配合赛灵思工具)实现评估工作负载与使用DSP处理器所需的工作量基本相当。

对FPGA用户而言,我们的研究充分说明HLST可在无显著负面影响的情况下提升生产力。而对于DSP处理器用户,FPGA显而易见确实值得考虑,HLST正快速成为改变格局的重大技术。