基于SPARC V8结构处理器的计算机系统设计

2008-12-19施蕾,刘波,周凯

施 蕾,刘 波,周 凯

(1.北京控制工程研究所,北京 100190;2.国防科技大学,长沙 410073;3.中国空间技术研究院总体部,北京100094)

基于SPARC V8结构处理器的计算机系统设计

施 蕾1,刘 波1,周 凯2,3

(1.北京控制工程研究所,北京 100190;2.国防科技大学,长沙 410073;3.中国空间技术研究院总体部,北京100094)

首先介绍了国内外计算机SPARC体系结构的研究现状,指出SPARC体系结构已成为国际上流行的处理器结构之一,而且众多航天机构也采用了SPARC结构的处理器设计其航天器的计算机系统。随后,着重说明了SPARC V8的组成结构以及国内外基于SPARC V8结构设计实现的处理器。最后给出了基于国产SPARC V8结构处理器BM3802设计实现的最小系统组成结构。

SPARC结构;SPARC V8处理器;体系结构;最小系统

1 引 言

半导体工艺的飞速发展,以及深亚微米工艺加工技术的不断提高,使整个系统设计集成到单一芯片上的实现成为可能,这种系统集成技术统称为系统芯片(SOC,system on chip)技术。针对卫星设计来说,SOC技术是一种高度集成化的系统集成技术。利用系统集成技术可以将卫星的传感器信号处理、数据采样和处理、姿控、上下行通信、有效载荷数据处理和控制、故障检测和容错管理等功能进行合理划分,把系统集成为几个标准化的功能模块,并且通过自顶向下的电子设计自动化技术(EDA,electronic design automation),把功能模块尽可能的集成在一块芯片上。采用SOC技术后,不仅可以满足卫星的小型化需求,而且还能同时提高系统的性能和可靠性,适应设计复杂、要求严格的航天控制系统。

SOC技术为工程师们提供了一个快捷、经济的系统设计方法,使嵌入式结构摆脱了以往系统设计时高性能与高成本并存等缺点的束缚。达到了工程师通过低成本单片芯片,实现高性能系统的目的。目前,通过SOC技术实现系统设计已成为集成电路(IC)设计及嵌入式系统发展的趋势和主流。

基于 SPARC(scalable processor architecture)V8结构的高性能32位处理器,已在SOC设计领域中得到广泛地应用。本文介绍了采用基于SPARC V8结构的国产处理器BM3802设计所实现的最小系统。

2 SPARC系统的发展现状

1985年Sun系统公司为了获得更高的执行效率和更优化的编译器,并满足缩短开发周期,迅速投放市场的要求,提出了SPARC体系结构。SPARC体系结构是一种精简指令集计算机(RISC,reduced instruction set computers)类型的中央处理器(CPU,central processor unit)指令集体系结构[1]。

1987年SUN和TI公司合作开发了基于SPARC结构的微处理器。于1989年成立专门负责SPARC体系开发认证的国际组织。SPARC体系结构是一种可以随着工艺技术的改进,来成比例提高自身性能的处理器结构。而且SPARC体系结构采用了一种开放式的体系结构标准,任何企业或个人都可以根据这个标准来设计和开发微处理器和半导体器件。

上个世纪末,欧空局为了摆脱对美国高性能、高可靠性处理器的依赖,利用SPARC V7结构,加入了抗幅加固工艺的处理,开发出了面向空间应用的TSC695F处理器。目前,SPARC结构已经从最早的32位SPARC V7结构,经过32位SPARC V8哈佛结构,发展到了目前的64位 SPARC V9超标量结构,使SPARC体系结构的微处理器得到了更为广泛的发展。

目前,中国航天领域的计算机系统,广泛采用了基于SPARC V7结构实现的TSC695F处理器。关注SPARC体系结构的发展,有利于中国航天领域系统设计的技术更新。

3 SPARC V8结构

SPARC体系结构是一种CPU的指令集结构,它是微处理器精简指令集结构的一个分支。其设计的指令集能提高执行的效率以及优化编译器生成的代码,从而使代码执行起来更为高效、快速。

SPARC体系结构采用了一种基于“寄存器窗口”的系统结构,这种系统结构对于用户程序、特别是很大的应用程序,能够使编译器生成更直接、更高效地优化代码。相对于其他 RISC结构来说,这种窗口结构尽量减少了存储器装载/存储指令,加快了代码执行的速度。对于像C++这种以面向对象为主的编程语言来说,“寄存器窗口”这种结构能更好地优化可执行代码。当在操作系统下运行时,各进程之间在这种结构下能更快地进行上下文切换[2]。

SPARC体系结构具有如下特点:

1)统一格式的指令译码;

2)指令规整、对称、简单;基本寻址方式有2~3种;3)大部分指令都是单周期指令五级流水线;4)使用海量寄存器(“寄存器窗口”的系统结构);

5)只有LOAD/STORE指令能够访问存储器。

3.1 SPARC V8指令系统

SPARC V8支持10种数据类型。整数类型包括有符号整型字节、有符号整型半字、有符号整型字、无符号整型字节、无符号整型半字、无符号整型字、双字和带标志字。浮点类型包括单精度浮点数和双精度浮点数。

SPARC是一个大端模式体系,一个双字,单字或者半字的地址是它最高字节的地址。最高位的字节通常存储在最低的地址位上。

处理器通过从存储器上读取指令来执行操作、取消操作或者执行中断。这些指令总共可以分成6类:LOAD/STORE、算术/逻辑/移位、控制转移指令、读写状态寄存器指令、浮点运算指令和协处理器运算指令。一共有72个基本的指令操作码。

SPARC V8目标码和V7目标码唯一的区别是:编译器生成整数乘法和整数除法指令,SPARC V8支持该指令,而 V7体系不支持。DIV除法指令、MUL指令乘法指令、MAC指令乘法和累加指令是SPARC V8特有指令。

3.2 SPARC V8寄存器

SPARC V8寄存器包括两种类型的内部寄存器:控制/状态寄存器和通用寄存器。

3.2.1 控制/状态寄存器

32位的整数运算单元(IU)控制/状态寄存器包括:程序计数器(PC,nPC)、处理器状态寄存器(PSR)、窗口无效标志寄存器(WIM)、异常基址标志寄存器(TBR)和乘法/除法标志寄存器(Y),用户可以通过这些硬件寄存器了解处理器的工作状态。

1)程序计数器

32位的PC包含IU当前执行的指令地址。nPC包含下一条指令的地址(假设异常没有发生)。PC由CALL或者JMPL指令读出,当一个陷阱产生时,PC和nPC的值就会被写入两个局部寄存器内。

2)处理器状态寄存器(PSR)

处理器状态寄存器PSR除了包括反馈处理器操作状态的信息外,也包括了控制处理器操作的各项信息。它可被SAVE、RESTORE、TICC和RETT指令修改,同样可以被其他可修改PSR状态位的指令修改。例如特殊的RDPSR和WRPSR指令等。

3)窗口无效标志寄存器(W IM)

窗口屏蔽寄存器用来指定当CWP(当前窗口指针)指向哪个窗口时,会引起上溢或下溢陷阱产生。即每一个寄存器集或者一个寄存器窗口在W IM中都有一个相应的状态位。

4)异常基址标志寄存器(TBR)

异常基址寄存器TBR包含三个字段。当异常产生时,将异常基址寄存器TBR的内容送入程序计数器PC中,以实现向陷阱处理程序的传输控制。

5)乘法/除法标志寄存器(Y)

乘法/除法标志寄存器(Y)用来保存整型乘法指令(如 SMUL、SMULCC、UMUL、UMULCC)和 整型乘法指令(MULSCC)双精度结果中的高32位,同时还将保存整型除法指令(SDIV、SDIVCC、UDIV、UDIVCC)双精度被除数的最高字。

3.2.2 通用寄存器

SPARC V8含有32个32位的通用存储器。

3.3 SPARC V 8处理器

3.3.1 BM3802 32位空间嵌入式处理器

BM3802是由航天某研究所自主研制的一款基于SPARC V8结构的AMBA总线的高性能32位RISC嵌入式处理器[3]。

BM3802是采用以 32位整数和 32位、64位IEEE-754标准浮点数为基本数据类型的指令集结构。它定义了通用整数、浮点数、特殊状态寄存器和72个基本指令操作,译码都是32位宽的指令格式。处理器包括整数单元、浮点处理单元、AMBA总线、独立的指令Cache和数据 Cache、硬件乘法器和除法器、存储器控制器。为了实时应用,处理器提供了一个看门狗、两个定时器、一个中断控制器和两个串口通信控制器。另外,处理器具有检错和纠错功能,适合恶劣环境应用,具有低电路复杂度和低功耗的特点。处理器支持嵌入式操作系统,包括uclinux和 RTEMS。

BM3802提供了大量系统支持功能的嵌入式处理器,只要加上存储器和与应用相关的专用外围电路,就可以构成完整的板上计算机。

3.3.2 SAILING S698处理器

SAILING S698处理器(以下简称S698处理器)是国内针对嵌入式实时控制及信息处理应用而研制的32位RISC嵌入式处理器,其设计遵循SPARC V8标准[4]。

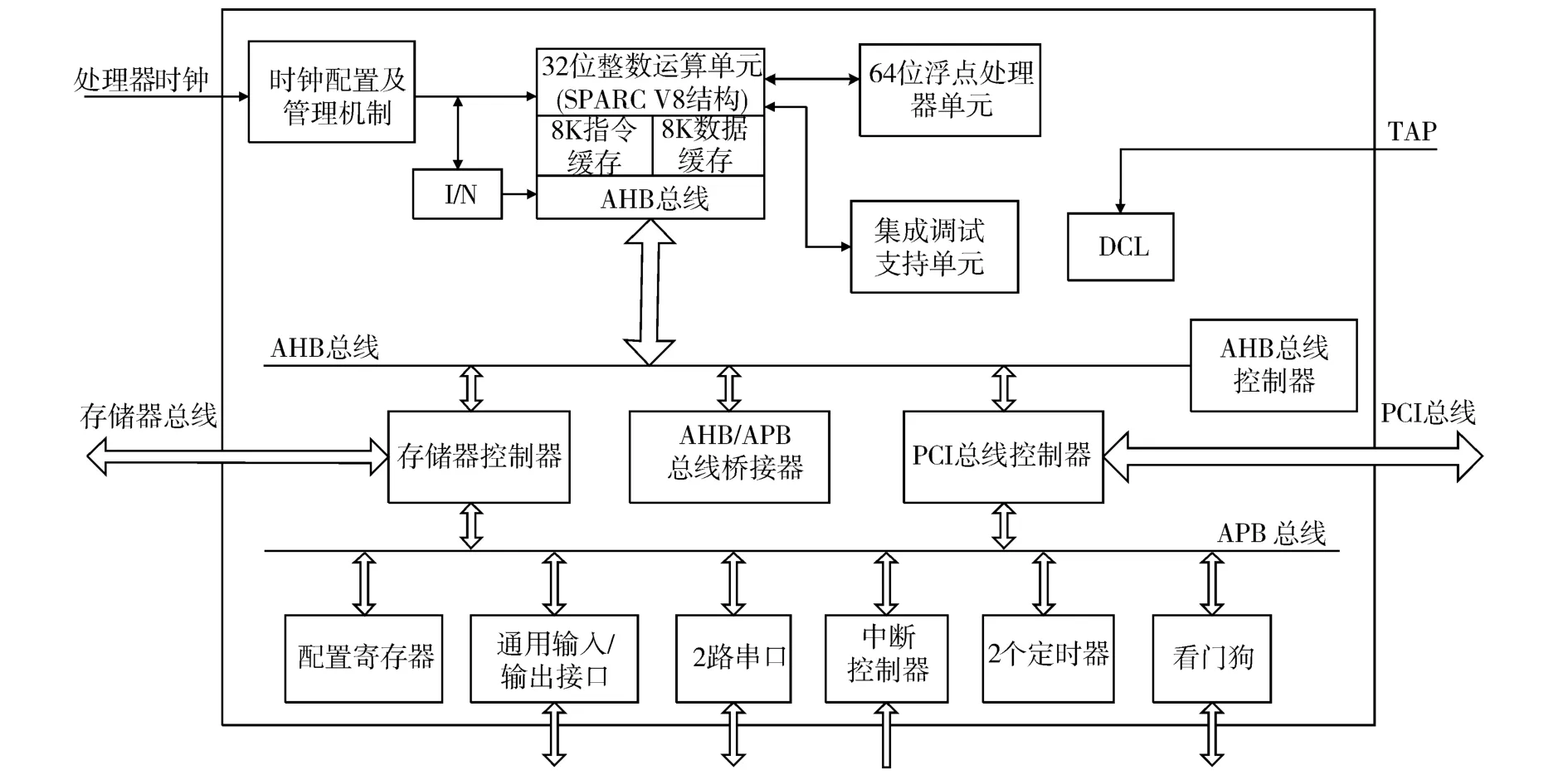

S698处理器内嵌符合 IEEE-754标准的64位浮点运算器(FPU),采用AMBA总线作为片内系统架构总线,片上各模块通过AMBA总线进行数据交换和通讯。AMBA总线配置了PCI总线接口、存储器总线接口、UART、定时器、中断管理器、I/O、看门狗、配置寄存器等,使得S698芯片的集成度和功能得到了大幅度的提高。S698处理器内部结构框图[4]如图 1所示。

图1 S698结构图

S698处理器具备硬实时处理能力,完全支持ORBITA实时嵌入式操作系统ORBITA EOS、实时嵌入式操作系统RTEMS以及嵌入式操作系统uclinux。基于S698处理器芯片,利用其完整的软硬件开发系统,用户可以轻便地设计各种各样的嵌入式应用系统,包括 PC/104主机板、VME主机板、CPCI主机板等。S698还可以应用于高端工业控制、消费电子、航天计算机等领域。

3.3.3 具有抗辐射能力的32位SPARC处理器AT697

2005年,Atmel公司推出了具有加固能力,适用于空间领域应用的32位SPARC V8处理器AT697。与前代SPARC处理器相比,AT697在封装尺寸减小3倍的同时,还将速度与功耗比提高了8倍,有效地提升了计算能力。

AT697软件与 SPARC V7 TSC695F等前代SPARC处理器兼容。这样工程师可以重新使用前代SPARC处理器开发的任何软件来发挥AT697的高性能。AT697处理器采用欧空局(ESA)的LEON2 FT(容错)VHDL模型,采用 Atmel的0.18μm CMOS工艺制造。它包括一个 SPARC V8整数单元、浮点单元、分离指令和数据缓存、PCI接口及灵活的存储器控制器与 SRAM、PROM和SDRAM连接。

AT697的内核及I/O缓存分别采用1.8V和3.3V电源,100MHz时速度达86MIPs和23MFlops。性能与能耗比为150MIPs/W,功耗为7mW/MHz。

AT697处理器采用陶瓷密封MCGA 349引脚封装,可独立使用,该封装适合太空产品使用,无论是大小、重量还是热敏感度均优于扁平四方封装。

AT697处理器不仅具有高可靠、高性能和低功耗等优势,而且可以兼容基于TSC695F处理器开发的所有软件,但由于受供货渠道的限制,目前仅能拿到 AT697的样片[5]。

3.3.4 处理器性能特点比较

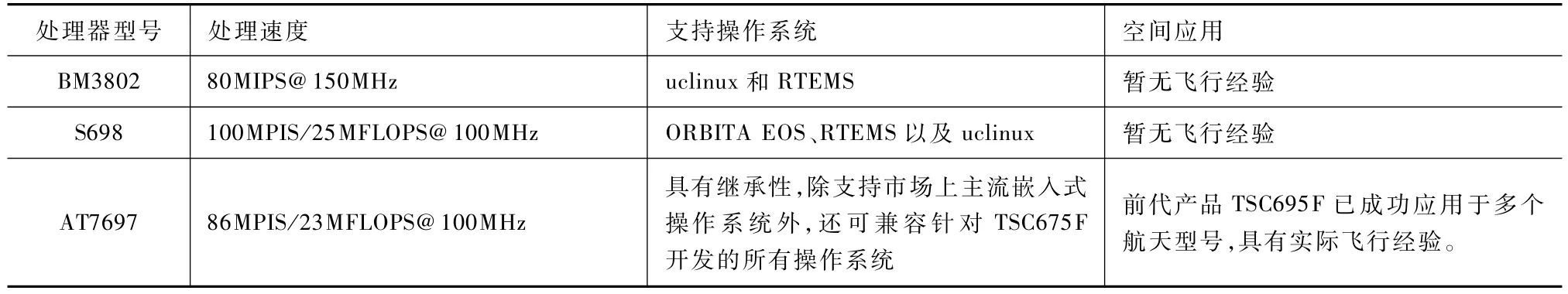

前3节分别介绍了3种主流的SRARC V8结构处理器,表 1[3-5]针对其各项性能、特性进行了总结。

表1 基于SPARC V8结构处理器的性能和特性分析表

4 基于SPARC V8处理器的应用设计

在整个系统的开发过程中,包括了硬件设计、底层软件支持库、驱动程序、操作系统和上层应用程序等部分,本节只对系统的硬件设计进行简要介绍。

4.1 项目需求

项目设计要求主处理器使用32位RISC CPU,时钟周期大于100MHz,运算能力大于30MIPS。选择采用基于SPARC V8结构、具有浮点运算能力的处理器,即可满足系统对CPU的性能参数的要求。系统要求配置128MB数据存储器,2MB程序存储器。

目前国内星上使用的处理器性能较低,而且依赖于进口,无法满足航天器设计实现自主化研制的需求。为了改变这一现状,系统打算以国内自行开发、研制的BM3802处理器为核心,设计实现能够在外层空间环境下正常工作、在宇宙线照射条件下不出现暂态误动作的、以容错功能为主导的计算机体系结构。从而为以后大卫星的研制提供有利的保障和坚实的基础。

BM3802是基于SPARC V8结构的、AMBA总线的高性能32位RISC嵌入式处理器。

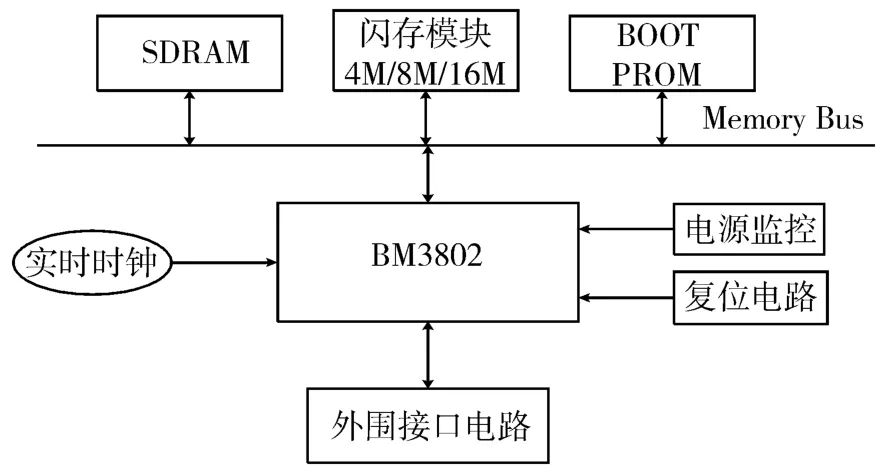

此处理器是一个高性能的32位嵌入式的处理器,它具有低电路复杂度和低功耗的特点。处理器包括整数单元、浮点处理单元、AMBA总线、独立的指令Cache和数据Cache、硬件乘法器和除法器、存储器控制器。BM3802结构[3]如图2所示。

4.2 系统设计

系统硬件设计采用以SPARC V8结构为核心的国产 BM3802处理器,主要由 BOOTROM、FLASH、SDRAM、复位电路、电源电路和外围接口电路等组成。BOOTROM中存入系统的引导程序,使系统可以在没有操作系统的支持下,构建出最简单的软件运行环境,可以在系统上电后直接运行。最小系统的结构框图如图3所示,板级实物图如图4所示。

图3 SPARC结构最小系统示意图

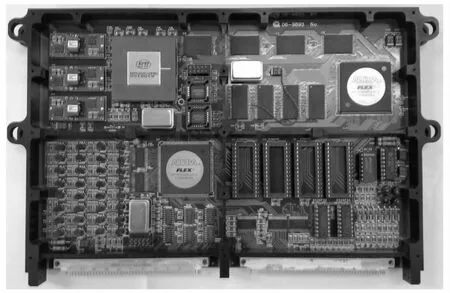

图4 以BM3802处理器为基础设计实现的板级实物图

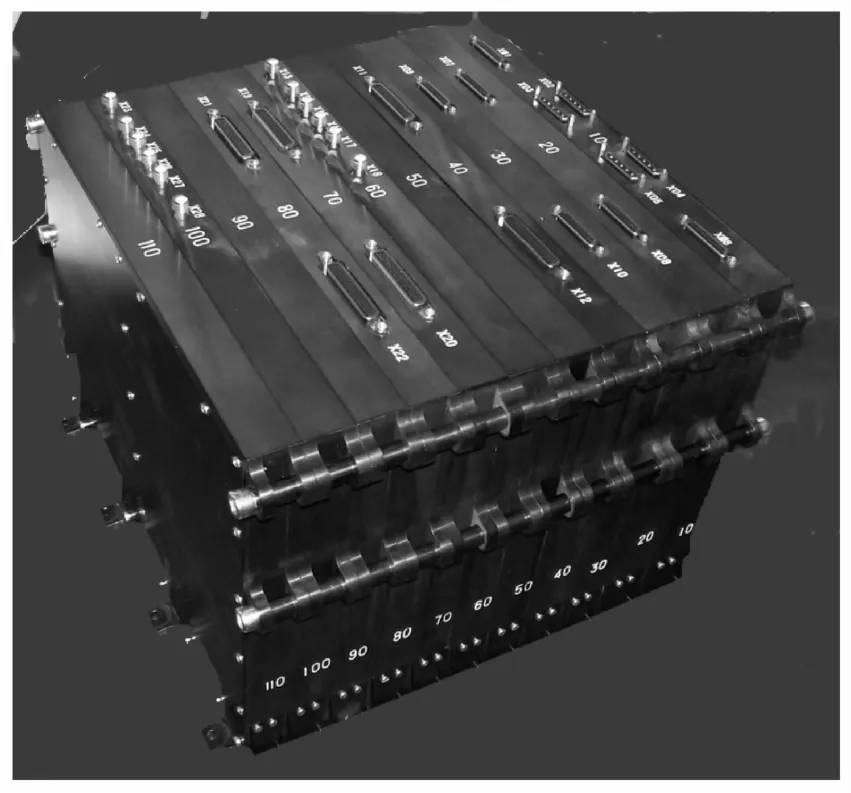

目前,以该最小系统为基础设计实现的卫星综合电子系统已完成了一期阶段的研制、生产与调试工作,项目成果见图5。

5 结束语

目前,中国在航天系统应用研究中普遍采用了SPARC体系结构作为航天器计算机系统设计的基础,可以说SPARC体系结构已成为航天器系统设计的一个新热点。SPARC V8采用一种开放的体系结构标准,它作为芯片制造和应用的桥梁,一方面反映了在芯片上集成系统功能的工艺技术已经日趋成熟,另一方面也从根本上促进了高性能系统的研制和开发。尤其是在航天领域,体系结构的合理性和先进性与系统的各项性能指标是直接相关的,直接决定了系统的可使用性能。

图5 综合电子系统一期实物图

目前,在综合考虑卫星、飞船和空间站等航天飞行器对微处理器的需求以及国内外研究状况等各种因素的前提下,将SPARC V8设计思想渗透到实际的体系结构研究和应用中,对中国航天乃至整个计算机领域的发展都会起到促进作用,也为中国的航天器设计工作提供更为广阔的发展平台。

[1] 范建民.基于SPARC V8的RISC处理器中IU的设计和研究 [D].华南理工大学硕士论文,2005

[2] Gaisler J.A portable and fault-tolerantmicroprocessor based on the SPARC v8 architecture[C].Proceedings of International Conference on Dependable Systems and Networks,Washington,DC,USA,2002

[3] BM3802 32位空间处理器用户手册[M].中国航天时代电子公司,2005,4-49

[4] 蒋晓华,李付海,祁波.SPARC体系的S698系列SOC及其应用[J].单片机与嵌入式系统应用,2007,(8):84-85

[5] Gaisler R.LEON2 processor user'smanual(XST Edition)[M].北京:国防工业出版社,2005,36-207

The Com puter System Design Based on the SPARC A rchitecture Processor

SHI Lei1,LIU Bo1,ZHOU Kai2,3

(1.Beijing Institute of Control Engineering,Beijing 100190,China;2.Graduate School of National University of Defense Technology,Changsha 410073,China;3.China Academy of Space Technology,Beijing 100094,China)

This paper specifies the development of SPARC architecture and addresses the design of computer systems for spacecraft based on SPARC architecture.This paper puts emphasis on the details of SPARC V8 architecture and lists the processors by using SPARC V8 architecture.Finally it raises a processor system designed with the indigenouschip BM3802.

2007-11-26

施蕾 (1980-),女,北京人,工程师,研究方向为星载计算机设计(e-mail:shi_sissa@163.com)。

SPARC architecture;SPARC V8 processor;systematic structure;minimum system

V446.2

A

1674-1579(2008)03-0046-05