基于FPGA 的图像上采样IP 核设计与实现

2024-07-24李京安杨越程刘宇晨康子律

摘要:随着人们对图像信息处理的要求不断提高,图像上采样算法的研究成为当前热点,而算法的硬件化实时性发展趋势,使得提升图像处理质量的同时减少硬件开销成为一个难点问题。本文通过对基于FPGA的双线性插值上采样算法进行优化,实现了图像的4倍放大功能,实验结果表明,上采样算法功能正确,开发板资源消耗较少,为图像放大实时性要求高的应用场合提供了解决方案。

关键词:FPGA;图像上采样;双线性插值算法

中国分类号:TP391.41 文献标识码: A

文章编号:1009-3044(2024)17-0043-03 开放科学(资源服务)标识码(OSID) :

0 引言

随着电子技术的飞速发展,人们对视频图像质量的要求不断提升,如何处理超大数据量的图像数据并提高响应速度已成为图像处理领域研究的热点。图像缩放技术通过将高分辨率(High-Resolution, HR) 图像下采样为低分辨率(Low-Resolution, LR) 图像,减少系统处理的数据量和响应时间,然后通过上采样技术还原HR图像显示。目前,图像缩放技术已在GPU中广泛应用,从NVIDIA的DLSS到AMD的FSR,上采样算法成为其研究重点,并在无人机、智能驾驶、安防监控、遥感、医疗等领域有着广泛的应用。

为了满足图像处理的实时性需求,越来越多的图像处理算法采用硬件系统实现。FPGA以其并行性和可重构特点,为图像处理算法的硬件实现提供了更好的灵活性。本文基于FPGA技术,以Zedboard开发板为硬件平台,通过对几种插值算法的分析比较,实现了双线性插值图像上采样算法IP核设计。最终,以将960×540分辨率图像放大4倍至3 840×2 160分辨率为例,验证了该IP核的有效性及性能。

1 图像上采样算法

图像上采样也称为超分辨率重建技术,即将低分辨率(LR) 图像经过处理转换成高分辨率(HR) 图像的方法[1]。目前,国内外对上采样算法的研究主要分为三类:基于插值、基于重构和基于学习的算法[2]。基于插值的上采样算法通过在原始LR图像像素点间插入新像素点补充成HR图像,主要包括最近邻插值、双线性插值、双三次插值等线性插值算法,以及边缘导向插值、小波变换插值等非线性插值算法;基于重构的上采样算法利用多幅LR图像与未知HR图像提取所需的图像特征信息,估计HR图像特征信息后重建HR 图像,主要包括非均匀内插法、迭代反向投影法、凸集投影法、最大后验概率法等空域法和频域法;基于学习的上采样算法通过对给定图像数据集中特征信息的集中学习,建立LR和HR图像序列的先验关系,再通过超分辨率图像重建算法实现图像重建,目前主要包括基于卷积神经网络的SRCNN[3]和对抗神经网络SRGAN[4]算法等。

由于FPGA本身的LUT门数资源限制,在处理复杂算法时存在算力不足的问题,当前主要采用基于插值的上采样算法。因此,本文在VS2019环境下,以C 语言编程实现了最近邻插值、双线性插值、双三次插值等插值算法的软件模拟。结果表明:最近邻插值算法简单,但放大后图片肉眼可见的锯齿感和块状模糊现象严重;双三次插值较双线性插值在PSNR和SSIM 参数上略有提高,但在LPIPS参数上略有不足。虽然双三次插值的图片质量较好,并且边缘失真现象有所缓解,但算法复杂性明显增大,运行时间约增长20倍;双线性插值算法相对简单,图片质量基本得到保证。因此,选用双线性插值算法作为本设计的实现算法。

双线性插值算法如图1所示,其基本思想是利用周围最近四个点的值做三次线性插值。首先在水平方向做两次线性插值得到两个点的像素值R1和R2,然后利用R1和R2在竖直方向做一次线性插值,即可估算出P点处的值作为新插入的像素点。P点处的线性插值计算公式如式(1) 所示。

2 基于FPGA 的图像上采样系统设计与实现

2.1 总体架构图

本系统的主要功能部件包括ARM Cortex-A9核、 上采样IP核模块、DDR3控制器、AXI SmartConnect总线模块、SD卡及Fat文件管理系统、按键检测模块、HDMI显示模块等,系统总体架构如图2所示。

本系统的SoC整体部署在Zedboard开发平台,并在SDK环境下创建板级支持包和FAT文件管理系统。PS端利用文件管理函数从SD卡中读取图片像素矩阵数据并存储在DDR3中。当外部按键被按下时,上采样IP核开始工作,通过datamover模块和总线模块从DDR3中获取像素数据进行处理,处理完成后再将像素数据写入DDR3中。其中,datamover和IP接口遵循AXI-Stream 协议。当一张图片处理完毕后,通过HDMI接口协议将处理后的图像显示在显示器上,并存储在SD卡中。

2.2 上采样IP 核设计

双线性插值算法的硬件实现面临两个问题:1) P 值运算涉及大量除法和乘法操作;2) 当两个像素之间的距离视为1时,公式(1) 中的分子都是浮点数。在FPGA中实现乘除法运算和浮点数运算非常浪费资源,设计也较为复杂。因此,从以下两个方面进行优化。

2.2.1 双线性插值算法公式化简

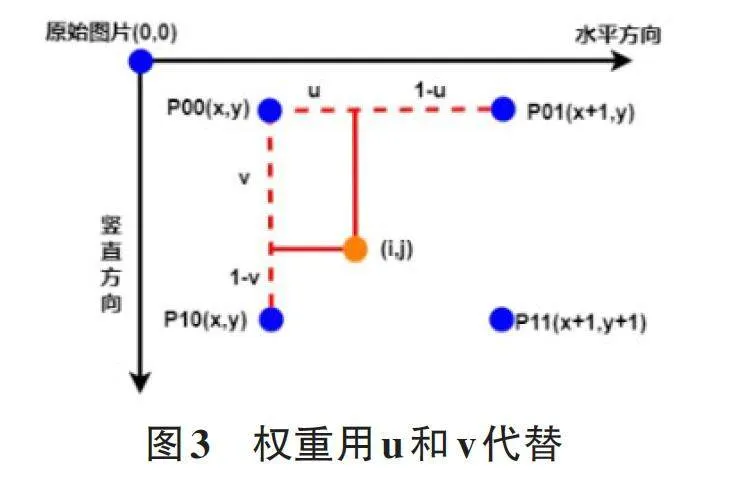

首先,相邻两个像素点之间距离视为1,即x2-x1=1,y2-y1=1,则消除了分母,减少除法;其次,在权重表示上如x2-x 和x-x1可以分别用u 和1-u 代替,y2-y 和y-y1分别用v 和1-v 代替,如图3所示。

公式简化结果如式(2) 所示:

R(i,j ) = P00(1 - u)(1 - v)+P01u (1 - v)+P10(1 - u)v+P11uv (2)

2.2.2 FPGA 自动生成权重

本文拟在上采样部分将图片分辨率放大4被,即相当于目标图片到原始图片缩小4倍。如果目标图片某一个像素点(i,j) 在原始图片中对应的位置为(x,y) ,则x=i×1/4,y=j×1/4。因为放大在水平方向和竖直方向放大倍数一样,此处以水平方向为例进行说明,水平方向原始图片与目标图片像素值的对应关系如图4 所示。

水平方向上目标图片像素点到对应原始图片最左边像素点的距离,随着目标图片像素点的递增存在周期为4的变化规律0à1/4à2/4à3/4à0à1/4à…,即式(2) 中u 的变化规律,竖直方向变化规律相同。而此时u 和v 虽然都是分母为4的浮点数,将分母4提到公式前得到最终化简结果,如公式(3) 所示。此时u、v变化规律为0à1à2à3à0à1,乘法变成了整数与整数相乘,而分母4×4则可利用右移寄存器实现,简化了计算步骤。

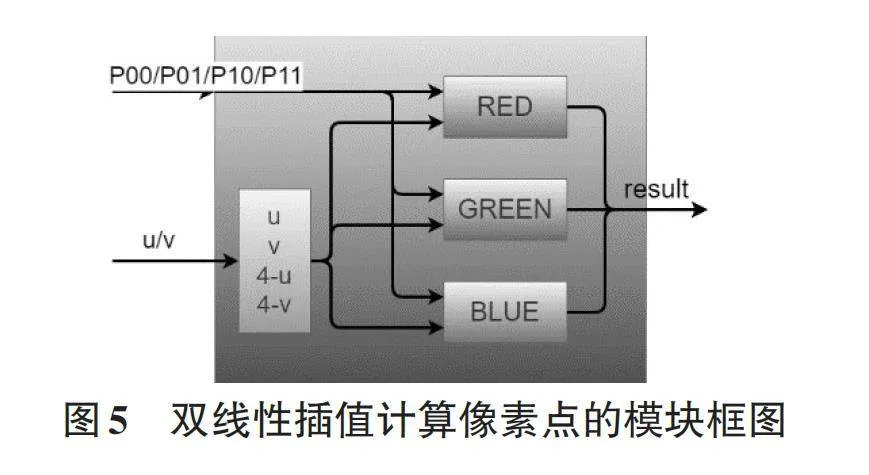

插值计算模块设计如图5所示,模块整体输入为四个像素点的像素值P00/P01/P10/P11和权重u/v,每个像素点由R、G、B三基色组成,设置RED、GREEN、BLUE三个通道利用双线性插值算法分别计算R、G、像素值,最后通过信号合并把R、G、B像素值合并成新像素点result输出。

2.2.3 IP 核实现架构

上采样模块IP 核微架构如图6所示,主要包括stream 模块、控制原始图片数据行缓存模块sur_row_ctrl、插值计算模块ctrl_pixel、控制目标图片行缓存模块des_row_ctrl和目标图片行缓存状态模块state。

按键按下时,sur_row_ctrl模块向stream模块发起读数据请求,随后stream 模块向总线发起读数据请求,从总线读取到的数据被返回给sur_row_ctrl模块。该模块按一定顺序将数据存储在片上存储资源sur_row_bram 中。存储完两行原始图片数据后,sur_row_ctrl模块向ctrl_pixel模块发出开始计算信号。ctrl_pixel模块接收开始计算信号后,从sur_row_bram 中读取这两行数据,开始插值计算,并将计算结果写入des_row_ctrl模块。在插值计算过程中,ctrl_pixel模块和des_row_ctrl模块既可以更改state模块状态,也受state模块的约束。des_row_ctrl模块中目标图片的行缓存按乒乓原理存储[5],state模块表示目标图片行缓存的状态。当des_row_ctrl 模块存储完四行数据后,向stream模块发起写数据请求。stream模块接收请求后,向总线发起写数据请求,总线收到请求后将目标图片行缓存中的数据存储到DDR3中。整个上采样IP核一边从DDR3中读取数据并处理,一边将处理好的数据写入DDR3中,直到处理完一张图片后结束。

2.3 系统仿真验证

设计了testbench文件来验证上采样IP核。该IP 核的接口部分主要采用AXI-Stream协议,除一个执行信号外。testbench 文件通过设置合理的输入,观察datamover 端口信号的变化情况,以验证结果的正确性。

3 实验结果分析与总结

3.1 实验结果

将生成的BMP格式LR图片保存在SD卡中,并通过上采样IP核在FPGA板上进行验证。图像分辨率由原始的960×540放大到3 840×2 160。放大后的图像与原始图像一致,如图7所示,实验结果正确。

3.2 总结

基于双线性插值算法的FPGA上采样IP核实现了原始图像的4倍放大功能,放大后的图像内容一致。该IP核在Zedboard开发板上的硬件实现,在工作频率为250 MHz的情况下,处理一张图片需要24 ms,板上资源消耗为6 528 个LUT、7 890 个FF 和41.5 个BRAM36K 储存资源。该系统通过对双线性插值公式简化和计算权重去浮点处理,减少了系统运算量,加快了运行频率,实现了图像上采样功能。该方案为图像放大实时性要求高的应用场合提供了解决方案,但仍存在边缘模糊问题,有待进一步解决。

参考文献:

[1] 张芳,赵东旭,肖志涛,等.单幅图像超分辨率重建技术研究进展[J].自动化学报,2022,48(11):2634-2654.

[2] 钟梦圆,姜麟.超分辨率图像重建算法综述[J].计算机科学与探索,2022,16(5):972-990.

[3] DONG C,LOY C C,HE K M,et al.Learning a deep convolutional network for image super-resolution[C]//European Conference on Computer Vision.Cham:Springer,2014:184-199.

[4] LEDIG C,THEIS L,HUSZÁR F,et al.Photo-realistic single im⁃age super-resolution using a generative adversarial network[C]//2017 IEEE Conference on Computer Vision and Pattern Recog⁃nition (CVPR).Honolulu,HI,USA.IEEE,2017:105-114.

[5] 张弘.基于FPGA的视频图像处理的研究与实现[D].成都:电子科技大学,2020.

【通联编辑:梁书】

基金项目:湖北工业大学大学生创新创业项目(S202310500110) ;湖北工业大学教学研究项目(校2018027)