玻璃通孔(TGV)技术的前景及机遇

2024-05-29

近期,玻璃基板概念横空出世,通达信及东方财富Choice 等行情软件均推出相关概念板块及指数,原因是“大摩爆料GB200 将使用玻璃基板”及“英特尔加大了对多家设备和材料供应商的订单,积极备战下一代先进封装的玻璃基板”等消息的共振。

实际上,我们经过深入研究发现,按照上述多重消息的指向,该玻璃基板概念实际上指的是用于半导体封装过程中的转接板之用,利用玻璃通孔(TGV)技术来实现芯片电路连接,实现2.5D/3D 封装,以满足AI+Chiplet 趋势化需求。需要注意的是,目前市场火热的玻璃基板概念股,有的是与显示相关,有的甚至纯粹是炒作,真正用于半导体封装的产业链产品并不多。本期封面文章我们就将简明扼要地对TGV 技术做介绍和分析,希望对各位读者辨别“ 李逵”和“ 李鬼”有所帮助。

2.5D/3D封装工艺中的TSV技术

我们都知道,要实现芯片性能的提升就需要堆叠更多的晶体管,根据“摩尔定律”,芯片上容纳的晶体管数目每18 到24 个月增加一倍。近几十年来,随着“摩尔定律”的发展,由于单位面积堆叠的晶体管越来越多,因此芯片得以不断微型化,这造就了诸多便携式电子产品的问世,如智能手机、电脑、笔记本等等。

但“摩尔定律”终有触及天花板的时候,自从晶圆制造进入14nm、7nm、5nm 直至最新的3nm 工艺,“摩尔定律”的有效性越来越受到挑战:工艺进步越来越难,性能也提升有限,且成本上升巨大。

随着近两年来AI 的火热,AI 服务器对于算力的需求出现井喷,而强大的算力当然需要强大的芯片,那么强大的芯片只能通过不断进步的光刻工艺吗?当然不是,由于目前的芯片已经非常很微型化了,加上服务器并不像消费电子那样对轻薄化要求那么高,另一条思路就诞生了——堆叠更多芯片在一起达成算力提升。打个不是很形象的比喻就是一节火车头不够用那就多加两节,犹如詹天佑当年的解决思路。

由此产生了问题,芯片堆叠如何实现?

也因此,对于封装技术又有了新的要求,以期可以实现更高的I/O 密度、更快的信号传输速度和更好的电热性能,从而提高芯片的性能和功能。并且,还需要兼顾降低芯片的功耗和体积,提升芯片的可靠性和生产效率。

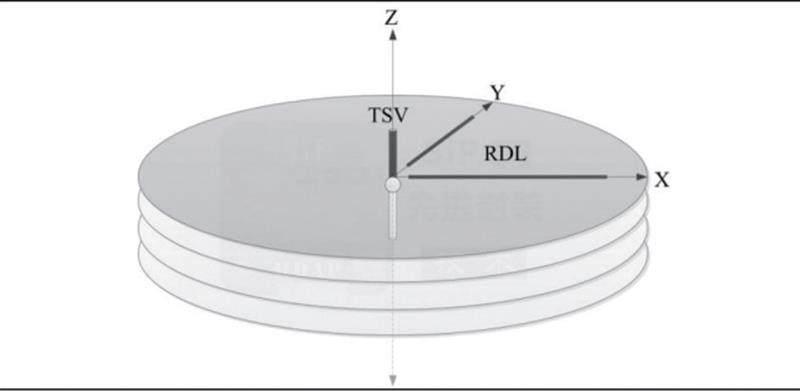

根据东方财富证券邹杰的研报,目前先进封装分为两大类(见图一):

一、基于XY 平面延伸的先进封装技术,主要通过RDL(ReDistributionLayer,重布线层工艺)进行信号的延伸和互连;

二、基于Z 轴延伸的先进封装技术,主要是通过TSV(Through Silicon Via,硅通孔)进行信号延伸和互连。

图一:先进封装两大类型

資料来源:先艺电子官网,东方财富证券研究所

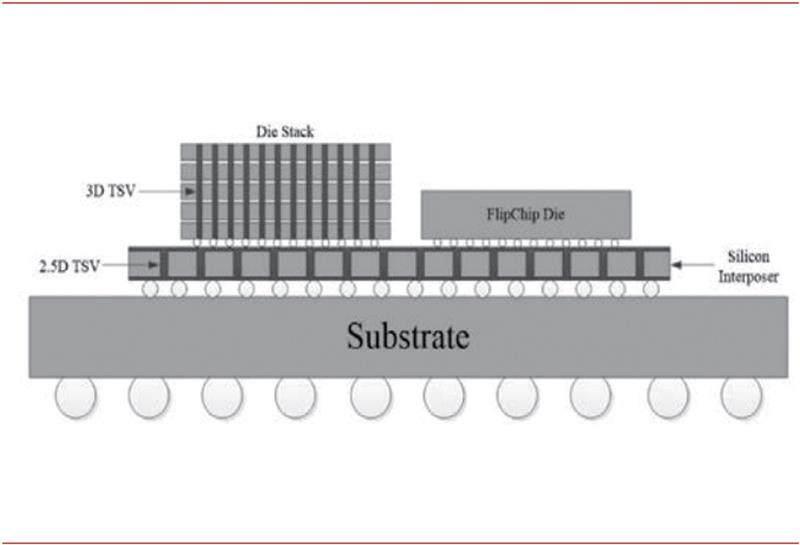

显然,芯片堆叠属于第二种。通过TSV 技术,可以将多个芯片进行垂直堆叠并互连。按照集成类型的不同分为2.5D TSV 和3D TSV,2.5D TSV 指的是位于硅转接板(Silicon Inteposer)上的TSV,3D TSV 是指贯穿芯片体之中,连接上下层芯片的TSV。在3D TSV 中,芯片相互靠近,所以延迟会更少,且互连长度缩短,能减少相关寄生效应,使器件以更高的频率运行,从而转化为性能改进,并更大程度的降低成本。TSV 的尺寸范围比较大,大的超过100um,小的小于1um。随着工艺水平提升,TSV 可以越做越小,密度越来越大,目前最先进的工艺,可在1 平方毫米硅片上制作10 万-100 万个TSV。(见图二)

根据中泰电子王芳等联名的报告,TSV 技术是目前唯一的垂直电互连技术。

TGV:TSV 的升级

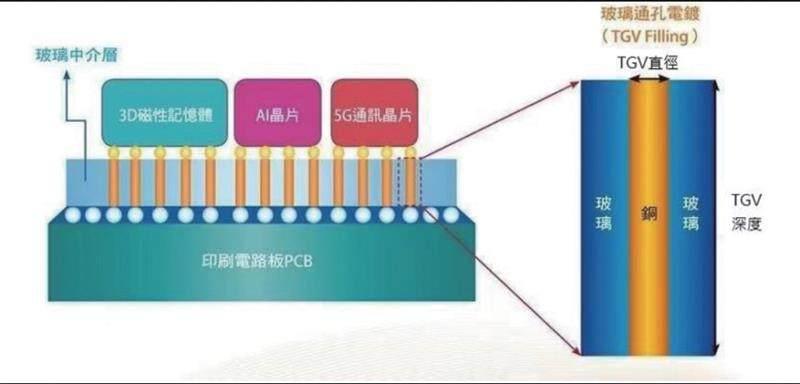

TGV 正是对TSV 的升级。(见图三)

根据东财研报,这是由于硅基转接板存在两个主要问题:

一、成本高,TSV 制作采用硅刻蚀工艺,随后硅通孔需要氧化绝缘层、薄晶圆的拿持等技术;

二、电学性能差,硅材料属于半导体材料,传输线在传输信号时,信号与衬底材料有较强的电磁耦合效应,衬底中产生涡流现象,造成信号完整性较差(插损、串扰等)。

相较硅基转接板,玻璃转接板优势显著。玻璃转接板有诸多优势:

一、低成本:受益于大尺寸超薄面板玻璃易于获取,以及不需要沉积绝缘层,玻璃转接板的制作成本大约只有硅基转接板的1/8;

二、优良的高频电学特性:玻璃材料是一种绝缘体材料,介电常数只有硅材料的1/3 左右,损耗因子比硅材料低2~3 个数量级,使得衬底损耗和寄生效应大大减小,可以有效提高传输信号的完整性;

三、大尺寸超薄玻璃衬底易于获取:康宁、旭硝子以及肖特等玻璃厂商可以量产超大尺寸(大于2m×2m)和超薄(小于50μm)的面板玻璃以及超薄柔性玻璃材料;

四、工艺流程简单:不需要在衬底表面及TGV 内壁沉积绝缘层,且超薄转接板不需要二次减薄;

五、机械稳定性强:当转接板厚度小于100μm 时,翘曲依然较小。

图二:3D TSV结构

来源:《先进封装与异构集成》,中泰证券研究所

图三:TGV工艺示意图

资料来源:台湾工研院官网,东方财富证券研究所

TGV 远期成长空间广阔

英伟达的H100 加速计算卡采用台积电CoWoS-S(S表示硅转接板)2.5D 封装技术,在硅转接板上实现7 组芯片互连,包括中间的H100 GPU die 及周围6 堆HBM 内存。AMD(超威半导体)MI300 采取类似布局,以CoWoS 工艺在硅转接板上封装6 颗GPU、3 颗CPU 及8 组HBM 内存。国内方面,壁仞科技BR100 系列GPU 也采用CoWoS-S 封装,将2 颗计算芯粒互连,实现算力的跨越式提升。

CoWoS 封装的核心之一为硅转接板及TSV 工艺,但其存在成本高和电学性能差等不足,而玻璃转接板及TGV 工艺具有低成本、易获取、高频电学特性优良等特性,因此,东财邹杰认为,TGV 有望作为前者替代品,成为先进封装核心演进方向之一,叠加AI 浪潮之下加速计算芯片需求高增,TGV 远期成长空间广阔。

其实,不止可用于转接板,搭配TGV 技术,玻璃基板的应用领域广泛,透明、气密性好、耐腐蚀等性能优点使玻璃通孔在光电系统集成领域、MEMS 封装领域有巨大的应用前景,也可以作为IC 载板使用,以在部分领域替代现在主流的ABF。

Chiplet 技术风潮之下产业转向大尺寸封装及小芯片设计,大型数据中心GPU 均使用小芯片封装,一片载板上最多可封装50 颗芯片,只要有一颗封装不良,就会导致整片报废。因此封装重要程度日渐提升,进而给封装材料提出新需求。ABF 载板已有劣势显露,其粗糙表面会对超精细电路的固有性能产生负面影响。作为替代方案的玻璃载板进入视线,玻璃载板具有比ABF 载板更光滑的表面,厚度降低四分之一以上,且使芯片的性能提高、功耗下降。

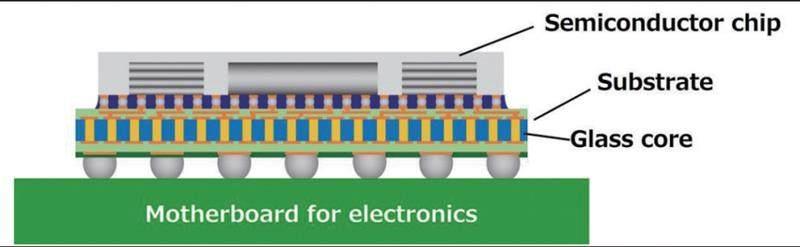

2023 年3 月DNP(大日本印刷株式会社)发布了针对下一代半导体封装的玻璃芯载板(GCS,GlassCore‐Substrate)。新产品用玻璃基板取代了传统的树脂基板(如倒装芯片球栅阵列)。通过使用高密度玻璃通孔(TGV)技术提供比基于现有技术更高性能的半导体封装,且该产品的制造工艺还可以支持对更高效率和更大尺寸载板的需求(见图四)东财邹杰认为,尽管玻璃载板商业化尚需时日,但其有望成为载板行业的规则改变者。

根据MarketsandMarkets 最近的研究,全球玻璃基板市场预计将从2023 年的71 亿美元增长到2028 年的84亿美元,2023 年至2028 年的复合年增长率为3.5%。在AI 的大势之下,目前,已有包括英特尔、AMD、三星等多家大厂公开表示入局玻璃基板封装。

大规模应用仍需再等等

虽然A 股市场已经热火朝天,但可真正用于半导体封装的产业链产品并不多。目前玻璃基板主要应用于显示面板的制造中,大多国内产业链厂商的应用暂时也仅限于显示场景。半导封装的玻璃基板要求比显示玻璃基板要求更高,高性能的玻璃基板成本较高,会导致产品整体成本增加。

另外,根据财联社报道,“ GB200 将使用玻璃基板封装”这一说辞也并不准确。尽管此次大摩用了一整页的篇幅介绍玻璃基板封装,但是财联社记者翻阅该报告发现,大摩并未明确GB200 将使用玻璃基板,仅表示预計在未来两年左右玻璃基板将被用于先进封装。

图四:DNP 玻璃芯载板示意图

资料来源:DNP 公司官网,东方财富证券研究所