一种基于FPGA 的AD936x 基带接口设计*

2024-04-03张跃为于宗光陆皆晟

张跃为,于宗光,陆皆晟

(1.江南大学物联网工程学院,江苏无锡 214122;2.中科芯集成电路有限公司,江苏无锡 214072)

0 引言

软件无线电中的数字化处理系统离天线非常近,所以整个系统对数字接收端的接口传输速率要求较高。传统的通信硬件架构中的模数转换器(ADC)会使用各种不同的器件作为物理层去驱动信号[1],如串并行CMOS 信号、低电压差分信号(LVDS)、低电压正极性发射耦合逻辑(LVPECL)、电流模式逻辑(CML)等,并遵循特定的数据样式和标准[2],因此在基带数据传输中,需要对FPGA 接口进行设计以兼容驱动ADC的特定器件,并且满足对应的数据格式和标准。在100 MHz 以下的低速数据接口中,单倍数据速率(SDR)CMOS 非常普遍[3],目前主流的基于CMOS 的通信接口有串行端口(SPORT)、集成电路互连总线(I2C)、串行外设接口(SPI)、通用异步收发器(UART)等,通过特定的接口协议标准可大幅降低接口的开发难度与成本[4]。但CMOS 的高低电平摆动幅度大,电平状态的切换时间长,不适用于传输速率高于100 MHz的信号;输出信号为单端信号,信号传输过程中易被干扰[5];通信接口存在功耗高的问题,即使COMS 器件的静态功耗较低,由于电平转换的范围较大,这些CMOS 接口产生的动态功耗也较高[6]。在100 MHz 以上的高速数据接口中,目前主流的接口标准为联合电子器件工程委员会204 标准(JESD204),数据速率可达12.5 GB/s[7],具有抗干扰能力强、低功耗、高速传输等特点,用于单一主机(如FPGA 或ASIC 等)与一个或多个ADC 之间的高速串行链路。但为实现数据帧的传输,JESD204 需要的资源远远多于简单的LVDS或CMOS,并且需要使用更昂贵的FPGA,PCB 布线也更复杂[8]。

为了满足高速率、高可靠、可配置等需求,同时兼顾成本和功耗的问题,本文针对“AD936x+ZYNQ”的软件无线电架构,设计了一种高效的无线通信数字基带接口。该接口物理层采用简单且低成本的并行LVDS 来发送数据[9],数字数据标准采用的是高速率的LVDS 双倍数据速率(DDR)传输模式,该模式下的并行LVDS 的功耗低于CMOS[10],该模式包含数据速率时钟和帧时钟,这两个时钟结合FPGA 中特有的DELAY、BUF 等延迟缓冲原语资源实现了差分转换、帧数据同步、可配置延迟等模块,这些模块可保证系统的高可靠数据采集。

1 接口技术原理

1.1 LVDS DDR 数据传输协议

目前AD936x 和数字基带处理器之间的数据接口有两种常用的工作模式:标准CMOS 兼容模式与LVDS 兼容模式。在CMOS 模式下,接口的时钟信号和数据信号均可以用单端信号线进行传输,虽然简化了端口信号,但在有噪声的环境下,CMOS 模式容易出现共模噪声、电磁干扰(EMI)等问题[11];在LVDS 模式下,AD936x 拥有较强的灵活性和稳定性,当使用LVDS 接口作为数据传输接口时,更有助于自定义的ASIC 连接具有LVDS 功能的FPGA。LVDS 由于其差分特性,在对低串扰和共模特性有较高要求的应用场景中优势明显并且综合成本较低,尤其在高速率、大容量数据传输系统中体现得更加明显[12]。LVDS 的输出电压摆幅可以保持在300~400 mV,同时可以兼容低于2 V 的电压;在信号传输过程中,其不仅抗干扰能力强,速率还可高达几百MB/s,并且功耗和噪声干扰也很低。

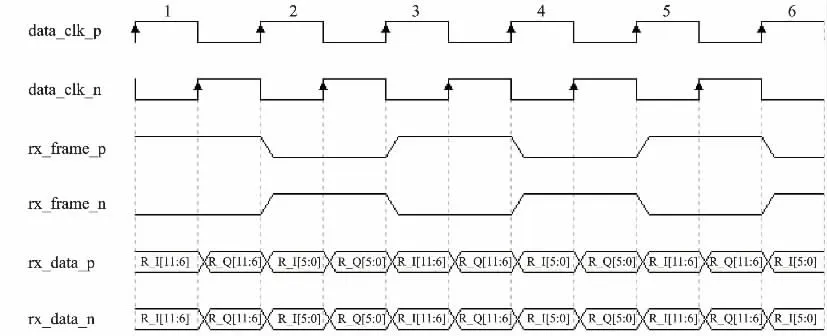

由于高速率的需求,系统需要提高一个时钟周期内可被采集的数据量,因此对于AD936x 和FPGA 之间的数据传输协议,接口主要采用LVDS DDR 数据传输模式,在单通道情况下,只需要两个时钟周期即可完成12 bit I/Q 数据传输,传输协议时序如图1 所示。

图1 传输协议时序

由图1 可知,在接收帧信号rx_frame_p 为高时,消耗一个时钟周期可接收到一个通道的高6 bit I/Q 数据;接收帧信号rx_frame_p 为低时,消耗一个时钟周期可接收到一个通道的低6 bit I/Q 数据;在数据时钟data_clk_p 的下降沿能够采集到I 路数据而上升沿能够接收Q 路数据,两个时钟沿即可采集到一个通道的I 路和Q 路的完整12 bit 数据。

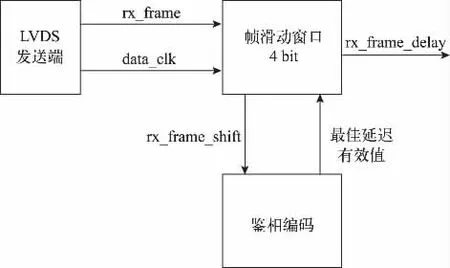

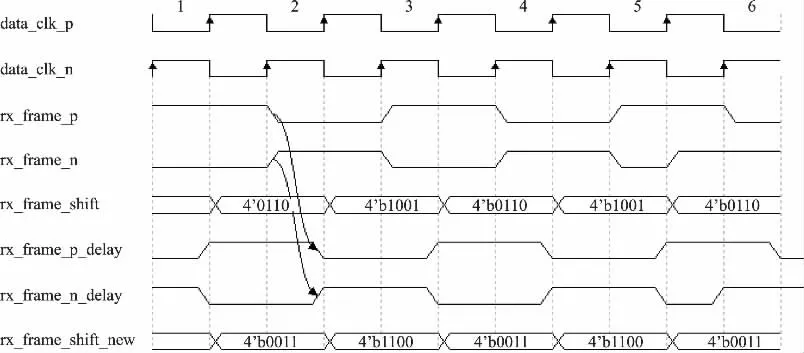

1.2 基于CDR 的帧数据同步

当时钟频率较高时,实际情况下会出现走线延迟,并行数据信号线的时序很难做到完美对齐,会有些相位的偏差。例如100 MHz 时钟,一个时钟周期只有10 ns,采样波形如图2 所示,数据线之间的时间延迟会对系统的数据接收产生一定的影响,因此将数据线的时序校正到可接收范围内非常关键[13]。为了确保帧时钟能正确采集到数据,防止出现无法解码的情况,本文引入了时钟数据恢复技术(CDR)[14],采用帧滑动窗口观察多组数据样本。根据协议时序要求,模块中设计了4 bit 的帧滑动窗口。帧滑动窗口若采集到4’b1100 或4’b0011,则满足协议要求,可将12 bit 的I/Q数据缓存入寄存器,进行数据处理;若采集到4’b1001或4’b0110,则说明数据信号在传输期间存在延迟,需要通过延迟模块进行相位偏移,直到初始相位对齐,为了确保数据采集的稳定性,整个帧数据同步操作都会经过鉴相编码,以获得最佳的采样位置;若采集到的帧信号不满足以上两种情况,则可判断为出现了失真等情况,不宜采样。帧数据同步逻辑如图3 所示。

图2 采样波形

图3 帧数据同步逻辑

2 系统硬件设计

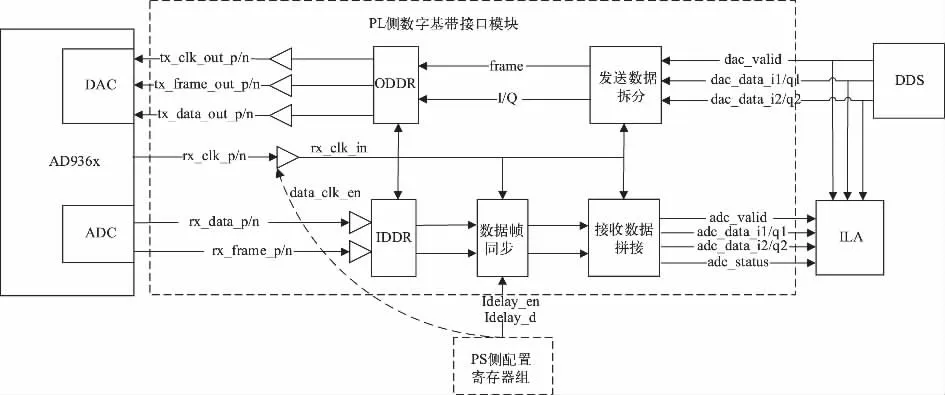

系统以ZYNQ 作为主控模块,通过SPI 接口控制AD936x 射频前端芯片完成各种收发通道参数的设置,实现射频收发,利用FPGA 的内部资源搭建AD936x 芯片与FPGA 内部基带数据处理模块之间的数字基带接口模块。为了使该基带接口模块具有可配置性,通过ZYNQ 的高级可扩展接口(AXI-Lite)实现时钟数据的延迟可配置;为了使该基带接口模块拥有高速抗干扰的性能,通过Xilinx FPGA 的输入延迟单元(IDELAYE2)、输入缓冲差分信号(IBUFDS)、带有门控时钟启用的缓冲器(BUFGCE)等原语资源以及FPGA 内部的逻辑运算资源实现帧数据同步;接口设计所用的数据传输格式为LVDS DDR 模式,在此模式下,通过输入双倍速率器件(IDDR)实现了数据速率时钟、帧时钟和数据等信号从双边沿采集转换至单边沿采集的高效操作,整体系统架构如图4 所示。

图4 整体系统架构

2.1 LVDS 数字基带接口模块

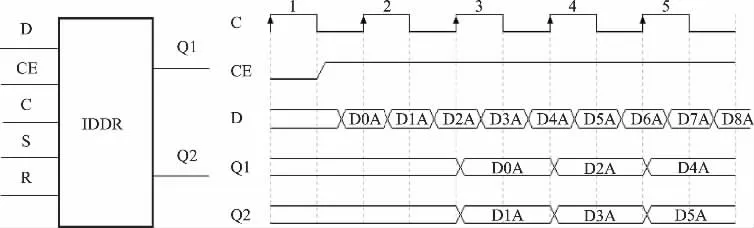

为了满足LVDS DDR 通信协议,AD936x 的数据送入FPGA 时,LVDS 数字基带接口模块需要将双边沿输出数据转换成单边沿数据,Xilinx 提供的IDDR和ODDR 两个原语便符合数据沿转换的要求,主要通过IDDR 原语的SAME_EDGE_PIPELINE 模式来实现,IDDR 接口和数据采集时序如图5 所示。

图5 IDDR 接口及数据采集时序

为了确保接收端接收到的帧和数据与发送端一致,LVDS 数字基带接口模块在数据输入端利用Xilinx FPGA 的延迟原语资源,通过CDR 技术实现帧数据同步,因此该模块使用了Xilinx 的IDELAYE2 原语,并通过用AXI-Lite 接口实现PS 端的软件配置的方式使其延迟值Idelay_d 的动态可调节能力大大增强。AD936x 数字基带接口架构如图6 所示。

图6 AD936x 数字基带接口架构

2.2 帧数据同步模块

在数据传输过程中,数据时钟与帧数据之间的延迟比较大时,会出现数据无法被正确采集到的情况,为了解决该问题,接口设计引入了帧数据同步模块,在数据输入端采用CDR 技术实现帧数据同步。利用Xilinx FPGA 的IDELAYE2、IBUFDS、BUFGCE 等原语资源,帧数据同步模块在接收端可以获得灵活调整接收数据与数据时钟/帧时钟延迟的能力[15]。由于前面通过IDDR 实现了双边沿信号的单边沿采集,因此在该模块中的所有信号均采用单端信号,在开始输入端采用IBUFDS 原语,将数据和时钟均变为单端信号。每当data_clk 产生一次上升沿,通过一个4 bit 移位寄存器便可采集新的2 bit 接收帧信号rx_frame,实现帧滑动窗口,用以检查进入该接口的帧信号是否满足LVDS DDR 数据格式4’b1100 或4’b0011,若不满足,则进行边沿检测和逻辑判断,并校正得到最佳数据采样位置。当时钟与帧数据相位差较大时,需要通过IDELAYE2 原语对数据rx_data 和rx_frame 进行多级延迟,该IDELAYE2 原语可进行32 级延迟,延时分辨率由参考时钟决定,该模块采用FPGA 内部的锁相环生成的200 MHz 参考时钟产生78 ps 分辨率的延迟。帧数据同步模块结构如图7 所示。

图7 帧数据同步模块结构

为了确定最佳数据采集位置所需要延迟的级数,在数据帧同步模块中需要进行鉴相编码,由于共有32级延迟,因此可设置的编码位数为5 bit,最大编码值为31,当采集到的帧信号为4’b1001 或4’b0110 时,设置编码为0,之后的编码值均为前一个编码值加1,同时进行与编码值一样的级数的延迟,直到采集到的帧信号为4’b1100 或4’b0011;为了确定正确信号的边缘,可将当前帧滑动窗口值与上个时钟沿采到的值进行对比;确定了边缘后,还需要对边缘信号的编码值进行记录、保存,并继续进行编码延迟,直到获得下一个边缘信号,即可确定两个边缘中间时的编码值,以获得最佳采样位置。帧数据滑动窗口值同步前后时序如图8 所示。

图8 帧数据滑动窗口值同步前后时序

3 实验验证与分析

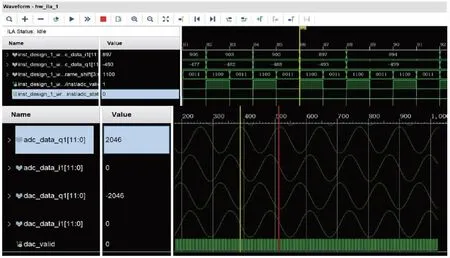

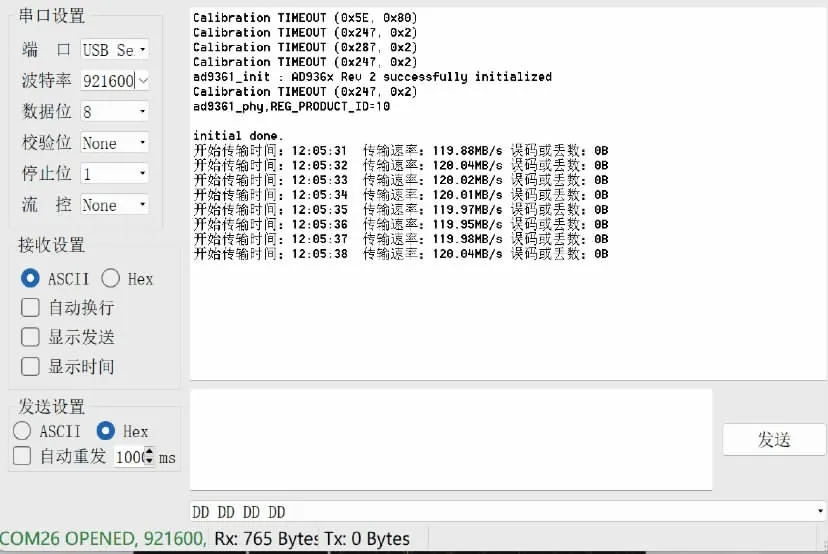

在实验室中采用ZYNQ-7020 和AD936x 的通用软件无线电平台对该接口进行了测试。采用DDS IP核产生正弦波单音输入信号,配置AD936x 内部时钟获得同步采样时钟,通过JTAG 测试接口将该接口接收到的采样数据在ILA 中显示。采样时钟为80 MHz时,位宽为12 bit、频率为780 kHz 的正弦波单音输入信号的测试结果如图9 所示,其中移位帧寄存器rx_frame_shift 用于获取数据位的帧时钟数据滑动窗口,dac_data_q1 和dac_data_i1 是发送端数据时序波形,adc_data_q1 和adc_data_i1 是采样数据时序波形,每两个采样时钟周期可采集到I/Q 两路共24 bit 数据,因此传输速率达到了120 MB/s。接口传输速率及误码测试结果如图10 所示。

图9 正弦波单音输入信号的测试结果

图10 接口传输速率及误码测试结果

4 结论

基于LVDS DDR 数据传输协议,本文提出了一种可进行帧数据同步且可灵活配置调控的基带数字接口模块设计方法,并进行了验证和测试。该模块引用了Xilinx 的IDELAYE2、IBUFDS、IDDR 等原语模块进行差分与单端信号之间的高速设计,实现了帧数据同步功能,同时也实现了使用ARM Cortex-A9 嵌入式硬核完成对AD936x 的初始化以及状态的控制和参数的配置。此外,对该模块进行了单音正弦波信号的收发实验,通过ILA 观测到了完整的收发数据,并通过采样时钟速率以及接收数据位数计算了该接口的传输速率,同时进行了数据对比、计算了误码率。结果表明,传输速率达120 MB/s,未出现误码,接口模块性能良好,进一步提高了AD936x 的通信性能。