一种可暂停的低功耗DMA 控制器设计及验证

2024-04-03苏皇滨林伟林伟峰

苏皇滨,林伟,林伟峰

(福州大学物理与信息工程学院,福州 350000)

0 引言

直接内存存取(DMA)控制器是一种重要的硬件设备,用于实现计算机系统中的直接内存访问。计算机系统及应用程序的不断发展对数据传输速度和效率的要求日益提高,DMA 控制器的重要性也日益凸显。DMA 控制器广泛应用于各种计算机系统,特别是在需要大数据量传输和复杂数据流处理的应用领域,如图形处理、音视频编辑以及网络通信等领域[1]。在当今高科技领域的快速发展和智能设备的普及背景下,低功耗、可持续的设计理念已深入各种电子设备的设计中。传统的DMA 控制器在工作过程中存在不少难以忽视的问题,如高功耗、低灵活性和资源浪费等。文献[1]针对传统架构的DMA 控制器存在的面积资源浪费问题提出一种多通道且面积优化的设计方案;文献[2]通过在模块级设计中采用独热码多路器和格雷码编码状态机的设计方法对功耗进行了一定的优化,为DMA 控制器的高功耗问题提供了解决方案。通过分析已有的DMA 控制器设计方案可以发现,大多方案没有考虑到DMA 控制器的可暂停性。但是,在某些情况下,可暂停操作非常必要,特别是在高效数据传输的场景,例如在视频流传输过程中,DMA 控制器可以将数据从摄像头缓冲区传输到内存缓冲区,同时CPU可以对这些数据进行处理,如图像识别、特征提取等,当CPU 需要更多的时间来处理数据时,DMA 控制器可以暂停传输,等待CPU 完成处理后再继续传输数据,用户可以更加灵活地控制数据传输。此外,当系统中有多个DMA 传输操作时,可以通过暂停某些传输操作,调整DMA 传输的优先级,以满足系统的需求。因此,本文提出了一种可暂停的低功耗DMA 控制器设计方案,在保证数据传输质量的前提下,不仅实现了低功耗设计,而且解决了现有DMA 控制器在灵活性方面的局限性。

1 DMA 控制器的整体结构

DMA 控制器从本质上来说是一种专用的接口电路,其包含中断机制,采用DMA 方式连接外部设备与总线[3]。本文设计的DMA 控制器包含1 个从机模块ahb_slave(用于信息配置)以及1 个主机模块axi_master(用于数据传输),内建1 个32×64 bit 的数据先入先出(FIFO)存储空间,最大支持4 kB 传输,支持源端及目的端设备类型自由配置,即存储器到存储器、存储器到外设、外设到存储器、外设到外设4 种传输模式,支持多种传输位宽和不同的地址传输方式,AXI 总线读写通道支持outstanding 功能,即主机能够不等待上一次传输完成就开始发送新的传输地址。

目前DMA 传输结构主要有2 种模式:描述符模式和寄存器模式[4]。本设计采用寄存器模式,即DMA传输的参数和控制信息都保存在特定的寄存器中,CPU 通过写入这些寄存器来配置DMA 传输的源地址、目的地址、传输长度等参数。一旦配置完成,DMA控制器就可以独立完成数据传输操作,不需要CPU 的介入。DMA 控制器通过直接访问系统总线,直接与内存进行数据传输。

DMA 控制器的整体架构如图1 所示,主要由从机模块ahb_slave、寄存器模块dma_reg、跨时钟域同步模块sync、引擎模块dma_engine、主机模块axi_master、时钟门控模块clk_gate 和外设握手模块hand_req 组成。

图1 DMA 控制器的整体架构

ahb_slave 通过AHB 总线与CPU 进行通信[5],CPU 的配置信号与控制信号都是通过该模块传入DMA 控制器,CPU 通过该模块查看DMA 控制器的寄存器状态。dma_reg 用来接收来自ahb_slave 的CPU配置DMA 任务的数据信息,并将这些信息存放到模块内对应的寄存器中,之后再将这些信息进一步同步到AXI 时钟域的dma_engine 中,此模块主要作用是存储配置信息。sync 用来管理DMA 控制器不同时钟域之间的同步逻辑[6]。dma_engine 是整个DMA 控制器的核心,根据dma_reg 中存储的配置信息,完成读数据、拼接数据、写数据等操作。axi_master 是DMA 端控制AXI 总线进行数据传输的模块,能够控制AXI 总线上2 个相应设备间的数据传输。当DMA 控制器没有任务进行时,clk_gate 通过控制系统中的时钟使其进入低功耗模式,以降低功耗[7-8]。hand_req 用于实现DMA 控制器源端与目的端的外设握手,从而进行异步信号处理。

2 关键模块的具体实现

2.1 功耗分析与时钟门控

芯片功耗分为动态功耗和静态功耗,动态功耗是设备运行时或者信号改变时所产生的功耗,静态功耗则是设备上电但是信号没有改变时所产生的功耗[8]。动态功耗又可以分为翻转功耗和短路功耗。翻转功耗Pswitch是动态功耗最主要的组成部分,计算公式为

其中CL为输出电容,Vdd为供电电压,Ptrans为输出翻转率,fclock为时钟频率[4]。在满足芯片功能的前提下,可以通过降低Vdd、Ptrans、CL的方法来减少功耗。

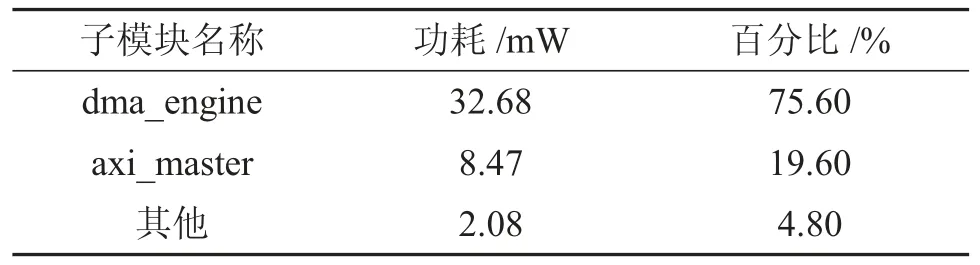

在数字集成电路设计中,时钟信号的翻转率是比较高的[9],它引起的功耗约占整个芯片功耗的20%~30%,因此时钟门控技术特别重要[7,10]。时钟门控技术就是根据设计,将暂时不用的模块的时钟信号进行门控,降低这个模块的时钟信号翻转率,从而降低芯片功耗的一种技术[10]。各模块功耗如表1 所示,本设计中DMA 控制器的功耗来源主要是dma_engine,通过Synopsys 公司的Design Compiler(DC)综合工具初步计算,采用SMIC 180 μm 工艺,在AXI 总线时钟(aclk)频率为100 MHz、AHB 总线时钟(hclk)频率为50 MHz 的情况下,dma_engine 的功耗约占据整个设计总功耗的75.60%,因此通过时钟门控技术,在启动信号到来之前和完成信号到来之后将dma_engine 的时钟信号关闭,从而达到降低功耗的目的。时钟门控技术的实现电路如图2 所示,由1 个锁存器latch 和1个与门组成,当启动信号到来时,使能信号en 为高电平,时钟信号gclk 开启。当完成信号到来时,en 为低电平,gclk 关闭。前仿真结果表明,在启用时钟门控技术后,该模块功耗从32.68 mW 降到了12.39 mW,减少了62%。

表1 各模块功耗

图2 时钟门控技术的实现电路

2.2 主控模块与状态机

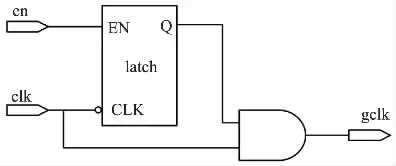

dma_engine 在收到启动信号后开始工作。读数据、拼接数据、写数据的过程划分为5 个阶段,在模块设计中采用有限状态机的方法[13],5 个阶段对应S0~S4 5 个状态,其状态转移如图3 所示。

图3 状态转移图

S0:空闲状态,DMA 处于空闲状态。

S1:数据接收状态,在该阶段发送读命令,接收读通道的数据,并将读取到的数据存入FIFO。

S2:等待状态,当有暂停请求或FIFO 空间不足时,进入该状态。

S3:边读边写状态,根据FIFO 中存放的数据量计算最多能发送多少笔数据,将写地址信息配置给写地址通道,同时从读数据通道读取数据并存入FIFO。

S4:数据拆分状态,因为支持32 bit 和64 bit 的数据传输,所以需要该状态进行写数据拆分处理。

各状态之间的转移条件如下。

C0:接收到启动信号且外设握手完成。

C1:收到暂停指令且完成当前一笔传输或者FIFO 空间不足。

C2:退出暂停模式或者FIFO 空间足够。

C3:FIFO 内存储的数据大于等于当前一笔写操作的数据量且FIFO 剩余动态空间足够。

C4:FIFO 内存储的数据大于等于当前一笔写操作的数据量。

C5:FIFO 内存储的数据小于当前一笔写操作的数据量。

C6:当前一笔写数据发送完成。

C7:写地址配置信息发送完成。

C8:所有写数据均发送完成。

2.3 可暂停模式设计

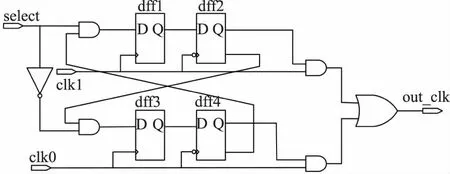

为了满足一些特定的场景需求,需要对DMA 控制器传输的数据进行实时处理。例如,在音频或视频处理中,可以使用DMA 控制器来传输数据,然后在处理器或其他专用硬件上进行实时音频或视频处理。在这种情况下,可暂停模式可以让处理器或其他硬件及时处理紧急任务,之后再继续进行DMA 传输,这个过程无需重新配置控制信息,提高了工作效率。同时,为了让DMA 控制器在暂停模式下处于低功耗状态,设计了时钟调整机制,时钟无毛刺切换电路原理如图4所示,通过控制选择信号select 使时钟从高频段切换到低频段,从而达到降低功耗的目的。

图4 时钟无毛刺切换电路原理

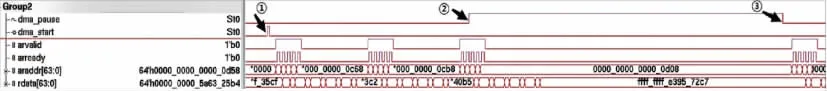

当需要进入暂停模式时,通过配置DMA 寄存器来启用暂停模式,DMA 控制器将停止传输数据,在暂停期间,状态机将会进入等待状态,并且DMA 控制器会保存当前的传输状态,包括源地址、目标地址、传输计数等相关信息。当重新启动DMA 传输时,恢复之前保存的传输状态,并继续传输剩余的数据。暂停模式波形如图5 所示,DMA 控制器在标号①处开始工作,经过一段时间后,在标号②处开启暂停模式,进入暂停状态,期间控制器不工作且处于低功耗状态,在标号③处关闭暂停模式,退出暂停状态,继续进行数据传输。

图5 暂停模式波形

3 DMA 控制器的仿真验证

3.1 验证环境及功能点

本文利用通用验证方法学(UVM)[14-15]搭建了相应的验证平台,图6 为平台框图,DUT 为待测设计,axi_slave_agent 为AXI 从机代理,ahb_master_agent 为AHB 主机代理,scoreboard 为计分板,agent 中的seqr、drv、mon 分别代表UVM 的序列、驱动、监测组件。采用基于覆盖率驱动(CDV)的验证策略,从接口类、功能类、异常类提取验证功能点[16],针对每个功能点编写测试用例,借助Synopsys 公司的VCS 仿真软件进行验证。

图6 验证平台框图

根据设计文档提取的功能点如下。

(1) 复位功能及寄存器读写功能的正确性。

(2) 正常传输模式下,地址对齐和地址非对齐传输的正确性,不同的数据传输位宽(32 bit 和64 bit),不同的地址传输模式(INCR 类型和FIXED 类型),不同的突发长度(1~16),不同的源端、目的端类型(存储器类型和外设类型)。

(3) 中断异常检测,包括超时中断、传输错误中断、配置错误中断、传输完成中断。

(4) 进入/退出暂停模式的测试以及检查暂停前后相关配置信息参数是否保持不变。

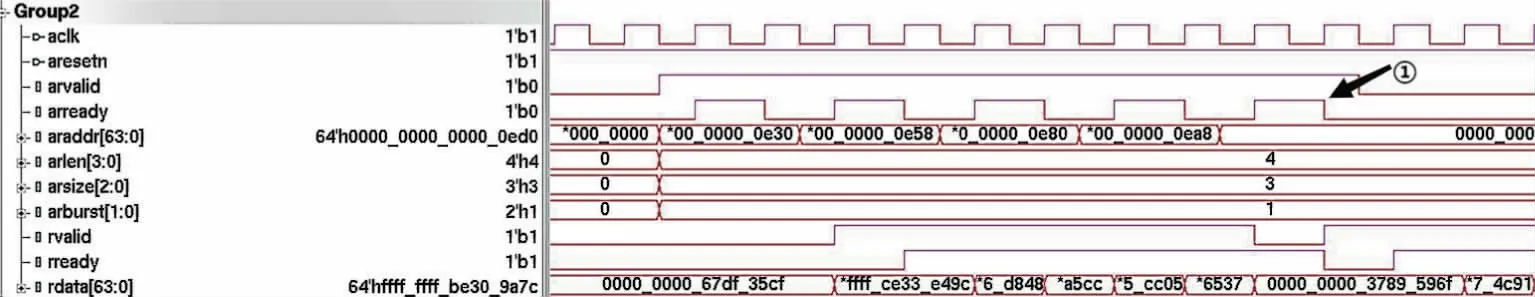

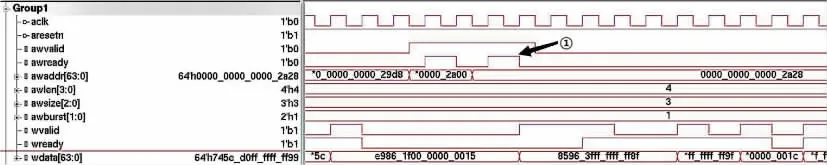

3.2 AXI 读写数据仿真结果

在完成DMA 控制器的配置后,DMA 开始进入工作状态,根据配置信息从对应的源端设备读取数据。读数据关键信号的波形如图7 所示,当arvalid 和arready 同时为高时,完成握手,读地址通道arlen/arsize/arburst 有效;当rvalid 和rready 同时为高时,读数据通道rdata 有效[17-18]。在内部FIFO 剩余空间足够大的时候,axi_master 会1 次发送至多5 个读指令,见图7 中标号①的波形,即读通道outstanding 能力为5。写数据关键信号的波形如图8 所示,当awvalid 和awready 同时为高时,完成握手,写地址通道awlen/awsize/awburst 有效;当wvalid 和wready 同时为高时,写数据通道wdata 有效,至多1 次发送2 个读指令,见图8 中标号①的波形,即写通道outstanding能力为2。

图7 读数据关键信号的波形

图8 写数据关键信号的波形

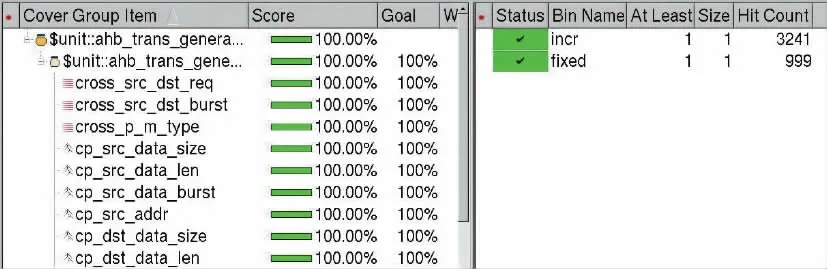

3.3 覆盖率统计结果

为了保证验证的完备性,在收集覆盖率时,需要确保代码覆盖率和功能覆盖率同时达到要求[18]。代码覆盖率用于衡量测试用例是否真正地覆盖到了所有的代码段,而功能覆盖率用于检查Spec 设计中所要求的功能点是否测试完成。功能覆盖率如图9 所示,图中cross_*和cp_*(*代表任意字符)均为提取的功能点,此处不再一一解释,这些功能点的覆盖率是最终跑完回归测试后的结果,因此所有功能点均已按要求被覆盖到,覆盖率达到100%。Line/Toggle/FSM/Condition/Branch 的代码覆盖率如图10 所示,所有模块的代码覆盖率在经过过滤处理后均达到100%。

图9 功能覆盖率

图10 代码覆盖率

4 结论

本文设计了一种可暂停的低功耗DMA 控制器,并完成了功能测试,代码覆盖率和功能覆盖率均达到100%。该DMA 控制器不仅加入了时钟门控技术,而且设计了可暂停模式以提高灵活性,并在暂停模式下,通过时钟无毛刺切换电路将其在暂停过程中从高频时钟段切换到低频时钟段,降低了时钟频率,从而降低了功耗。仿真验证结果表明,该设计在多种传输模式、不同数据传输位宽、不同地址传输方式的配置下均能正常工作,且功能正常,引擎模块功耗降低62%,达到低功耗的设计目标。