支持4K 分辨率的ARINC818 视频传输验证系统

2024-03-20高伟林杨炳伟辛春明

高伟林,杨炳伟,辛春明

(航空工业苏州长风航空电子有限公司,江苏 苏州 215151)

0 引言

航空电子技术的飞速发展对机载座舱视频传输系统提出了更高的要求,传统的DVI、VGA 等视频接口难以满足高分辨率视频传输需求,尤其在视频分辨率达到4K(3 840×2 160)或以上时,由于链路速率大幅提升,在机舱内复杂电磁环境下视频传输链路极易受到干扰,导致传输可靠性变差。ARINC818(航空电子数字视频总线,Avionics Digital Video Bus,ADVB)视频总线采用光纤通道进行传输,其技术特点恰好满足现代航电视频数据总线的要求,具备高带宽、高可靠性、低延迟、非压缩视频传输、抵抗电磁干扰、减轻线缆重量、灵活性高、兼容性扩展性强等优势[1-2]。ARINC818 总线已在波音787、空客A350、A400M、C-130J 等飞机驾驶舱视频传输系统中得到应用[3]。

随着显示器分辨率的逐步提高,对视频带宽的要求也越来越高,在2019 年发布的ARINC818-3 规范中新增了对10 Gb/s 编解码链路速率的支持[4]。本文针对未来机载座舱高分辨率视频传输需求,设计了一种支持4K分辨率的ARINC818 视频传输验证系统,链路速率达到10 Gb/s,支持 单链 路4K@30 Hz 和 双链 路4K@60 Hz 视频传输,并通过DP 视频接口完成传输验证。

1 ARINC818 协议规范

ARINC818 协议标准是在FC-AV(Fiber Channel Audio Video)音视频协议基础上进行简化而得,共有5 层协议[5],如图1 所示。

图1 光纤通道5 层协议

(1) FC-0 层描述物理接口,包括传输介质、发射机和接收机及其接口,规定了各种介质能够承载的各种运行速率。

(2) FC-1 层描述了8B/10B 编码规则,该码型可以区分控制字节和数据字节,可简化比特、字节和字同步,并且能够提高差错检测能力。此外,FC-1 对发射机和接收机的状态进行了规定。

(3) FC-2 层是信号传输协议层,规定了帧格式、帧序列及通信协议。

(4) FC-3 层涉及网络服务,如链路初始化、路由等,不适用于点对点特征的ADVB,ARINC818 未使用。

(5) FC-4 层作为光纤通道协议架构的最高层,定义了多种与FC 相关的应用接口,制定了光纤通道与上层应用协议间的映射规则。ARINC818 使用帧头控制协议FHCP(Frame Header Control Protocol),提出容器概念。

1.1 容器系统

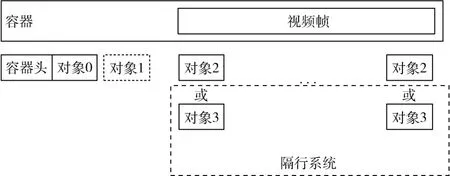

ADVB 容器是ARINC818 系统中传输视频信息的基本单元,一个容器包括一帧视频的所有视频、音频及附加数据,容器按顺序方式传送以提供连续动态更新的图像。容器由容器头和对象组成,如图2 所示。

图2 ADVB 容器结构

容器头大小为22 个FC 字(32 bit),主要包括容器计数、视频标识、容器时标、传输类型、容器类型、对象参数等信息。对象0 传输附加信息,一般为2 个FC 字,规定视频帧分辨率、颜色信息、扫描方式、像素排列方式等信息。对象1 传输音频数据,一般不使用。对象2 和对象3传输视频数据,逐行系统中,仅使用对象2。

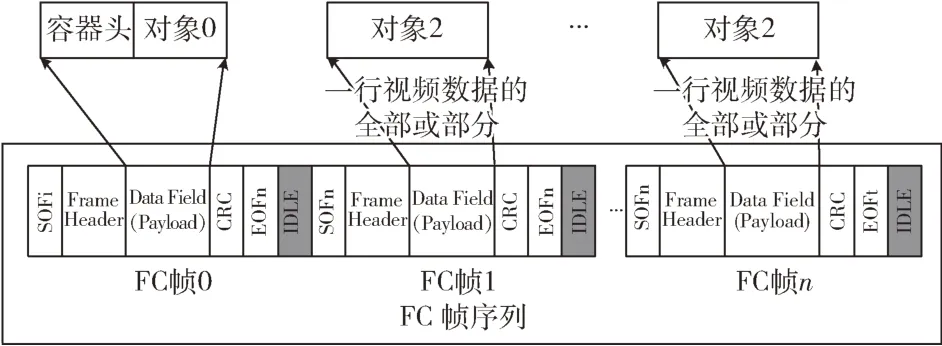

1.2 FC 帧序列

一个ADVB 容器与一帧视频对应,裂变为一个FC帧序列,如图3 所示。每个FC 帧通过SOF(Start of Frame)和EOF(End of Frame)两种类型定界符定义帧信息起始、结束,同时包含6 个FC 传输字的帧头定义,用于传输FC 帧路由控制、类型、帧控制等信息。容器头与对象0 封装入第一个FC 帧中,剩余FC 帧用于封装像素数据,有效载荷长度最大为2 112 B,若一行像素数据不大于2 112 B,每一行像素数据封装入一个FC 帧中,若一行视频数据大于2 112 B,将每一行像素数据进行合适的划分并封装入多个FC 帧。

图3 FC 帧结构

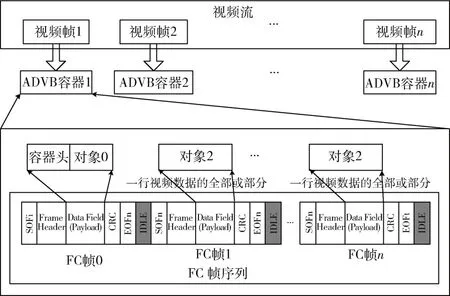

图4 为视频流到FC 帧序列的映射,一帧视频与一个ADVB 容器对应,一个容器与一个FC 帧序列对应。每帧画面第一个FC 帧的SOF 格式为SOFi(SOF initiate),其后的每一个FC 帧的SOF 格式为SOFn(SOF normal)。最后一个FC 帧的EOF 格式为EOFt(EOF terminate),其他FC 帧的EOF 格式为EOFn(EOF normal)。FC 帧之间填充IDLE 数据。

图4 视频流到FC 帧序列的映射

1.3 ICD 文档

ICD(Interface Control Document)接口控制文档用于记录ARINC818 视频配置信息,包括链路速率、视频分辨率、刷新率、扫描方式、颜色信息等。发送端和接收端的ICD 必须一致才能实现正确的发送和接收操作[6]。

2 方案设计

2.1 系统架构

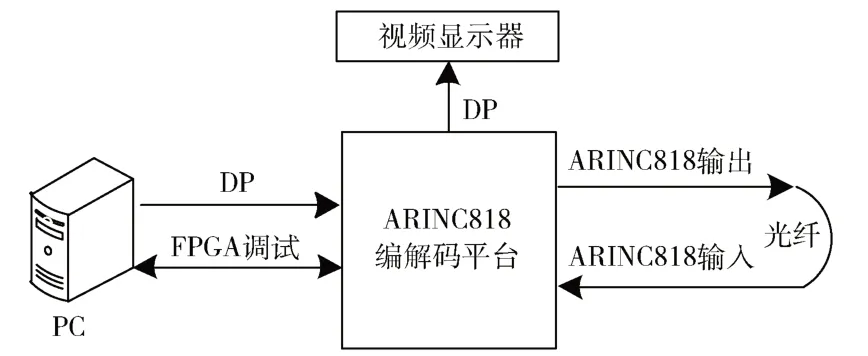

本系统采用FPGA 完成ARINC818 的编解码逻辑设计,并采用DP 视频完成视频链路传输验证,硬件系统框图如图5 所示。

系统接收上位机输出的DP 视频,送入FPGA 的GTX 高速端口,再通过DP IP 核实现DP 链路解码,解码后的视频数据送入ADVB 编码模块,按照ARINC818 协议完成封包处理后,再通过GTX 高速端口形成串行ARINC818 视频经光电模块送出。

使用光纤连接本系统的ARINC818 输入输出端口,将产生的ARINC818 视频再回送至本系统,通过GTX 高速端口和ADVB 解码模块后,再编码形成DP 视频输出显示。

2.2 GTX 高速端口

本系统选用Xilinx 的Kintex-7 系列FPGA,集成GTX高速接口,能够提供最高12.5 Gb/s 的链路速率[7],高度可配置化,具有8B/10B 编解码、RD 控制、逗号检测、字对齐、时钟矫正、预加重等功能[8]。

GTX 的发送通道和接收通道均由PMA(物理媒介适配层)和PCS(物理编码子层)两部分组成,PMA 中集成了串并转换器、发送接收缓冲、时钟发生器和时钟恢复电路。PCS 中集成了8B/10B 编解码模块、逗号检测对齐模块和用来进行时钟校正的弹性缓冲区。GTX 收发结构简图如图6 所示。

3 ARINC818 编解码设计

ARINC818 协议的FC-2 和FC-4 层通过ARINC818编解码模块实现。ARINC818 编解码模块的功能包括:

(1)将视频流数据编码成32 bit 的FC 帧序列送至GTX 模块;

(2)接收GTX 模块的32 bit FC 帧序列将其解码成视频流数据输出。

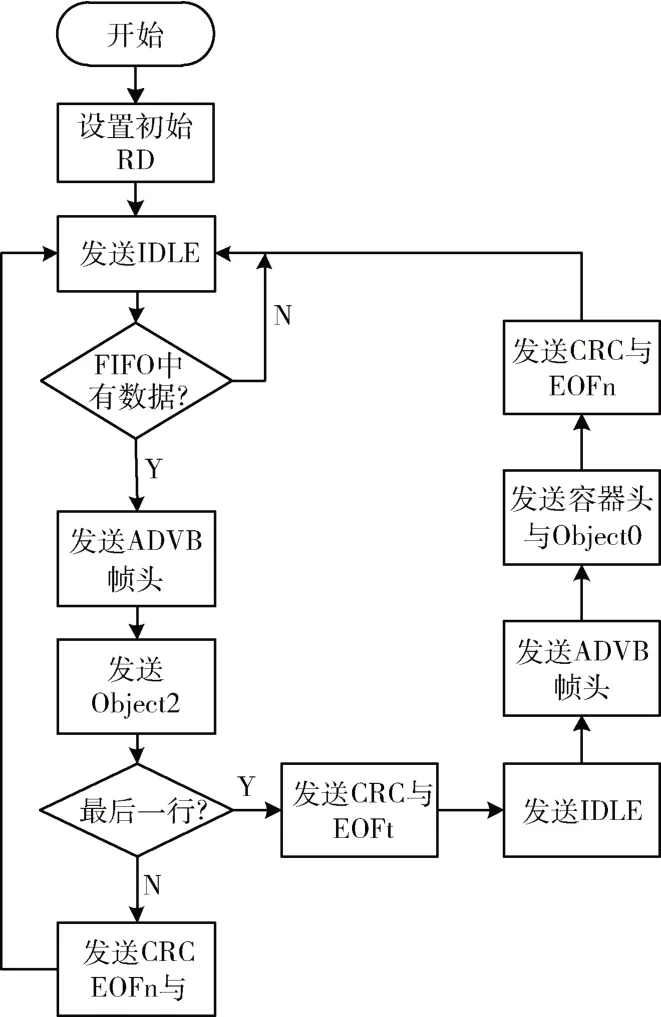

3.1 ADVB 编码模块

ARINC818 编码模块流程图如图7 所示,模块初始化完毕后控制链路的初始RD 值为负,并通过查找表实时记录当前链路的RD 值。等待FIFO 中缓存一行图像数据后,发送载有对象2 视频数据的FC 帧,首先发送SOFn、FC 帧头数据,读取FIFO 中的数据并发送FC 帧的有效载荷,当前FC 帧有效载荷发送完成发送CRC 校验结果,并根据当前的RD 值发送合适EOF。若一行图像数据能够存在一个FC 帧中(即数据小于等于2 112 B),等待FIFO 中存入下一行数据,重复上述过程至一帧图像传送完毕。若一行图像数据大于2 112 B,将一行图像数据划分存入的FC 帧,FC 帧之间填充预先设定好数量的IDLE 数据,一行图像发送完毕后等待FIFO 中存入下一行数据,重复上述过程至一帧图像传送完毕。

图7 ARINC818 编码模块流程图

载有对象2 的FC 帧发送完成后,发送预先设定好数量的IDLE 数据,接着发送下一帧图像数据载有容器头和对象0 的FC 帧,等待FIFO 中存入一行图像数据后重复上述发送载对象2 的FC 帧的过程。

3.2 ADVB 解码模块

ARINC818 解码模块流程图如图8 所示,检测到数据流中的SOFi 信号后解析第一个FC 帧,读取容器头和对象0 的数据存入相应的寄存器中。解析完成第一个FC 帧后持续检测数据流中的SOFn 信号,读取对应FC帧中的对象2 视频数据存入FIFO 中,通过Frame Header中F_CTL 的bit19 标志位(容器中的最后一帧,有效为“1”)和FC 帧结束的SOFn/SOFt 判断当前FC 帧是否为一帧图像画面的最后一行数据,若是,开始检测SOFi,若不是,重复检测SOFn。在上述存储过程中,通过CRC计算模块计算并校对链路数据是否有错误,若有错误上报CRC 错误。

图8 ARINC818 解码模块流程图

3.3 4K@30 Hz ARINC818 协议实现

对于4K@30 Hz 视频,带宽由式(1)计算得出,式中3 840×2 160 为视频分辨率,24 为像素位宽,30 为帧率,1.25 为加上附加信息和协议控制信息后的等效带宽倍乘因子。

ARINC818 传输系统采用10 Gb/s 链路速率,一条传输链路即可满足要求。通过FPGA 的QPLL 设置GTX 速率,QPLL 输出的时钟频率由式(2)计算:

链路速率通过PLL 输出时钟的上升沿和下降沿产生,且发送和接收均有一个时钟分频模块,将PLL 输出时钟降频D倍,链路速率由式(3)计算:

式中N、M和D由表1 中的属性或者接口决定。

表1 QPLL 分频设置

输入的参考时钟频率为100 MHz,M设置为1,N设置为100,D设置为1,将链路速率匹配为10 Gb/s。

一个FC 帧最大支持2 112 B 的负载数据,对于分辨率为3 840×2 160 的应用,若视频图像为RGB888,则一行图像容量为11 520 B,无法在一个FC 帧内传输一行视频数据,因此在4K 视频传输中需要将每一行视频分割为6 个FC 帧进行传输,每一个FC 帧封装1 920 B 字节数据。一帧图像则需要12 960 个FC 帧方可传输完成。每个FC 帧之间填充着预先设定好的IDLE,IDLE 时长最后设置为ICD 参数集成到现有工程中。

ADVB 接收端的ICD 与发送端一致,接收端在获取链路同步后实时接收链路上的FC 数据帧,根据附加数据中的格式完成图像数据的重组。由于ADVB 协议规定的有 序集为SOFi1、SOFi3、SOFn1、SOFn3、EOFn、EOFt 以及IDLE,因此在接收端除此之外的其他有序集均视为IDLE 对待。同时,接收端采取以下原则以保证当链路故障情况时始终能够从下一幅图像第一行数据完整显示出:

(1)当检测到链路失同步时,需重新获取链路同步并等待直至下一个SOFi 到来,才开始正常接收;

(2)当检测到8B/10B 编码错误,需获取并保持链路状态直到下一个SOFi 正常;

(3)当检测到CRC 校验错误,则丢弃当前帧,停止接收直到下一个SOFi。

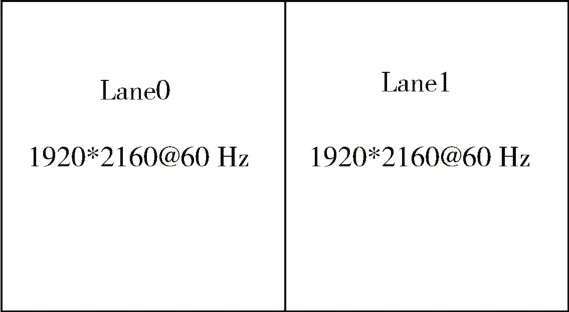

3.4 4K@60 Hz ARINC818 协议实现

对于4K@60 Hz 视频,带宽由式(4)计算得出,总带宽超过了单条链路所能提供的10 Gb/s 带宽。当单条链路速率无法满足应用时,ARINC818 协议支持多链路模式,将视频帧按一定模式进行分割,如左右半屏或奇偶像素,再将分割后的数据分别绑定到多个链路。实际应用中,将画面分割为左右半屏并分别绑定到两条链路上,如图9 所示。在发送端,图像数据按左右半屏方式分配至两个 ARINC818 编码发送模块;在接收端,ARINC818数据接收模块将两条lane 收到的数据分别写到同一块内存区域的左右两边,使其组成一帧完整的4K图像。

图9 画面分割与链路绑定方式

4 DP 视频编解码设计

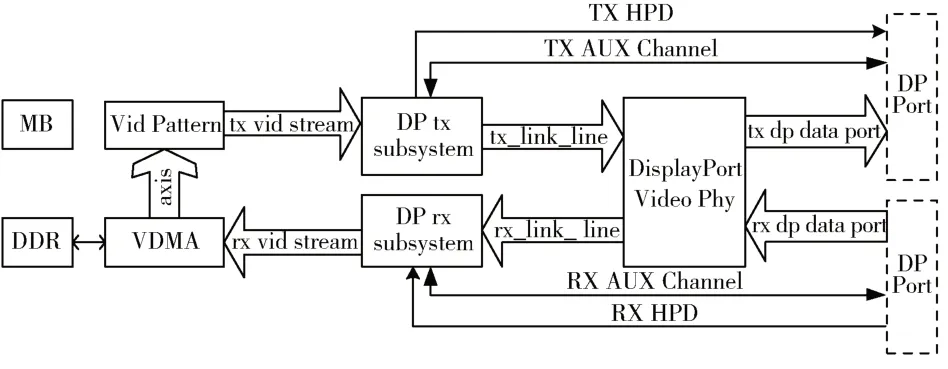

本项目采用DP 视频接口完成ARINC818 视频传输验证,DP 视频编解码功能采用Xilinx 的DP IP 实现,为了完整验证DP 视频收发功能,设计了pass-thorugh demo 框架,如图10 所示,主要包括以下几个部分:

图10 pass-thorugh demo 框架

(1) MB,Microblaze 软核,用于系统运行的管理,主要包括DP 编解码的控制管理、VDMA 的控制管理、动态时钟的配置等;

(2) DDR,用于存储视频数据,实现视频数据缓存等,本设计中,DDR 总线的位宽为64 bit,DDR 的数据时钟工作在1 600 MHz 的频率下;

(3) VDMA,用于提供高带宽的直接地址存储访问,可以在Microblaze 配置完成的情况下,进行视频数据的缓存搬运;

(4) Vid Pattern,逻辑上存储了几幅视频画面,可以通过MB 进行选择输出;

(5) DP tx subsystem,实现DP 协议的编码模块,除了main link 的视频数据编码外,还具备接收Sink TX HPD的触发,TX AUX Channel 通道数据访问交互功能;

(6) DP rx subsystem,实现DP 协议的解码模块,除了解码main link 上的数据信号外,还具备RX HPD 触发Source 功能,可以与Source 进行AUX 数据交互,存储接收端EDID 的功能;

(7) DisplayPort Video Phy,实现DP Phy 的功能,主要包括串行链路的时钟倍频、串行数据与并行数据的相互转化功能、8B/10B 编解码、时钟恢复等功能;

(8) DP Port,DP 插座模块。

5 测试与验证

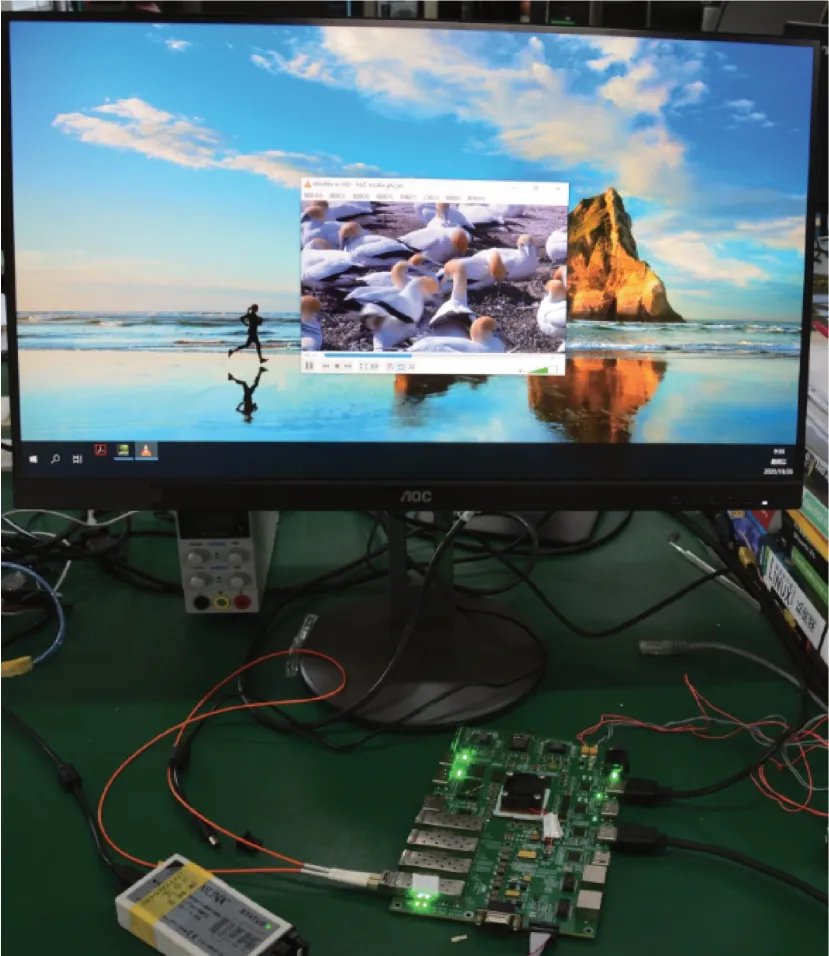

测试验证平台如图11 所示,由PC 产生DP 视频信号,经过ARINC818 编码,通过光纤返回到板卡中,再由ARINC818 解码,转换成DP 视频进行输出显示。本系统自回环测试实物图如图12 所示。

图11 测试验证平台示意图

图12 ARINC818 自回环测试图

6 结论

ARINC818 专注于航空电子环境下视频传输的应用要求,采用单向点对点数据传输,不需要实现链路初始化、流量控制以及交换注册等操作,最大限度地保证了光纤通道的高速、高可靠、低延迟等特点。本系统基于Xilinx K7 系 列FPGA GTX 高速端 口,采用10 Gb/s 链 路速率,实现了4K 分辨率的ARINC818 视频传输,支持4K@30 Hz 和4K@60 Hz 视频规格,通过DP 接口完成视频收发验证。本系统具有一定的通用性,通过配置ICD,可适应不同规格视频传输,满足各类应用需求。