一种用于频率驾驭系统的快速捕获锁相环设计

2024-03-20郭永刚蔡志伟王世伟陆昉

常 健,郭永刚,蔡志伟,王世伟,陆昉

(中国空间技术研究院 兰州空间技术物理研究所,甘肃 兰州 730000)

0 引言

锁相环技术广泛应用于通信、导航、医疗、国防军工以及天文观测等各个领域,这些领域的发展对锁相环路的指标提出了更高的要求,因此开展锁相环技术研究具有重要意义[1-2]。模拟锁相环主要由检相器、环路滤波器和压控晶振(Voltage Controlled Oscillator,VCO)三部分构成。捕获时间是指环路从非锁定状态进入锁定状态所需时间,是锁相环的主要指标之一[3]。传统模拟锁相环的捕获时间取决于输入频率跳变的大小以及环路带宽,增大环路带宽可以加速环路锁定,但会降低环路对杂波和相位噪声的抑制,甚至导致环路不稳定,因此如何加速环路锁定且保证环路对杂波、谐波和相位噪声的抑制是锁相环技术研究的重要方向之一。

现有多种辅助捕获技术用以缩短捕获时间,比如频率扫描法将一个恒定摆动的电流注入环路滤波器,在VCO 压控端产生斜坡电压实现对VCO 频率的扫描,当VCO 输出频率扫描到与输入信号一样时,环路锁定[4-7]。但是此方法实现过程中,VCO 频率扫描速度大于rad/s2时存在即使扫描到输入信号频率也不锁定的情况,此情况发生的概率与环路阻尼有关[3]。此外还有借用鉴频器进行频率捕获,此方法在非锁定状态时,由鉴频器构成的自动频率控制环路将VCO 频率调节到接近输入信号频率,此后锁相环路将VCO 相位锁定[8]。此方法电路结构复杂,其自动频率控制环路在输入信号信噪比足够大的条件下捕获才能实现。

通过对上述两种方法的分析,本文提出了一种新的快速捕获的方法,并完成了相关电路的设计。该电路可根据检相器输出信号动态调整环路滤波器的阻值,从而改变环路带宽。在环路处于未锁定状态时,增大环路带宽以实现快速捕获;当环路锁定后,减小环路带宽以抑制环路的杂波、谐波以及相位噪声。

1 锁相环基本理论

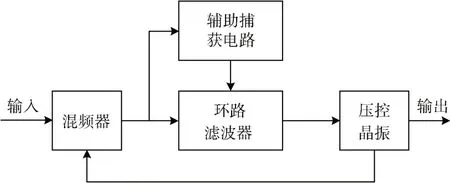

模拟锁相环由检相器、环路滤波器和压控振荡器构成,如图1 所示。

图1 锁相环基本框图

输入和输出信号的相位分别用θi(t)和θo(t)表示,角频率分别为ω1和ω2,当检相器是线性且环路锁定时,检相器输出误差电压为:

其中Kd是检相器的增益,相位误差定义为:

误差电压经过环路滤波器处理输出一个控制电压用以控制VCO 频率从而减小输入信号和VCO 之间的相位差。假设VCO 的压控系数为K0,其输出相位与压控电压关系为:

环路滤波器如图2 所示,其传递函数可以表示为

图2 环路滤波器

其中,τ1=R1·C,τ2=R2·C。

锁相环开环传递函数为:

锁相环电路传递函数为:

式 中ξ为阻尼系数,ωn为固有频率,由ξ和ωn可以推算出:

频率误差从初始频率误差Δω变化到锁定极限K所需的时间被定义为捕获时间,捕获时间还与锁相环电路参数有关,其关系为:

环路滤波器输出电压与频差的关系为:

当|Δω| ≫K时,捕获时间为[3]:

其中K为环路增益且K=。

相位噪声是锁相环的主要指标,研究锁相环相位噪声来源及其传递模型对抑制相位噪声至关重要,因此,本文建立了锁定状态下锁相环的噪声模型如图3 所示[10]。

图3 相位噪声模型

锁相环输出信号的噪声的功率谱密度可以表达为[11]:

式 中Sin(ω)、SVCO(ω)、Slpf(ω)、Spd(ω) 分别是 输入信 号、晶振、环路滤波器以及检相器的相位噪声的功率谱密度;ω=2πf,A(s)=H(s),B(s)=1-H(s)。

信号的单边带相位噪声L(Δω)可以由功率谱密度计算出来[12],关系如式(12)所示。

式中,P为信号总功率,P(ω0+Δω,1 Hz) 为频率偏移Δω处1 Hz 内单边带噪声功率,与功率谱密度的关系如下:

2 锁相环电路设计

本文设计的快速捕获锁相环主要由混频器、环路滤波器、压控晶振以及辅助捕获电路构成,其结构如图4所示。

图4 快速捕获锁相环框图

其工作原理为:初始状态,输入频率信号和晶振输出存在频差,两个信号经过混频后输出误差电压,此电压与两个信号频差呈正比关系,再经过环路滤波器滤除误差电压中的高频成分,输出的直流电压控制压控晶振的输出频率发生变化,使得晶振频率向输入频率靠近。由于双平衡混频器输出电压较小,当输入信号和晶振频差较大时,环路滤波器需要花费较长时间去调整到环路锁定所需电压。因此,通过在传统锁相环电路的基础上加入辅助捕获电路,此电路可根据混频器输出信号动态调整环路滤波器的阻值,从而改变环路带宽。在环路处于未锁定状态时,增大环路带宽以实现快速捕获;当环路锁定后,减小环路带宽,以降低环路输出相位噪声。

2.1 环路滤波器设计

环路滤波器采用有源滤波器。由式(10)可知,可以通过调整环路滤波器中电容和电阻改变捕获时间。由于改变电容会破坏环路滤波器对频率的记忆,本设计采用带宽法实现辅助捕获,即通过调整环路滤波器中的电阻改变捕获时间,电路原理如图5 所示。

图5 环路滤波电路原理

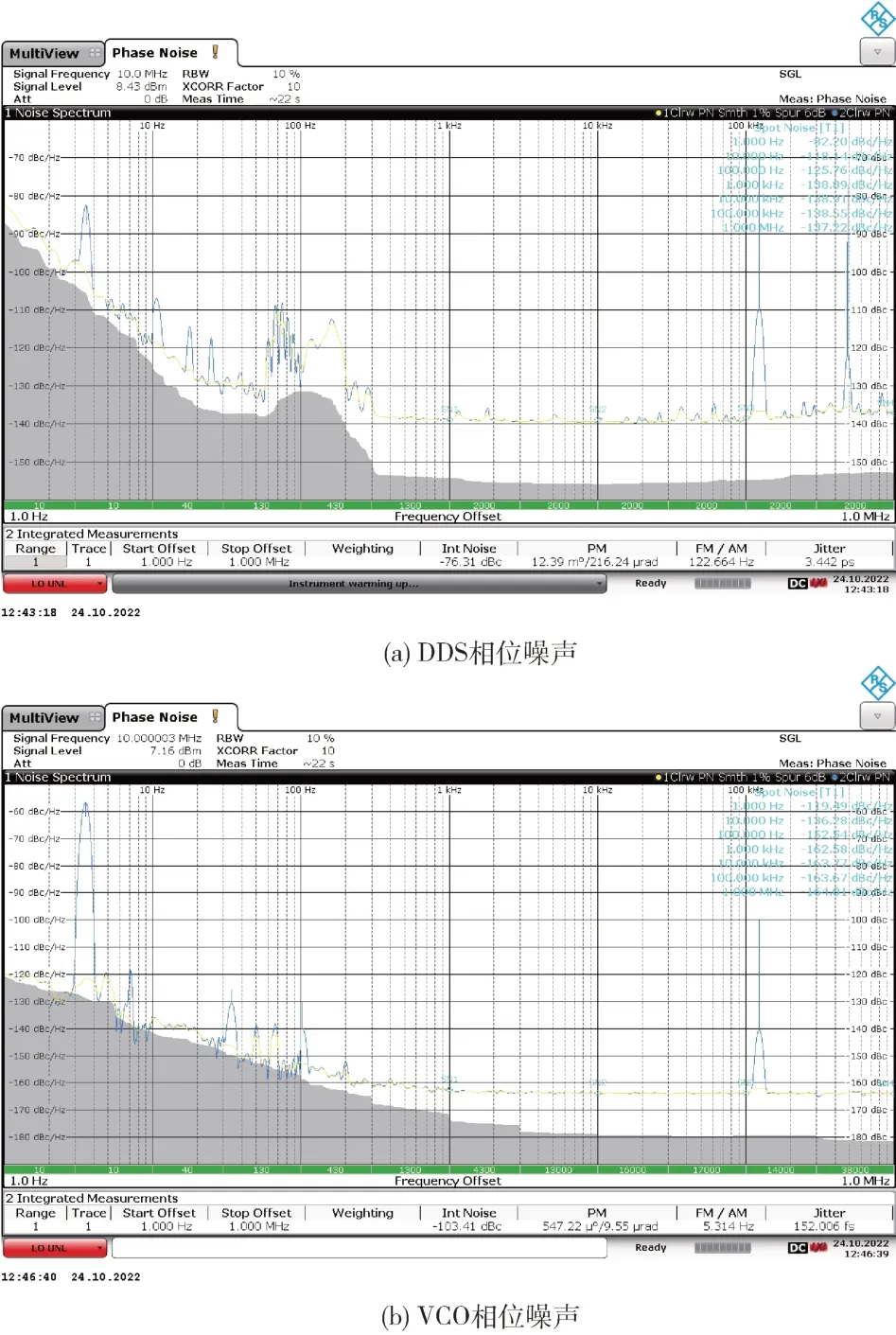

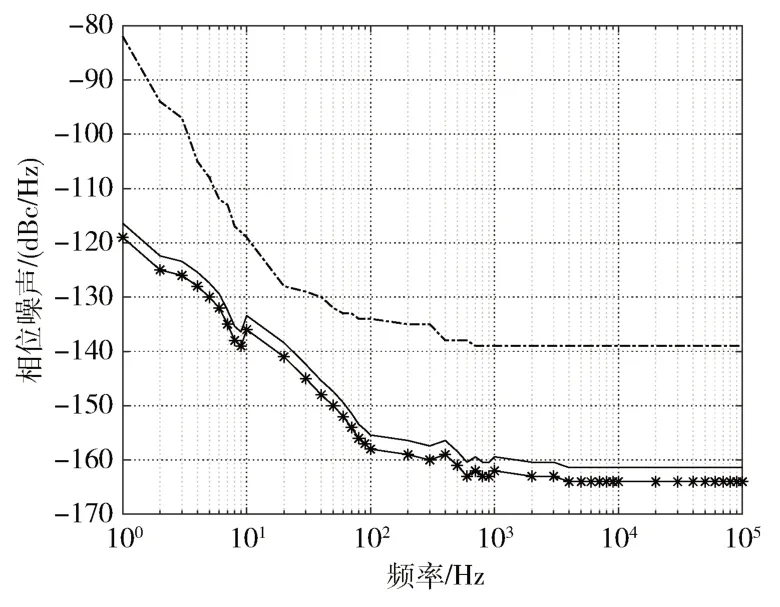

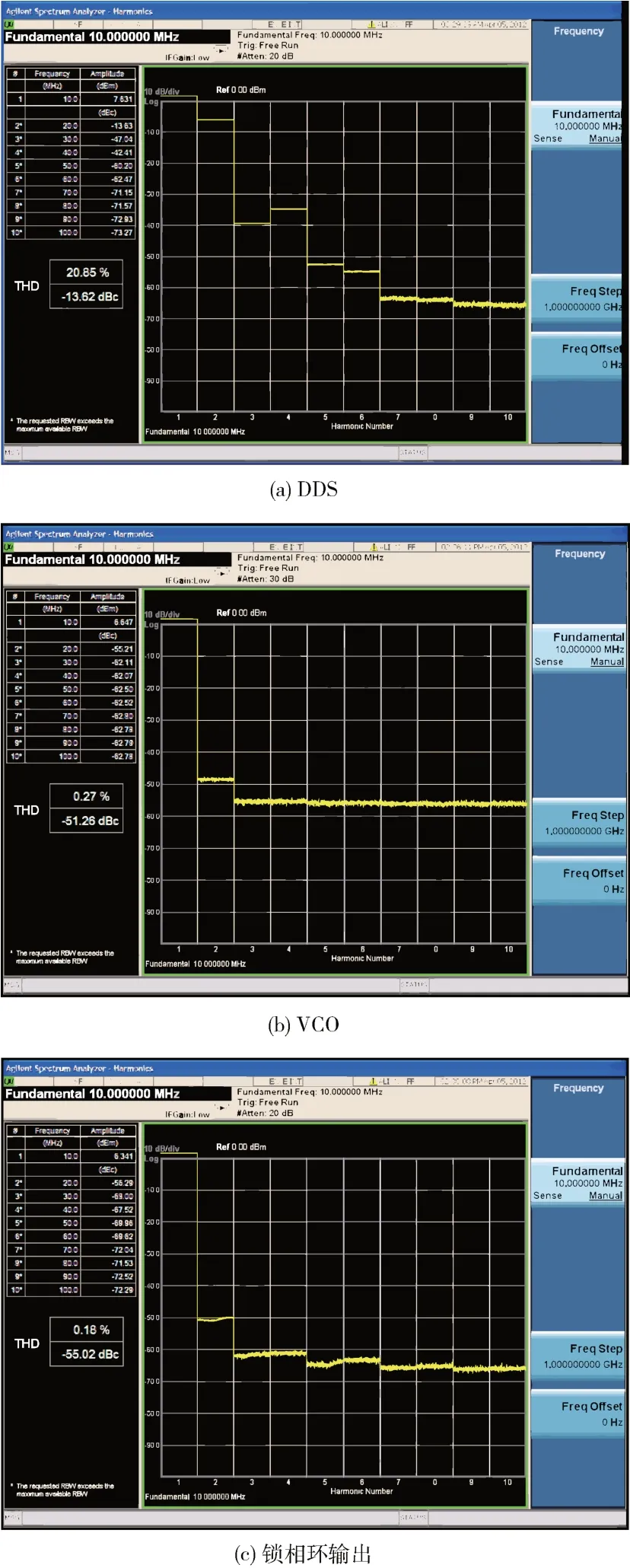

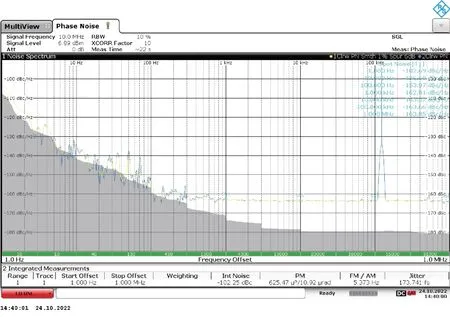

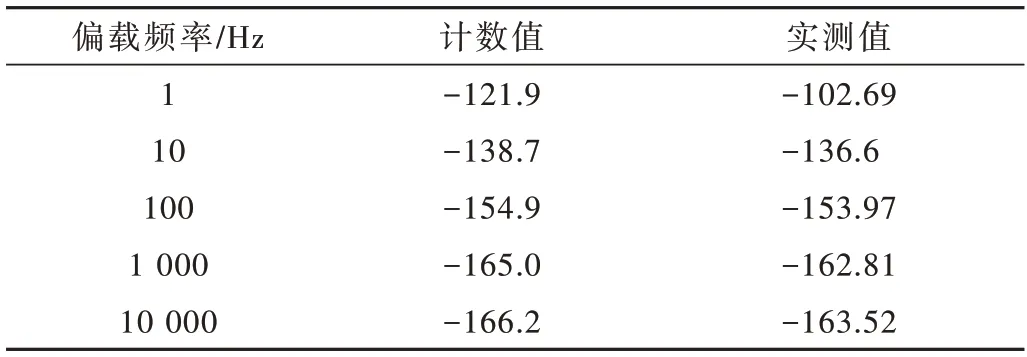

图5 中R3 环路滤波器的设计应该确保环路稳定,其中R1、R2以及C的选择还需使得环路输出相位噪声最优[14-15]。环路滤波器设计阶段主要考虑输入信号和晶振引入的相位噪声。为确定环路滤波器的参数,先对锁相环的输入信号及晶振的相位噪声进行测量,测试结果如图6 所示。 图6 单边带相位噪声 本设计中,取阻尼系数ξ=0.51,将输入信号及晶振的相位噪声测量结果代入式(11)中,计算环路输出相位噪声与ωn之间的关系,计算结果表明,ωn=π/3 时环路输出噪声最优。 本文中Kd≈0.3,K0≈5π/3,选取环路滤波器电容的容值1 μF,根据式(7)可以计算得到环路滤波器参数: 环路滤波器噪声主要来源于两个电阻及运放,环路滤波器的噪声模型如图7 所示。 图7 中,en和in是运放的等效输入噪声电压和噪声电流,eR1和eR2分别是电阻R1和电阻R2的热噪声,且=4kTR。k是玻尔兹曼常量,T是绝对温度。 环路滤波器的噪声功率谱密度可以表示为[16]: 忽略检相器带来的噪声,将式(15)带入式(11)中即可得到环路的噪声模型。图6 所示相噪分析仪测量DDS 和晶振相位噪声测量谱线比较杂乱,将长期多次的测量结果平滑滤波后带入相位噪声模型,计算锁相环锁定时环路输出信号相位噪声,结果如图8 所示。 图8 相位噪声仿真结果 由仿真结果可以看出,本文设计的锁相环中晶振相位噪声小于锁相环输入信号相位噪声,锁相环输出信号的相位噪声主要取决于压控晶振相位噪声。 为测试本设计的效果,采用DDS 输出信号作为锁相环输入,测试锁相环输出谐波、杂波、捕获时间及其相位噪声指标。其中,谐波、杂波测量选用安捷伦的E4440A频谱分析仪,相位噪声测试选用罗德施瓦兹的FSWP 相位噪声分析仪。 对锁相环输入信号和晶振输出信号以及锁相环输出信号的谐波测试结果如图9 所示。 图9 谐波测试结果 锁相环输入信号和晶振输出信号以及锁相环输出信号高次谐波的功率如表1 所示。 表1 谐波测试数据(dBc) 由测试结果可以看出,锁相环输出信号总谐波失真相对锁相环输入信号减小,谐波抑制优于-55 dBc。锁相环输入信号和晶振输出信号的谐波都被抑制,这是因为谐波与基波距离较远,锁相环的低通滤波就可以很好地抑制谐波。 置频谱仪的中心频率为10 MHz,扫频宽度为10 MHz,分辨率带宽为1 Hz。对锁相环输入信号和晶振输出信号以及锁相环输出杂波测试结果如图10 所示。 图10 杂波测试结果图 环路的杂波来源包括:检相器输出高频干扰、电源纹波、电路板布局布线串扰以及工作环境。本文采用双平衡混频器作为检相器,其相对电荷泵锁相环具有较好噪声处理能力。如图10 所示,环路锁定后可以明显看到对环路输入信号中杂波的衰减效果,杂波抑制优于-90 dBc。 锁相环从一个指定频率跳变到另一个指定频率(在给定的频率误差范围内)所用的时间就是捕获时间[13]。本文用频率发生器E8257D 做锁相环的输入信号,设置锁相环输入频率跳变1 Hz,当R1=3 MΩ 时,环路不能锁定;当R1=10 kΩ 时,环路滤波器输出电压变化如图11所示。 图11 锁定时间测量结果图 从图11 中可以看出,在锁相环锁定状态下输入频差时,晶振压控电压发生变化。由此可知,锁相环输入频差1 Hz 时,锁相环的捕获时间约为5.71 ms。 对锁相环锁定状态下输出信号的相位噪声测试结果如图12 所示。 图12 锁定状态下输出信号相位测试结果 从图12 中看出,相位噪声谱线在60 Hz 附近有几个尖峰,主要源于电源干扰。将DDS 输出信号和晶振输出信号相位噪声测量结果代入式(11),计算锁相环锁定时环路输出信号相位噪声与实测结果对比如表2 所示。 表2 相位噪声计算值与实测结果对比(dBc) 由于锁相环噪声模型未考虑检相器给锁相环输出带来的噪声,在1 Hz 处相位计算结果与实测结果有偏差,锁相环输出信号的相位噪声理论计算结果与实测基本符合。 本文介绍了一种模拟锁相环辅助频率捕获方法,根据检相输出信号动态调整环路滤波器的阻值以改变环路带宽,进而实现快速频率捕获。首先通过数学模型介绍了锁相环的工作原理,明确了捕获时间与环路参数的关系。然后,设计电路验证快速捕获方法的可行性及其指标。通过实验测试,在锁定状态下,环路杂波抑制优于-90 dBc,谐波抑制优于-55 dBc。此外,本文分析了锁相环的噪声来源,并建立环路相位噪声的数学模型,通过数学模型计算相位噪声结果与实验测试结果相近,验证了相位噪声模型的正确性。通过本文设计辅助捕获电路可以很好地解决锁相环中相位噪声和捕获时间两个指标之间的制约关系,并在铷铯组合钟的频率驾驭模块中应用。

2.2 环路滤波器噪声分析

3 试验结果

3.1 谐波测量

3.2 杂波测量

3.3 捕获时间测量

3.4 相位噪声测量

4 结论