多逻辑比特表面码结构设计及其逻辑CNOT 门实现*

2024-03-19权东晓吕晓杰张雯菲

权东晓 吕晓杰 张雯菲

1) (西安电子科技大学通信工程学院,西安 710071)

2) (西安电子科技大学,量子信息协同创新中心,西安 710071)

量子计算因具有并行处理能力,相比于经典计算有着指数级的加速,但量子系统具有脆弱性,极易受到噪声的影响,量子纠错码是克服量子噪声的有效手段.量子表面码是一种拓扑稳定子码,由于其结构上的最近邻居特点和较高的容错阈值,表面码在大规模容错量子计算方面具有巨大的潜力.目前已有的基于边界的表面码均为编码一个逻辑比特的表面码,本文主要研究基于边界如何实现多逻辑量子比特的编码,包括设计表面码的结构,根据结构找出对应的稳定子和逻辑操作,进一步根据稳定子设计出基于稳定子实现的编码线路;在研究基于测量和纠正的单量子比特间CNOT 实现原理和基于融合操作和分割操作的单逻辑量子比特表面码间CNOT 门实现原理的基础上,优化了基于融合操作和分割操作的单逻辑量子比特表面码间CNOT 门实现方案,将其扩展到所设计的多逻辑量子比特表面码上实现了多逻辑量子比特表面码之间的CNOT 操作,并通过仿真验证量子线路的正确性.本文设计的多逻辑比特表面码克服了单比特表面码不能密铺于量子芯片的缺点且提高了某些逻辑操作的长度,提高了容错能力.基于联合测量的思想降低了对辅助比特的要求且减小了实现过程中对量子资源的需求.

1 引言

1.1 研究背景及意义

1982年,Feynman[1]首次提出了量子计算的概念,它是运用量子力学的规律,对量子数据比特进行调控的一种新型的计算方式.量子计算机在解决一些超复杂的问题时其性能要远优于经典计算机,例如NP 难题,当N很大时经典计算机无法解决,但使用Shor 量子算法[2]可以将其转化为P 问题而解决.因此,对量子计算机的研究和容错量子计算的应用已经成为亟待解决的问题.2012年,Preskill[3]提出了“量子霸权”,他指出如果可以将量子计算机拓展到50 个量子位上,那么量子计算机的计算能力将超过世界上所有的计算机.相比于经典计算的线性计算方式,量子计算[4–7]可以实现并行计算,它们之间的区别是: 经典n比特只能表示 2n个状态中的一个状态,而n量子比特可以同时表示 2n个状态的叠加态,因此能够实现并行计算.但是量子比特具有脆弱性,在量子计算过程中很容易受到噪声的影响.量子纠错码[8–10]将信息量子比特编入纠缠量子比特中,这样当量子比特在存储、传输和计算过程中发生错误时,我们能够通过测量物理比特之间的关系而推断具体的错误,因此量子纠错码成为发展量子计算机的必要条件.

由于量子表面码的物理量子比特被放在拉丁格中,稳定子只关系到附近的几个量子比特,因此稳定子的测量也只和附近的几个量子比特有关,有利于物理实现.因此表面码成为实现容错量子计算的重点研究对象之一,谷歌、IBM、Intel 和中国科学技术大学等目前公开的量子芯片结构都利于表面码的实现[11–14].表面码主要包括基于边界的表面码和基于缺陷的表面码[15],基于缺陷的表面码可以通过删除更多的稳定子构造内部边界而编码多个逻辑量子比特,而基于边界的矩形结构的表面码只能编码一个逻辑量子比特.随着可编码逻辑量子比特的增多,传输和处理的信息也会随之增多.因此,设计使用少量的物理量子比特来编码多位逻辑比特的编码方案是一项十分具有意义的研究.

CNOT 门是通用量子计算中一个非常重要的逻辑门,目前已有研究表明可以基于表面码的融合和分割操作来实现编码单逻辑量子比特的表面码之间的CNOT 操作[16].本文首先对已有研究方案提出优化,然后研究如何将CNOT 门的实现方法扩展到编码多逻辑量子比特的表面码之间.利用边界编码多个逻辑比特能够实现量子比特的密铺,在一定程度上降低对物理比特的需求,提高编码效率,从而可以降低量子计算实际实现的复杂性和难度.CNOT 门的实现可为容错量子计算提供基础,因此本文的研究对量子计算具有重要的理论意义.

1.2 研究现状

1995年,Shor[9]首先提出了量子纠错码的概念,并提出了用9 个物理量子比特编码1 个逻辑量子比特,可以纠正任意单比特错误的码距为3 的[9,1,3] Shor 码.1996年,Steane[10]提出了量子纠错方案的一般表述,并提出了用7 个物理量子比特编码1 个逻辑量子比特,可以纠正任意单比特错误的码距为3的[7,1,3] Steane 码.表面码是由Kitaev[17–19]提出的复曲面码发展演变而来的,在复曲面码的基础上,Kitaev 和Bravyi[20]以及Meyer和Freedman[21]分别发展出了平面版本的量子码模型.2003年,Preskill 等[22]发现了表面码优良的容错性,并通过堆叠多层表面的三维结构实现了逻辑CNOT 操作.2006年,Raussendorf 等[23]发现通过编织变换可以在单个表面上实现逻辑CNOT操作,并评估了错误率阈值.2008年,邢莉娟等[24]给出了CSS 量子卷积码的一种新型编译码方法,该方法描述了编译码网络结构,将码字的基态转换为信息多项式与生成多项式的乘积,利用量子态上的多项式乘法操作实现了编译码网络.Flower 等[25]于2009 年提出了基于表面码的高阈值通用量子计算,其二维近邻耦合量子比特晶格结构,接近1%的高错误率阈值,自然的非对称和可调强度错误校正,以及低开销、任意长度逻辑门的特性,使其成为迄今为止最好和最实用的量子计算方案.同年,一种基于超导硬件的表面码架构被 DiVincenzo[26]提出.2012年,Fowler 等[15]使用编织等方法,在表面码上实现了逻辑通用门集,包括逻辑CNOT 门、逻辑H 门等,并且全面阐述了表面码量子计算的相关内容.同年,Horsman 等[16]实现了表面码晶格的融合和分割,进而实现了通用的量子计算.

2014年,Tomita 和Svore[27]在真实量子噪声下研究了表面码的编码问题,提出如何减少编码所用门的数量和时隙.2017年,Brown 等[28]提出了一个统一的框架来描述表面码编码方法,包括用表面码的角落扭曲缺陷,基于此提出了一种新的逻辑编码方法,同时利用码变换,在不减小码距的情况下,实现了通用逻辑门集.2018年,Litinski 等[29]提出了一种基于表面码旋转操作的容错量子计算方案,该方案消除了单量子比特Clifford 门的时间开销,实现了远程多目标CNOT门,其时间开销仅随控制目标的分离而呈对数缩放.同年,Krylov和Lukac[30]提出用于量子电路设计的量子进化算法.2020年,Beaudrap 和Horsman[31]提出用量子计算图解语言the ZX calculus 与表面码中的晶格操作建立联系,使纠错操作更加直观,并且能在大规模范围下验证,从而实现更细粒度的晶格操作和纠正;Camps 和van Beeumen[32]提出了使用编码块近似完成了量子线路合成.Shirakawa 等[33]于2021 年提出了一种量子经典混合算法来编码给定的量子态.同年,Wang 等[34]基于机器学习的思想,构建了一个卷积神经网络译码器来纠正复曲面码中的错误,译码器的阈值精度达到10.8%,更接近于最优阈值.2022年,Marques 等[35]研究出了一种在表面码中进行错误检测的逻辑量子位运算方法;Kumari 等[36]提出了一种双面环形码,可以用n个数据量子比特编码至少n/3 个逻辑量子比特;Chen 等[37]提出了一种仅由 Clifford 门组成的系统高效的量子电路来模拟表面码模型的基态,能够在任意平面晶格上实现二维复曲面编码的基态;Chen 等[38]提出了一种面向量子通信系统的低开销容错纠错方案,该方案简化了电路深度开销和辅助量子态开销,且适用于通用量子稳定子码.此外,Xue 等[39]提出了一种基于周期性表面码强化学习的量子信息保护方案;Ding 等[40]提出了一种基于量子拓扑稳定子彩色码形态的神经网络译码方法,该方法将彩色码投射到表面码上,利用深度Q 网络对彩色码的解码过程进行迭代训练,在训练后可以达到较快的预测速度和较好的纠错阈值.2023年,Siegel 等[41]提出了一种用于缺陷晶格表面码量子纠错的新型自适应方法,结合适当的缺陷检测算法和对已识别区域的隔离,可以保留有限码大小的量子纠错优势.从以上介绍能看出,不管是在理论上还是实验实现上量子表面码都得到了广泛的重视,取得了快速的发展.但是,量子计算理论和实际实现之间的障碍仍然无法跨越,研究如何提高编码效率以及如何实现通用量子门集对容错量子计算的最终实现具有重要的理论意义.

2 基于边界的多逻辑比特量子表面码结构及编码线路设计

2.1 单逻辑比特表面码结构

表面码由一些具有特定拓扑结构的量子比特构成,包括最早提出的表面码以及旋转45°后形成的更节省物理比特的表面码[16].图1 为一个码距为3 的旋转表面码.

图1 3 × 3 表面码的结构图Fig.1.Structure diagram of 3 × 3 surface code.

如图1 所示,白色比特为数据比特,黑色比特为测量比特,黄色区域为X型稳定子,包括:X1X2X4X5,X2X3,X7X8,X5X6X8X9;绿色区域为Z型稳定子,包括Z1Z4,Z2Z3Z5Z6,Z4Z5Z7Z8,Z6Z9.可以看到不同类型的稳定子间都有 0 个或 2 个共同的数据比特,而同类型的稳定子本身互相对易,因此所有稳定子之间满足对易性;任何一个稳定子都不能由其他稳定子直积得到,因此也满足独立性.稳定子码编码的逻辑比特的数目等于物理比特数目和稳定子数目的差,因此,图1 可以编码1 个逻辑比特.

表面码有两种边界:X边界是由X型稳定子所形成的边界,Z边界是由Z型稳定子所形成的边界.连接两个X边界且与所经过的每个Z型稳定子有偶数个共同数据比特的连线上的所有数据比特X操作的直积就是X逻辑操作XL,信息比特要选择XL所涉及的量子比特;类似地连接两个Z边界且与所经过的每个X型稳定子有偶数个共同数据比特的连线上所有数据比特Z操作的直积就是Z逻辑操作ZL.据此,可以写出图1 中表面码的X逻辑操 作:XL1=X3X5X7,XL2=X2X5X7,XL3=X3X5X8,XL4=X2X5X8;Z逻辑操 作:ZL1=Z1Z5Z9,ZL2=Z4Z5Z9,ZL3=Z1Z5Z6和ZL4=Z4Z5Z6.容易验证,X逻辑操作和Z逻辑操作与所有的稳定子对易,两者反对易.

2.2 一种可以编码3 位逻辑比特的表面码

2.2.1 表面码结构设计

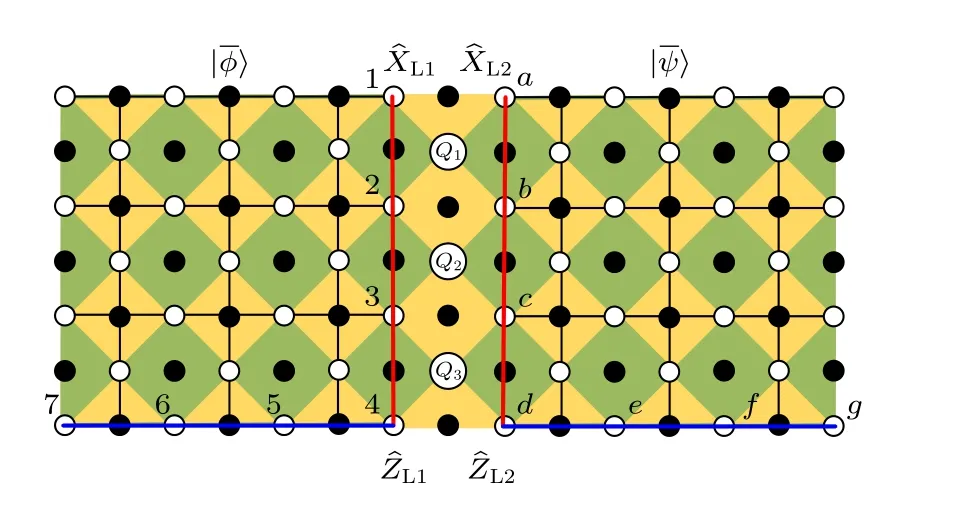

在表面码中,数据比特个数与稳定子个数之差等于可以编码逻辑比特的个数,所以想要同时编码多位逻辑比特,可以固定数据比特的个数后减少稳定子的个数.减少稳定子个数的方法有两种: 一种是在表面码内部采用“挖洞”的方式来减少稳定子个数,实际上是构造内部边界;另一种是构造更多的互相交替的外边界,能够形成更多连接同类型边界的逻辑操作,从而可以编码多个逻辑比特.经典的表面码结构包含 2 个X边界和2 个Z边界,X稳定子数目与Z稳定子数目相等,可以编码一位逻辑比特.

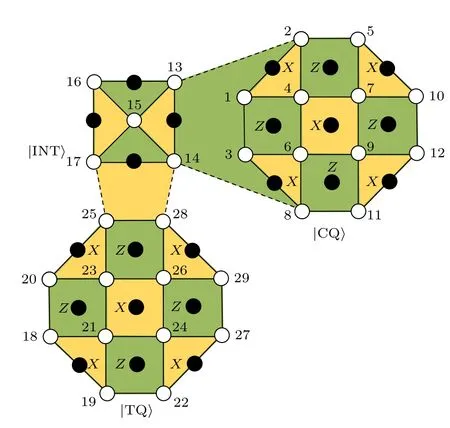

本文提出了一种基于边界可以同时编码三位逻辑比特的表面码结构,该表面码结构如图2 所示,由 12 个数据比特构成,包含 5 个X型稳定子X1X2X4,X3X6X8,X4X6X7X9,X5X7X10,X9X11X12以及4 个Z型稳定子Z1Z3Z4Z6,Z2Z4Z5Z7,Z6Z8Z9Z11,Z7Z9Z10Z12,4 个X边界和 4 个Z边界,因此可以编码3 位逻辑比特.

图2 基于边界编码三位逻辑比特的表面码结构Fig.2.Structure of surface code based on boundary encoding three logical qubits.

2.2.2 逻辑操作的选择

逻辑操作的选择需要满足以下原则: 第一,逻辑操作要与所有的稳定子对易;第二,Z逻辑操作ZLi要与相应的X逻辑操作XLi反对易,同时与编码其他逻辑比特的X逻辑操作XLj(ji) 对易;X逻辑操作XLi要与相应的Z逻辑操作ZLi反对易,同时与编码其他逻辑比特的Z逻辑操作ZLj(ji)对易.在该表面码中,边界是互相交替的4 条X边界和4 条Z边界,但它们是不独立的.理论上可以选择其中的 3 个Z边界作为逻辑X操作,3 个X边界作为逻辑Z操作,但是当固定了X逻辑操作后,会出现Z逻辑操作同时与两个X逻辑操作反对易的情况,因此逻辑操作不能全部选择最短的.这里第3 个逻辑Z操作选择为:ZL3=Z8Z6Z4Z2,或将其等价到边界上,写成=Z8Z3Z1Z2.最终选择的逻辑操作见表1.

表1 图2 所示表面码的逻辑操作Table 1.Logical operation of the surface code shown in Fig.2.

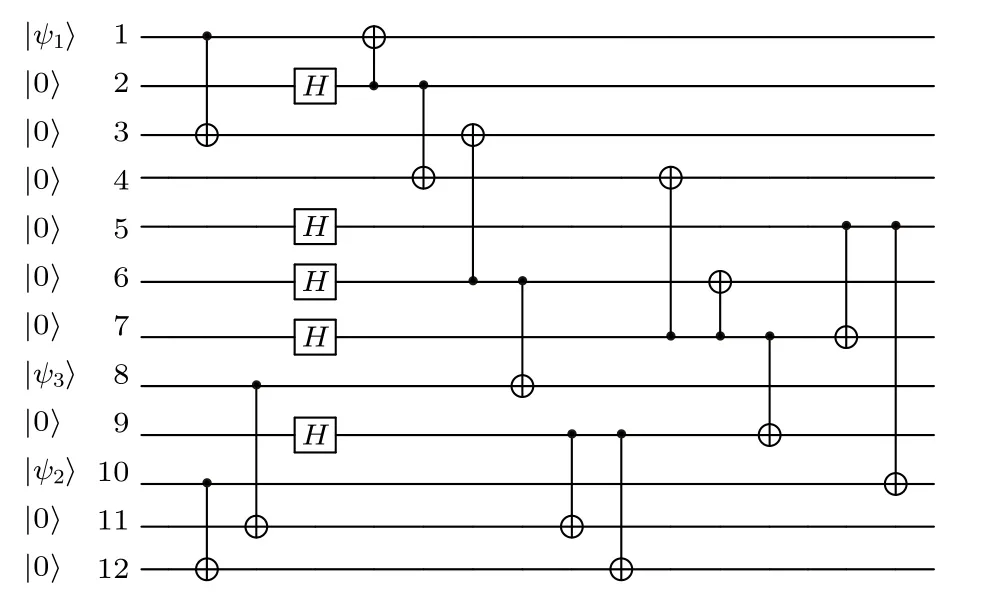

2.2.3 编码线路的设计与仿真

编码线路主要包括基于稳定子测量和纠正的编码线路[15]以及基于稳定子实现的编码线路[42].因为基于稳定子测量的编码线路总是随机地塌缩,需要根据测量结果进行纠正操作才能正确编码,消耗的资源较多,本文基于稳定子的实现设计编码线路.选定物理比特1,10,8 作为信息比特,编码线路的第1 部分是逻辑操作的实现,即利用信息比特控制相应的逻辑操作的其他比特;接下来利用H 门和CNOT 门逐个实现X型稳定子,得到的编码线路如图3 所示.

图3 图2 所示编码三位逻辑比特表面码的编码线路图Fig.3.Quantum encoding circuit for the surface code shown in Fig.2.

3 基于融合与分割的单逻辑量子比特表面码间CNOT 门实现的优化

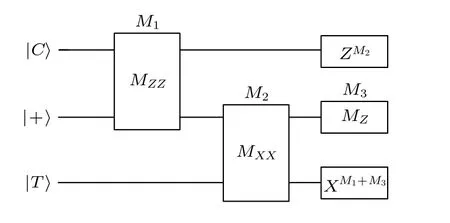

3.1 基于联合测量的单量子比特间CNOT门实现方法

图4 是利用联合测量在单量子比特之间实现CNOT 门的原理图,|C〉是控制位,|T〉 是受控位,实现过程中需要一个额外的初始化为 |+〉 的辅助比特M.实现过程分为4 步: 第1步,对控制位|C〉 和辅助比特M进行Z基下的联合测量,结果为M1;第2步,对辅助比特M和受控位|T〉 进行X基下的联合测量,结果记为M2;第3步,对辅助比特M在Z基下进行测量,结果为M3;第4步,根据前3 步的测量结果,在控制位 |C〉添加逻辑门ZM2,在受控位|T〉添加逻辑门作为纠正操作,即当M2=1时,添加Z门,当M1+M3=1时,添加X门.

图4 基于联合测量的单量子比特间CNOT 门的实现原理Fig.4.CNOT gate implementation for single qubit based on joint measurement.

图5 表面码的粗糙融合Fig.5.Rough fusion of surface codes.

如果结果为1,表示不满足这个稳定子,或者理解为满足稳定子-Z1Z2,这时候得到的态为

上述两种情况可以合并为

在CNOT 的实现过程中,基于上述理论进行分析,具体分析过程如下:

1) 对控制位|C〉 和辅助比特M进行Z基下的联合测量,可以得到输出态为

2) 对辅助比特M和受控位|T〉 进行X基下的联合测量,即进行稳定子X1X2测量,可以得到输出态为

3) 对辅助比特M进行Z基下的测量,可以得到输出态,见表2.

4) 根据测量结果添加纠正操作,无论哪一种情况,通过纠正操作后可以得到最后的输出结果(忽略系数)为

公司治理的产生是要解决所有者和经营者之间利益不一致而产生的委托代理关系,即公司剩余索取权和剩余控制权的分配问题,包含公司内部股东及管理层之间,也包含公司之外的因素之间的利益分配。鉴于此,现代公司治理有内部公司治理和外部公司治理之分。狭义的公司治理主要指公司中股东大会、董事会、监事会和经营管理层之间的权利制衡机制,通过有关制度,明确所有者和经营者之间的权利和责任关系,主要涉及公司的内部治理。而广义的公司治理则是通过一系列的内部制度或外部制度来制衡公司与所有利益相关者之间的利益关系,维护公司利益,实现价值最大化的目标。广义的公司治理结构,涉及内部治理和外部治理之间的协调问题。

根据输出结果,可以看到,当|C〉为|0〉时,输出 |T〉;当 |C〉为 |1〉时,输出X|T〉,符合CNOT门的逻辑功能,实现了单量子比特间的CNOT 门.

3.2 融合与分割操作

2012年,Horsman 等[16]提出了基于晶格融合与分割的方式实现逻辑CNOT 门.这里首先介绍粗糙融合、粗糙分割、光滑融合和光滑分割的原理,然后对Horsman 等[16]提出的CNOT 门的实现方法进行改进.

3.2.1 粗糙融合和粗糙分割

融合之后的状态为

上述公式不严谨,融合以后中间的3 个数据比特Q1,Q2和Q3将和左右两边的表面码是纠缠在一起的,因此(11)式表述的不够严格,因为它并没有考虑这3 个数据比特的状态.

为了便于分析,对融合过程增加的第4 个稳定子进行变形:

对量子比特Q3,Q2和Q1在Z基下进行测量,可以完成粗糙分割操作.在对Q3进行测量之后,与Q3相关的X型稳定子=X3XcXQ2XQ3因测量而消失;与Q3相关的两个Z型稳定子由四端变为三端,当测量结果为0时,三端稳定子自动满足;当测量结果为1时,需要添加X操作使这两个三端稳定子满足.同理在对Q2和Q1进行测量之后,稳定子=X2XbXQ1XQ2和稳定 子=X1XaXQ1会因为测量而消失.这时仅保留了变型过的,如图6 所示.

图6 表面码的粗糙分割Fig.6.Rough segmentation of surface codes.

图7 表面码的光滑融合Fig.7.Smooth fusion of surface codes.

通过粗糙融合和分割,实际上是对两个逻辑态进行联合逻辑测量.结合单量子比特间CNOT 门的实现原理(图4)可知,为了实现逻辑量子比特间的CNOT门,只需要联合测量和纠正操作就可以,因此粗糙融合和分割过程可以简化为对图6 所示的中间条形黄色稳定子的联合测量,这样就能够简化CNOT 的实现过程.将稳定子测量的结果记为M,稳定子测量后的量子态表示为

3.2.2 光滑融合和光滑分割

同理,对融合过程增加的第4 个稳定子变形:

对量子比特Q3,Q2和Q1在X基下进行测量,可以完 成光滑分割操 作.在X基下对Q3,Q2和Q1进行测量之后,稳定子=Z3ZcZQ2ZQ3,和会因为测量而消失,三端的X型稳定子可以通过纠正操作来满足,这时左右两个表面码由变型过的稳定子连接,如图8 所示.

图8 表面码的光滑分割Fig.8.Smooth segmentation of surface codes.

通过光滑融合和分割,实际上是对两个逻辑态进行联合逻辑测量,直接对两个逻辑态进行联合测量能够满足CNOT 门实现的需求,因此光滑融合和分割过程可以简化为对图8 所示的中间条形绿色稳定子的联合测量.将稳定子测量的结果记为M,稳定子测量后的输出态为

3.3 单逻辑量子比特表面码间CNOT 门实现的优化

经过上述分析,我们能够对基于晶格融合与分割的逻辑CNOT 门实现方案进行优化: 在原方案实现过程中,光滑融合对控制位和辅助位之间新产生的Z稳定子进行测量,它们测量结果的异或等价于联合逻辑ZL1ZL2测量的结果;粗糙融合对目标位和辅助位之间新产生的X稳定子进行测量,它们测量结果的异或等价于联合逻辑XL1XL2测量的结果.先融合后分割操作的结果是使得两个逻辑比特通过逻辑操作形成的稳定子连接成一个更大的表面码,这个新增加的稳定子可能为正也可能为负.因此,基于晶格融合与分割的逻辑CNOT 门实现方案可以简化为直接对逻辑操作形成的稳定子进行测量,再对辅助比特进行逻辑Z测量,最后添加纠正操作.下面以码距为 2,编码一位逻辑比特的表面码为例进行仿真验证.

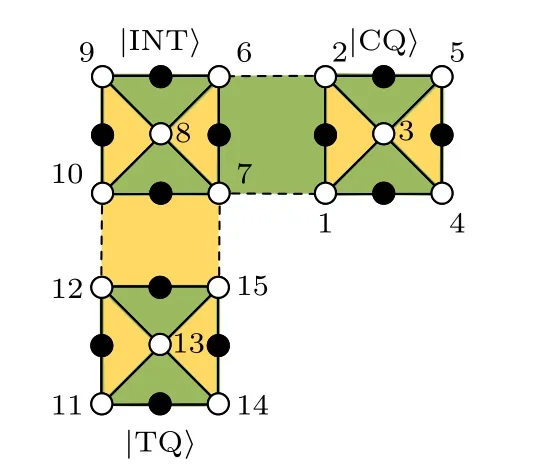

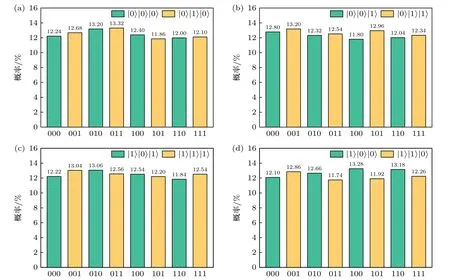

图9中,|CQ〉 代表控制位,逻辑操作分别为X2X5和Z1Z2;|TQ〉 代表受控位,逻辑操作分别为X12X15和Z11Z12;|INT〉 初始化为|+〉 作为辅 助态,逻辑操作分别为X7X10和Z6Z7.第1步,进行联合Z测量,在Z基下对控制比特和辅助比特的Z逻辑操作涉及的比特 1,2,6,7 进行联合测量,结果记为M1;第2步,进行联合X测量,在X基下对辅助比特和目标比特的X逻辑操作涉及的比特 7,10,12,15 进行联合测量,结果记为M2;第3步,在Z基下对 |INT〉 进行逻辑测量,测量结果为M3;第4步,进行校正操作,根据前3 步的测量结果,对 |CQ〉添加逻辑操作ZM2,当M2为1时,为Z1Z2;在受控位 |TQ〉添加逻辑操作XM1+M3,当M1+M3=1时,为X12X15;当M1+M3=1 且M2=1时,整体相位进行翻转.这里每个码字有4项,最终的结果是64项,是3 个逻辑态码字直积的结果.图10 记录了对每一种输入进行5000 次仿真后得到随机测量结果的概率统计以及在该种测量结果下对应的输出,其中横坐标为3 次测量的结果M1M2M3.

图9 单逻辑比特量子表面码逻辑CNOT 门的实现Fig.9.Implementation of logic CNOT gate for the single logical qubit surface code.

图10 不同输入状态下的仿真输出(a) |CQ〉 =|0〉 ,|TQ〉 =|0〉;(b) |CQ〉 =|0〉 ,|TQ〉 =|1〉;(c) |CQ〉 =|1〉 ,|TQ〉 =|0〉;(d) |CQ〉=|1〉 ,|TQ〉 =|1〉Fig.10.Simulation output under different input states: (a) |CQ〉 =|0〉 ,|TQ〉 =|0〉;(b) |CQ〉 =|0〉 ,|TQ〉 =|1〉;(c) |CQ〉 =|1〉,|TQ〉 =|0〉;(d) |CQ〉 =|1〉 ,|TQ〉 =|1〉 .

在图10中,每一个测量结果的概率都约等于12.5%,说明两个联合逻辑测量和辅助态在Z基下的测量都是随机塌缩的.对 |CQ〉 来说,输入和输出保持一致;对 |TQ〉来说,当 |CQ〉输入为0时,|TQ〉不变;当 |CQ〉输入为1时,|TQ〉 取反,符合CNOT门的结果.对 |INT〉 来说,因为M3是对 |INT〉 逻辑态的测量结果,当M3=0时,|INT〉 的测量结果为|0〉,当M3=1时,|INT〉的测量结果为 |1〉,在输出结果中,与理论分析相一致.当M1M2M3测量结果为011 和110 (M1+M3=1且M2=1)时,结果中会出现一个整体的相位翻转,因此当出现这种情况时,可在校正操作中添加一个整体的相位翻转.因此优化以后的过程能够实现逻辑CNOT 操作.

4 基于联合测量和逻辑测量的多逻辑量子比特表面码间CNOT 门的实现

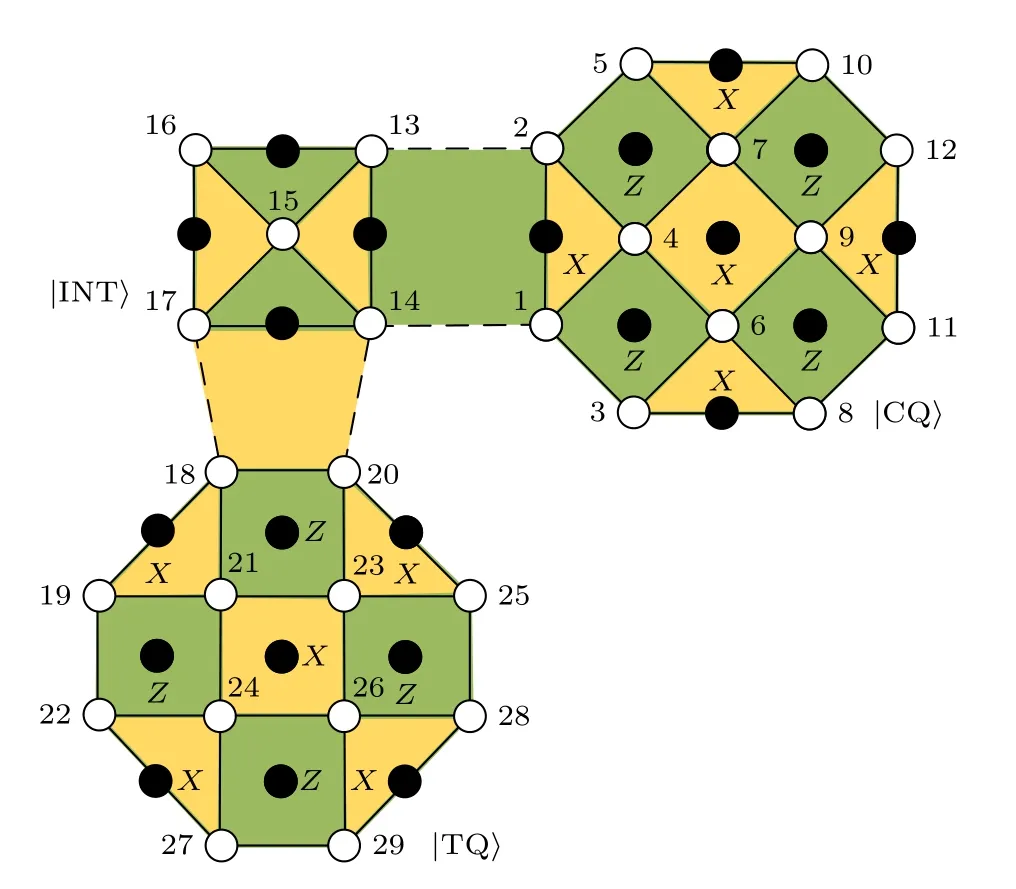

本文提出的编码多个逻辑量子比特的表面码(图2)依然可以基于联合测量和逻辑测量实现逻辑CNOT 门.|CQ〉代表控制表面码,|TQ〉 代表受控表面码,|INT〉的某一逻辑位初始化为 |+〉,作为辅助态.在编码一位逻辑比特的表面码中,只有一位比特,不需要特别关注逻辑操作的对应关系,但在编码三位逻辑比特的表面码中,要把信息比特和逻辑操作进行对应.在图2中,定义了表面码具体的逻辑操作,要实现控制表面码第i位逻辑比特与目标表面码第j位逻辑比特之间的CNOT,就要将控制表面码第i位逻辑Z操作与辅助表面码的逻辑Z操作对应,用Z型稳定子连接,将目标表面码第j位逻辑X操作与辅助比特的逻辑X操作边界对应,用X型稳定子连接.图11 给出了 |CQ〉 第一位逻辑比特利用 |INT〉第一位逻辑比特与|TQ〉第一位逻辑比特CNOT 的过程,Z1Z2和Z13Z14分别对应控制表面码和辅助表面码第一位逻辑比特的Z逻辑操作,X13X15和X25X27分别对应的是辅助表面码和目标表面码第一位逻辑比特的X逻辑操作.

图11 基于联合测量和逻辑测量的多逻辑量子比特表面码逻辑CNOT 门的实现Fig.11.Implementation of logic CNOT gate for multiple logical qubits surface code based on joint measuremnt and logical measurement.

逻辑CNOT 实现的步骤: 第1步,进行联合Z测量,在Z基下对 1,2,13,14 比特进行联合测量,结果记为M1;第2步,进行联合X测量,在X基下对 13,15,25,27 比特进行联合测量,结果记为M2;第3步,在Z基下对 |INT〉 的第一比特进行逻辑Z测量,测量结果为M3;第4步,进行校正操作,根据前3 步的测量结果,对 |CQ〉 添加逻辑操作,当M2为1时,纠正操作为Z1Z2;在受控位 |TQ〉添加逻辑操作XM1+M3,当M1+M3=1时,纠正操作为X25X27;当M1+M3=1且M2=1时,整体相位进行翻转.

在实现逻辑CNOT 的过程中,辅助比特|INT〉初始化 为逻辑 |+〉,在该过程中 |INT〉 不需要 与|CQ〉和 |TQ〉 的拓扑结构相同,在保证联合测量过程中构成逻辑操作的数据比特位数能够满足对应关系的前提下,可以将 |INT〉 进行简化.

如图12 所示,|INT〉 由码距为2 的边界表面码构成,这时候整个过程用到的量子比特数目就会减少很多,提高了CNOT 门实现的效率,并且利用普通计算机能够对此过程进行仿真.由于IBM 的Qiskit 支持的量子比特数目有限,因此在这里使用Matlab 编写了表面码的直积、基转换、联合测量、逻辑测量等函数,对上述CNOT 的过程进行了仿真,结果见表3—表6.

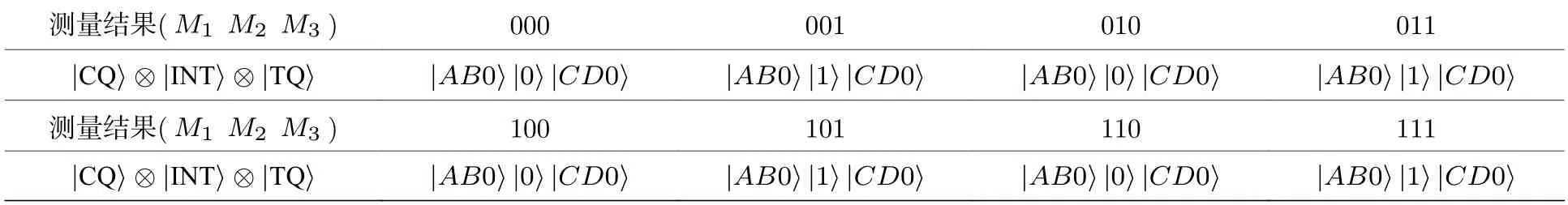

表3 |CQ〉 =|AB0〉 ,|TQ〉 =|CD0〉,(A,B,C,D ∈(0,1)) 时的输出Table 3.Output when the input is |CQ〉 =|AB0〉 ,|TQ〉 =|CD0〉,(A,B,C,D ∈(0,1)) .

表4 |CQ〉 =|AB1〉 ,|TQ〉 =|CD1〉,(A,B,C,D ∈(0,1)) 时的输出Table 4.Output when the input is |CQ〉 =|AB1〉 ,|TQ〉 =|CD1〉,(A,B,C,D ∈(0,1)) .

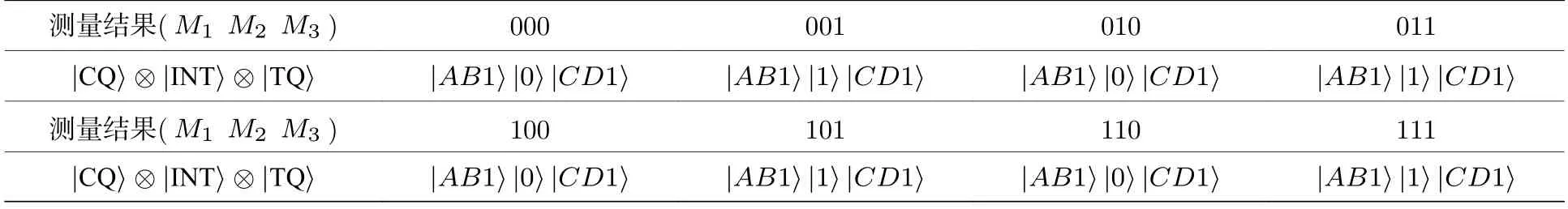

表5 |CQ〉 =|AB1〉 ,|TQ〉 =|CD0〉,(A,B,C,D ∈(0,1)) 时的输出Table 5.Output when the input is |CQ〉 =|AB1〉 ,|TQ〉 =|CD0〉,(A,B,C,D ∈(0,1)) .

表6 |CQ〉 =|AB0〉 ,|TQ〉 =|CD1〉,(A,B,C,D ∈(0,1)) 时的输出Table 6.Output when the input is |CQ〉 =|AB0〉 ,|TQ〉 =|CD1〉,(A,B,C,D ∈(0,1)) .

图12 基于联合测量和逻辑测量的多逻辑量子比特表面码逻辑CNOT 门的优化Fig.12.Optimization of logic CNOT gate for multiple logical qubits surface code based on joint measuremnt and logical measurement.

对|CQ〉 来说,输入和输出保持一致,符合CNOT 门的结果.对 |TQ〉来说,当 |CQ〉为|AB0〉,(A,B ∈(0,1))时,|TQ〉不 变;当|CQ〉为 |AB1〉,(A,B ∈(0,1))时,|TQ〉 第一位取反,说明两个表面码的第1 位逻辑比特之间实现了CNOT 操作,且在实现过程中没有影响到控制比特和目标比特的其他逻辑比特,符合CNOT 门的要求.对 |INT〉 来说,因为M3是对 |INT〉 进行逻辑Z测量的结果,当M3=0时,|INT〉塌缩为 |0〉,当M3=1时,|INT〉塌缩为 |1〉,与理论分析相一致.经过上述分析,基于联合测量和逻辑测量实现了多比特表面码之间的逻辑CNOT 门.

在图2 表面码中,逻辑比特2 和逻辑比特1 类似,因此逻辑CNOT 的实现也类似.当CNOT的控制比特和目标比特都是逻辑比特3时,由于对|INT〉只是进行逻辑比特联合测量和后续的逻辑测量,逻辑操作的数据比特位数不需要一一对应,因此 |INT〉Z逻辑操作的长度并不需要为4,仍然可以采用最小的表面码作为中间态,如图13 所示.经过仿真验证,能够实现CNOT 逻辑操作.基于简化的原理,可以设计出控制表面码的任意逻辑比特和目标表面码的任意逻辑比特之间的CNOT门,实现任意逻辑比特间的逻辑CNOT 操作.

图13 控制比特和目标比特都为逻辑比特3时,逻辑CNOT门的优化Fig.13.Optimization of logic CNOT gate when both control qubit and target qubit are the 3rd logical qubits.

5 讨论和结论

本文的主要创新包括: 第一,提出了一种基于边界可以编码3 个逻辑比特的表面码,该表面码用12 个数据比特编码 3 个逻辑比特;第二,对基于晶格融合与分割的表面码逻辑CNOT 门实现方法进行了改进,提出了一种基于联合测量和逻辑测量的表面码逻辑CNOT 门实现方法,并在提出的多逻辑比特表面码上进行了仿真验证.

编码多个逻辑比特的表面码的优点.第一,虽然本文提出的表面码结构与3 个逻辑长度相同编码单逻辑比特的表面码所用的物理比特一样多,但是在本文提出的表面码结构中有一个更长的逻辑操作,增加了表面码的容错能力.第二,对于编码单个逻辑比特的表面码,它们结构上是分离的,两个表面码之间的物理比特不能充分利用.本文的编码多逻辑比特的表面码相比于编码单逻辑比特的表面码,物理比特能够形成密铺,结构上更紧凑,在量子计算的实现过程中能更充分地利用每一个物理量子比特.第三,虽然本文给出的是长度为2 的表面码,只有检错能力没有纠错能力,但按照交替边界设计的思想能够设计出具有更长逻辑操作的表面码.这里是因为仿真的限制,因此研究长度为2 的表面码.

基于联合测量和逻辑测量的表面码CNOT 门实现方法过程更简洁,能够节省资源.这里以实现图5 所示码距为4 的表面码之间的CNOT 操作为例进行资源需求分析,基于融合和分割的方法辅助态表面码结构与图5 中的结构一致,而基于联合测量和逻辑测量的方法对辅助态没有具体要求,这里选择有纠错能力的码距为3 的表面码作为辅助态.两种方法需要的资源如表7 所列,可以发现基于联合测量和逻辑测量的方法性能优于基于晶格融合与分割的方法.逻辑CNOT 门优化方案的优点: 第一,中间辅助态的选择更灵活,可以利用码距比较小的表面码来实现,因此辅助表面码的码距和数据量子比特数目都比较小.第二,更节省量子门的数目.在基于晶格融合与分割的方法中,通过融合和分割操作,将两个表面码形成纠缠态,在基于联合测量和逻辑测量的方法中,联合测量直接完成了这个过程,联合测量的结果等价于融合与分割的结果.因此不仅简化了操作,还减少了量子门的数目.第三,在基于晶格融合与分割的方法中,需要多次对新产生的稳定子进行测量,且每次根据不同的测量结果需要进行纠正操作,还需要进行单比特的测量来消除稳定子;而优化方法中,不需要进行稳定子的测量和单比特测量,因此测量次数和纠正次数都减少.融合分割操作的优点是量子比特仅需要与相邻比特进行作用,在大码距表面码的物理实现上更容易.

表7 两种逻辑CNOT 门实现方法的资源消耗对比Table 7.Comparison of the resource consumption of the two logic CNOT gate implementation methods.

本文设计的多逻辑比特表面码克服了单比特表面码不能密铺于量子芯片的缺点,能够充分利用物理量子比特,且提高了某些逻辑操作的长度,增加了容错能力.基于联合测量的思想降低了对辅助比特的要求,简化后的实现过程减小了对量子资源的需求,高效地实现了逻辑量子比特之间的CNOT 门.本文的研究成果对通用容错量子计算的研究和实现都具有重要的意义.

附录A

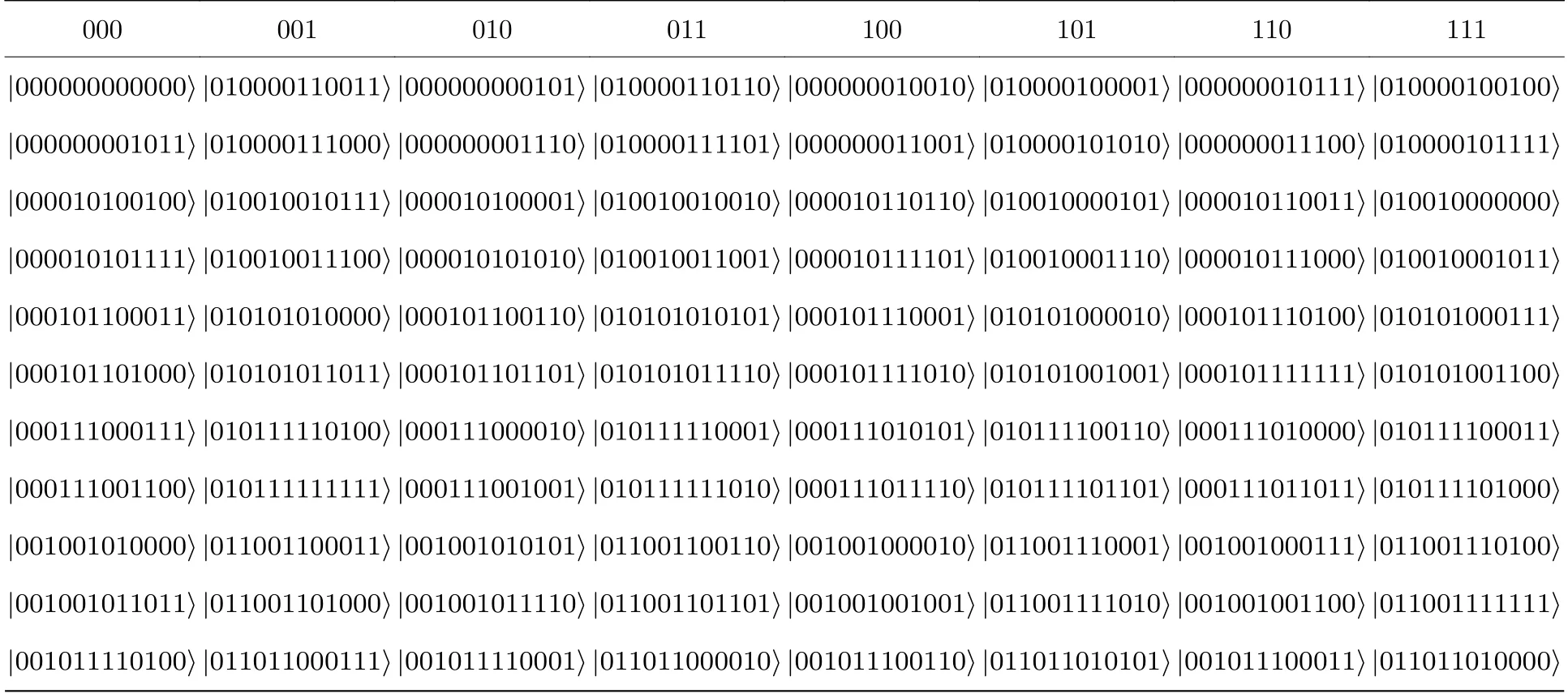

图3 所示的编码线路的8 种输出码字见表A1.

表A1 图3 所示的编码线路的8 种输出码字Table A1.Eight output codewords for the encoding circuit shown in Fig.3.