硅基芯片低空洞率底部填充工艺技术研究

2024-03-16兰元飞张鹏哲孙浩洋郭珍荣北京遥感设备研究所北京

兰元飞,焦 庆,姬 峰,张鹏哲,孙浩洋,尤 嘉,郭珍荣(北京遥感设备研究所,北京)

引言

三维倒装工艺具有集成密度高的特点,采用此工艺集成的产品高频性能优异,在电子封装领域具有显著的优势[1-2]。接收子阵是相控阵天线的重要组成部分,采用三维倒装工艺装配数十只接收硅基芯片,在内部实现天线阵面、TR 组件有源器件和馈电网络各层之间的垂直互联。硅基芯片与综合电路板之间采用焊锡球实现电气互联,与传统金丝互联相比,硅基芯片与综合电路板之间传输距离小,射频信号串扰小、传输延时短。但是综合电路板与焊锡球硬度低,硅基芯片与焊球焊点、综合电路板与焊球焊点强度小,因此硅基芯片与综合电路板间互联结构耐热冲击、机械冲击性能差[3-5]。采用底部填充胶填充在硅基芯片与综合电路板之间,填满焊球与焊球之间,可以减少由于硅基芯片与综合电路板、硅基芯片与焊球、综合电路板与焊球之间热膨胀系数差异引起的热应力以及由振动等引起的机械应力等对焊点的冲击[6-8]。低空洞率底部填充工艺技术是解决接收子阵现有三维集成后问题的关键工艺技术,对于小型化相控阵天线的研制生产具有重要意义。

1 工艺过程研究

硅基芯片底部填充的影响因素有底部填充点胶针头选型、倒装芯片清洗、底部填充胶分配模式等,本文主要对上述影响因素进行硅基芯片底部填充工艺研究,确定适宜的工艺参数。

1.1 底部填充点胶针头选型

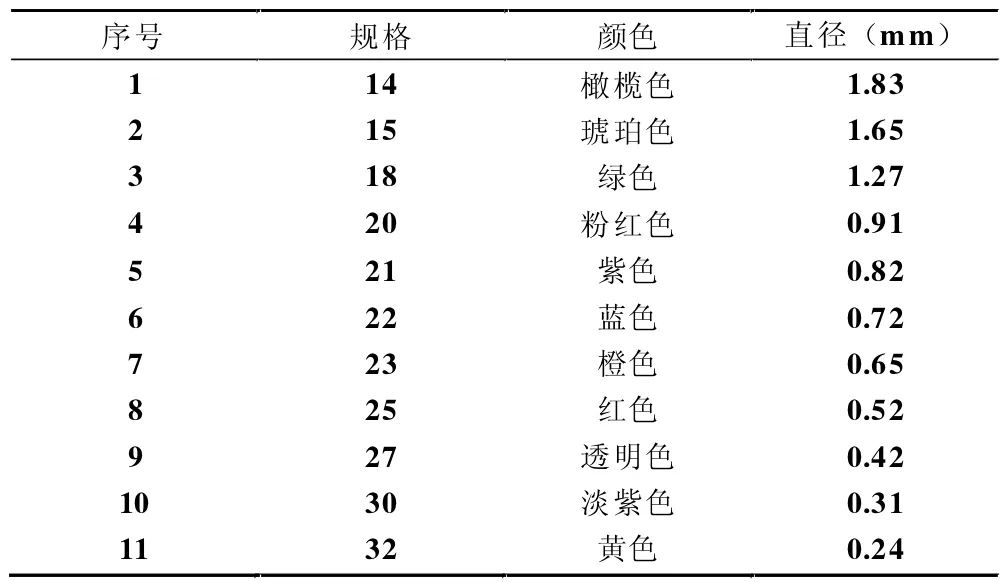

底部填充需采用合适的点胶针头进行点胶,常用的点胶针头规格信息如表1 所示,共11 种规格点胶针头,直径范围覆盖0.24 mm 到1.83 mm。通过对不同的点胶针头进行试验研究,结果表明点胶针头直径过大则会造成点胶量过多,使得填充胶漫流,对芯片周边造成污染,如果点胶针头直径过小则会造成点胶量过少,降低点胶效率。为保证填充胶的填胶高度,可以选择大小合适的点胶针头。

表1 常用点胶针头

从填胶高度上说,针头应尽量接近芯片边缘,同时需让针头正好略低于芯片的下表面,沿芯片边缘所填充的填充剂便会快速均匀地流入底面。填充胶的高度应高于芯片1/2 厚度,以确保填充足够的填充剂。

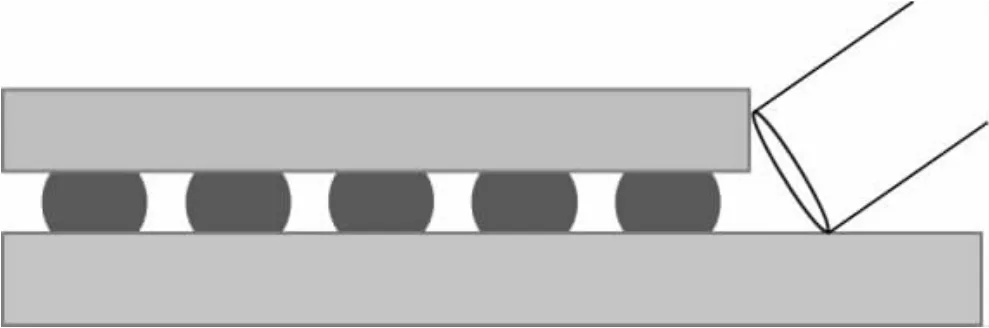

焊球高度约为200 μm,芯片厚度为0.2 mm。选择30 G 淡紫色直径为0.31 mm 的点胶针头,点胶针头的直径略大于焊球高度与芯片1/2 厚度,此时可以使填胶的胶粘高度与芯片高度匹配。点胶针头接近芯片的边缘且高度合适,沿芯片边缘所填充的填充剂便会快速均匀地流入芯片底面。底部填充点胶示意如图1 所示。

图1 底部填充点胶示意

1.2 倒装芯片清洗条件研究

通过丝网印刷工艺在综合电路板焊盘涂上焊膏,将硅基芯片倒装贴合在综合电路板焊盘相应位置,通过低温钎焊系统加热后,将硅基芯片倒装焊接在综合电路板上。焊膏中含有助焊剂,助焊剂残留会增加底部填充空洞,影响底部填充胶固化程度,降低硅基芯片粘接强度,因此在底部填充前,需要将残留的助焊剂清洗干净。

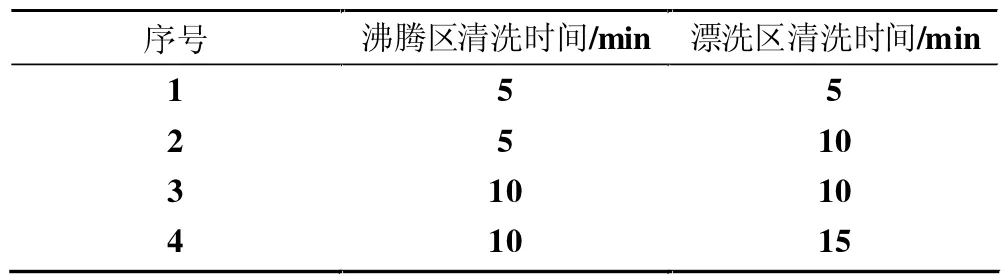

采用汽相清洗工艺对综合电路板进行清洗,过程分为两个阶段:(1) 沸腾区蒸汽清洗;(2) 漂洗区清洗液漂洗。工艺参数如表2 所示。

表2 汽相清洗工艺参数

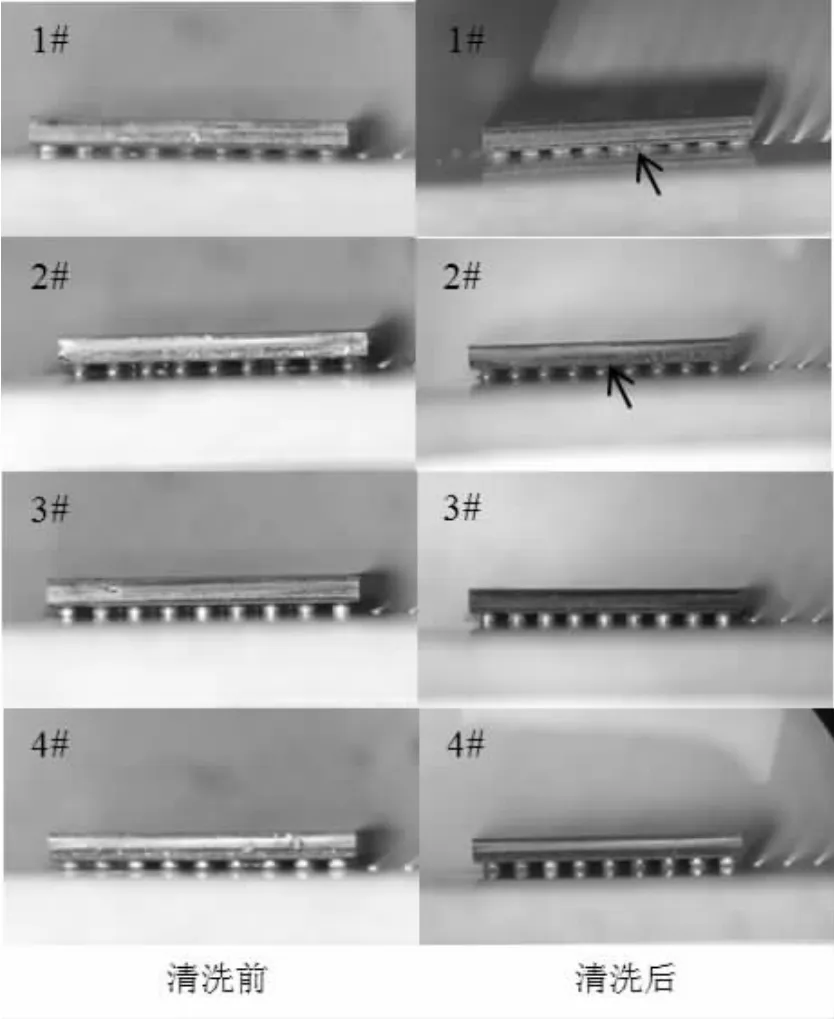

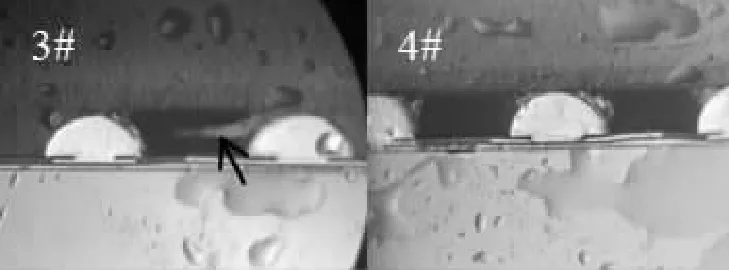

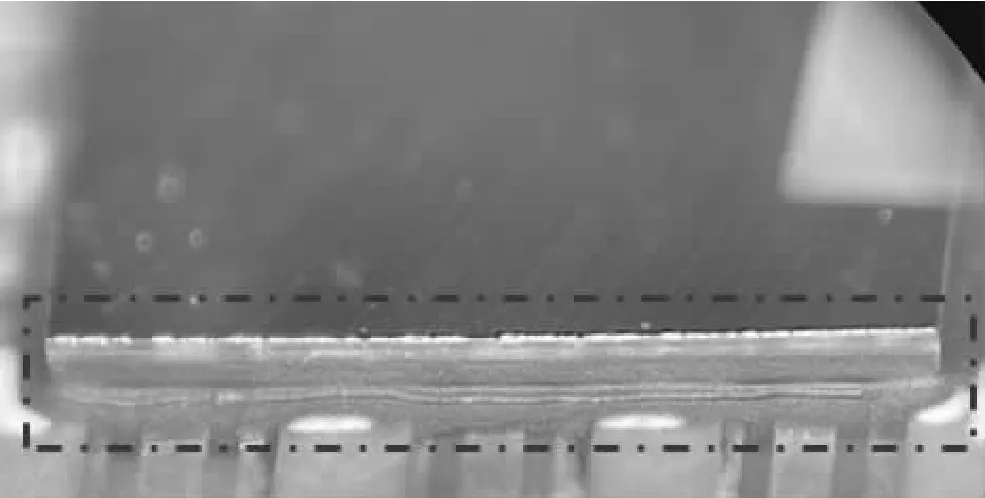

由硅基芯片侧面观察其与电路板间隙边缘,如图2 所示,可以发现除1#、2#样品外,3#、4#样品均未观察到间隙有助焊剂残留。将3#、4#芯片由中间截断,观察芯片中心部位缝隙中的形貌,如图3 所示,可以看出3#芯片存在少量助焊剂,4#芯片未观察到有助焊剂残留。从上述实验结果可知,利用汽相清洗可将助焊剂清洗干净。

图2 清洗前后芯片侧面照片

图3 清洗后芯片中心位置照片

1.3 底部填充胶分配模式研究

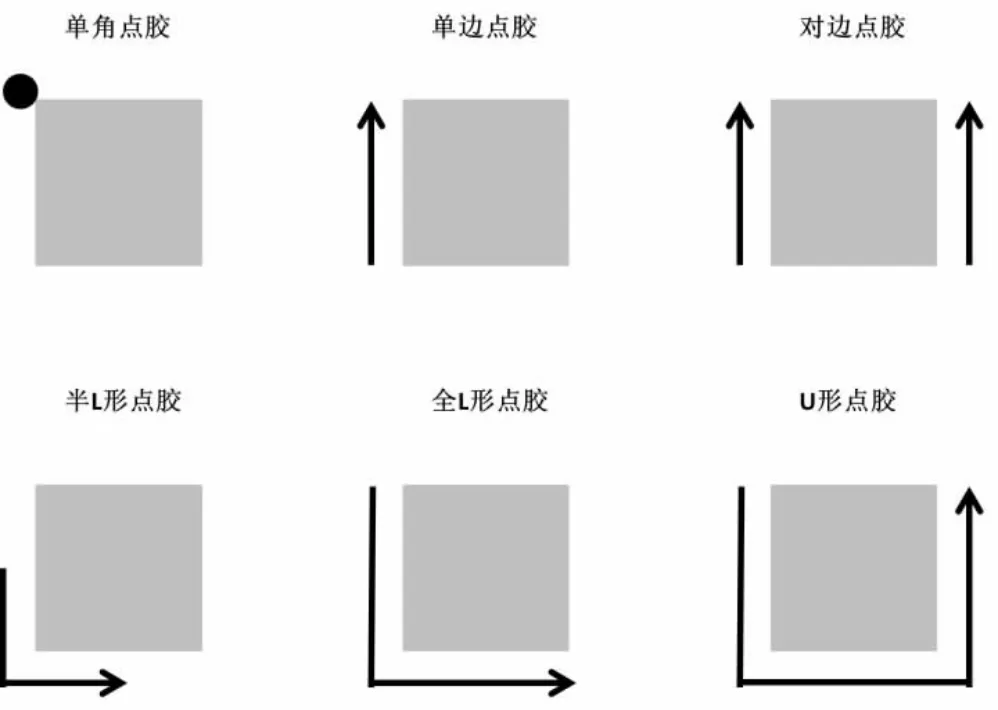

底部填充胶具有多种分配模式,研究不同的分配模式对底部填充速度和填充质量的影响,最终选择填充迅速,但又不把空气包裹在里面形成空洞的分配模式。底部填充胶分配模式示意如图4 所示。

图4 底部填充胶分配模式示意

从图5 可知,在不同的底部填充胶分配模式中,U形点胶显示空洞率最高,半L 形点胶显示空洞率最小。当底部填充胶点胶后,填充胶呈两维方向流动,边缘的底部填充胶流动速度比中间的底部填充胶快,U形点胶虽然底部填充胶流动速度快,但是容易包裹空气形成空洞,如图5 所示。根据切片照片结果,选择半L 型点胶分配模式。

图5 不同底部填充胶分配模式的切片照片

2 性能表征与测试

2.1 外观质量检测

对芯片边缘的底部填充胶进行外观检测,底部填充胶呈黑灰色,表面光亮,无开裂、无空洞,从边缘看底部填充胶完全覆盖住芯片下方焊球,如图6 所示。

图6 芯片边缘填充胶

2.2 空洞率检测

对完成底部填充的芯片进行切片分析,结合光学显微镜检查底部填充胶层质量情况,切片照片如图7所示。从照片可知,底部填充胶层无明显裂纹或分层,存在部分空洞,底部填充区总空洞率小于10%,单个空洞率小于2%,空洞率合格。

2.3 电性能测试

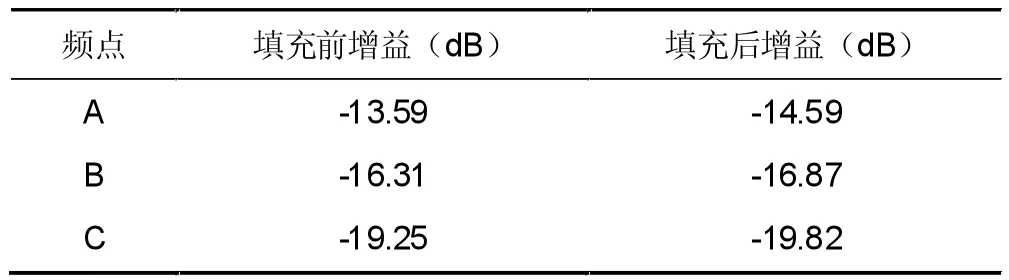

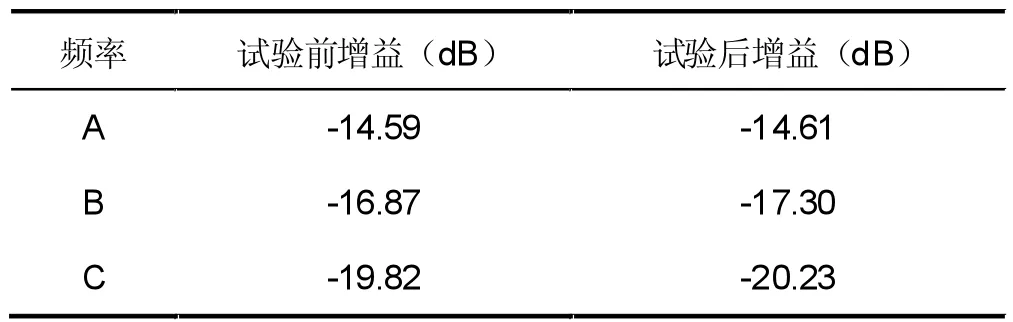

对接收子阵倒装焊芯片填充前和填充后的三个不同频率(A、B、C)增益进行了测试,测试结果如表3所示。从测试结果可知,对接收子阵倒装焊芯片进行底部填充后,增益减小≤1 dB,满足接收子阵性能指标。

表3 增益测试结果

对底部填充后的接收子阵进行温度冲击、温度循环试验。

温度冲击试验条件如下:温度范围为-40 ℃~+70 ℃,-40 ℃保持30 min,+70℃保持30 min,温度冲击10 次,转换时间<3 min。

温度循环试验条件如下:温度范围为-40 ℃~65 ℃,温度变化速率为10 ℃/min,极限温度保持30 min,循环5 次。

对完成温度冲击、温度循环试验后的接收子阵进行增益测试,测试结果如表4 所示。从测试结果可知,在经过温度冲击、温度循环试验后,接收子阵增益减小≤0.5 dB,满足接收子阵性能指标要求。

表4 增益测试结果

结束语

从底部填充点胶针头选型、助焊剂清洗、底部填充胶分配模式方面研究了倒装焊芯片底部填充工艺技术,并成功应用至型号相控阵天线的研制生产中。对倒装焊芯片底部填充外观、芯片底部填充空洞率以及接收子阵电性能进行了测试,结果表明底部填充后的倒装焊芯片满足相控阵天线接收子阵性能指标要求,提高了倒装焊芯片的可靠性。此项工艺技术可以广泛应用于其它型号倒装焊芯片的研制生产过程,为其它型号倒装焊芯片底部填充工艺的研制提供强有力的技术支撑和保障。