基于FSMC接口的点火控制装置设计

2024-03-05赵怡

赵 怡

(山西工程科技职业大学,山西 晋中 030600)

1 FSMC简介

FSMC是英文Flexible Static Memory Controller的首字母缩写,即可变的静态存储控制器。这个接口既可以当作GPIO使用,也可以连接诸如SRAM、ROM以及PSRAM等类型的外部存储设备,并按照存储设备自身的控制时序进行适应性设置,灵活可变。FSMC接口能实现类似于8080总线的控制功能,本文对接口SRM模式应用进行了研究,定义数据、地址和控制总线,在装置内作为一个系统总线使用。

1.1 FSMC内部结构

引脚数在100脚以上的STM32芯片都带有FSMC接口,从芯片外部看,它是ARM处理器按照总线格式组合而成的一个IO引脚集合,图1所示为STM32F103ZGT6的FSMC接口框图,有三组专用控制器信号线和一组通用控制信号线。三组专用控制器信号线分别是NOR/PSRAM控制器信号线、NAND控制器信号线和PC控制器信号线,通用控制信号线是共享于其他控制器的信号线,包括有数据线、地址线和控制线[1-2]。

FSMC从内部结构上看,包含AHB总线、配置寄存器、NOR/PSRAM控制器、NAND/PC控制器、时钟及中断控制线。

1.2 FSMC地址空间

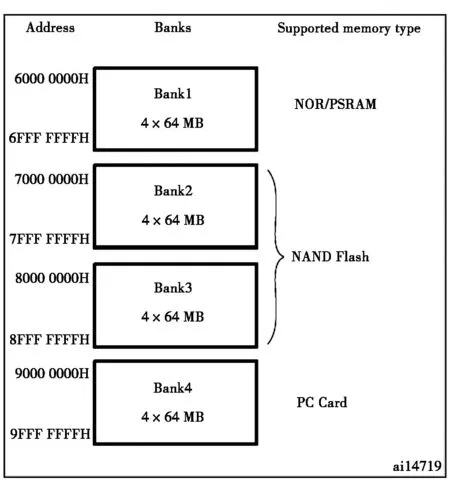

ARM处理器将FSMC接口资源按照外部存储设备进行分类管理,共分成4个BANK,如图2所示,BANK1是SRAM/ROM存储空间,大小为256MB,地址从60000000H到6FFFFFFFH;BANK2和BANK3是NAND Flash存储空间,大小为512MB,地址从70000000H到8FFFFFFFH;BANK4是PC CARD存储空间,大小为256MB,地址从90000000H到9FFFFFFFH。

图2 FSMC映射地址空间管理

本文设计选择SRAM模型,在该模型下,总线地址空间为60000000H~6FFFFFFFH。

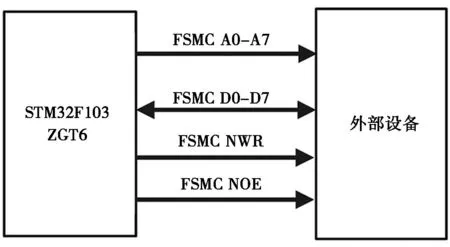

1.3 FSMC接口SRAM模型的应用

FSMC通过设置ARM寄存器选择应用模型,此时,ARM上的IO引脚开始充当总线对外部设备进行读写操作,如图3所示。

图3 FSMC对外部设备进行读写操作

2 点火控制装置硬件设计

点火控制装置用于某型发动机点火控制,主要完成发动机点火、点火回路阻值采集和点火电源采集,装置由主控板、电源板和点火控制板组成。

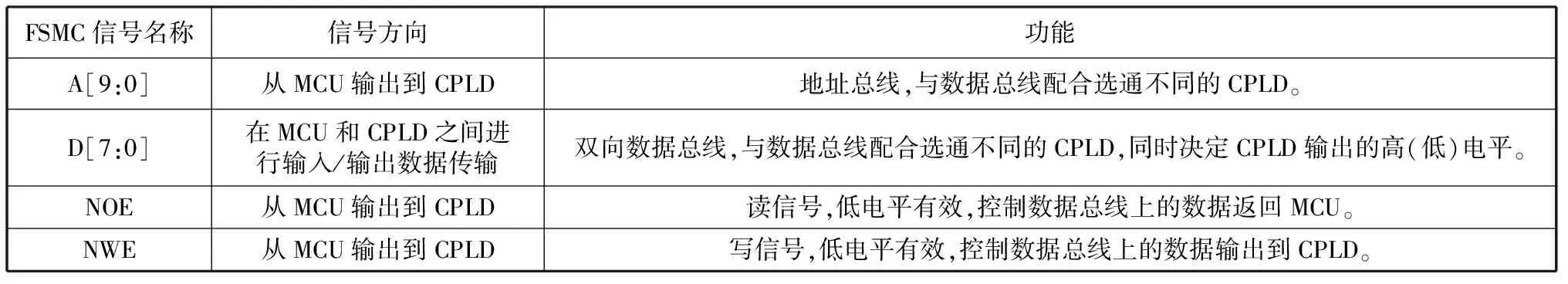

点火控制装置I/O扩展主要由FSMC和CPLD实现,使用的FSMC资源是BANK1的SRAM/ROM存储空间,地址线60000000H到600001FFH,FSMC数据线、地址线和控制线说明见表1。

表1 FSMC资源及功能

2.1 继电器控制

继电器控制信号是CPLD对FSMC地址线和数据线译码产生的,FSMC地址决定了被控的继电器是哪一个,FSMC数据决定继电器的状态是断开还是接通。

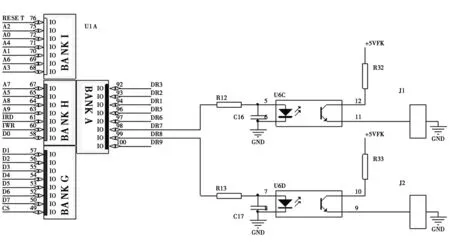

如图4所示,继电器J1对应FSMC地址为0X10,继电器J2对应FSMC地址为0X20,FSMC数据0XFF对应CPLD引脚输出高电平,数据0X00对应CPLD引脚输出低电平。

图4 继电器控制原理图

则当主控程序执行outputb(0X10,0XFF)时,CPLD第98引脚输出高电平,DR7=1,继电器J1将接通,而当主控程序执行outputb(0X10,0X00)时,CPLD第98引脚输出低电平,DR7=0,继电器J1将断开。同理,当主控程序执行outputb(0X20,0XFF)时,继电器J2将接通,而当主控程序执行outputb(0X20,0X00)时,继电器J2将断开[2]。

2.2 回路阻值采集

回路阻值检测电流是恒定的10 mA电流,根据欧姆定律,AD将采到的电压除以10 mA电流就可以得到阻值。阻值信号通过AD的并口送到CPLD,CPLD再将数据送到FSMC数据总线。具体过程如下。点火控制板上电后对AD转换芯片AD7609进行初始化:

复位端信号置0持续10ms后再置1完成芯片复位,然后片选置1,CONV引脚置1启动转换。上述过程也是通过FSMC总线实现。

当AD芯片完成数据转换后,通过一个电平变化给出完成信号,通知主控板此时可以接收数据,主控程序通过这一信号运行中断程序,执行inputb(0X43),将数据从CPLD输入FSMC接口,0X43是CPLD并行数据线的地址。

3 FSMC初始化设置

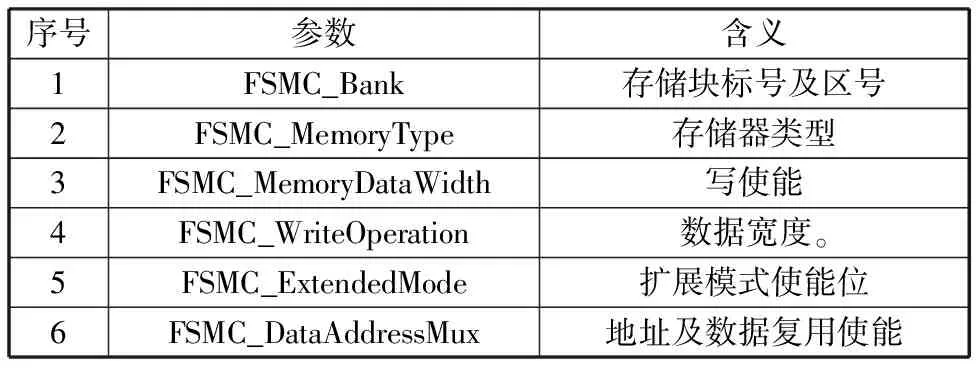

STM32F103固件库提供了标准的FSMC初始化函数,对于SRAM时序模型,只使用FSMC_NORSRAMInit()初始化函数,表2列出了FSMC控制总线参数。

表2 FSMC参数及含义

FSMC初始化函数具体如下:

void FSMC_SRAM_Init(void)

{

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC,ENABLE); //使能外设时钟

readWriteTiming.FSMC_AddressSetupTime = 0x01; //地址建立时间

readWriteTiming.FSMC_DataSetupTime = 0x0A; //数据建立时间

readWriteTiming.FSMC_BusTurnAroundDuration = 0x00; //总线转换周期

readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_A; //总线类型

FSMC_NORSRAMInitStructure.FSMC_Bank=FSMC_Bank1_NORSRAM1; //存储区映射区域

FSMC_NORSRAMInitStructure.FSMC_MemoryType =FSMC_MemoryType_SRAM; // 存储器类型

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_8b; // 存储器数据宽度

}

初始化中的地址建立时间数据建立时间是根据FSMC总线上的设备时序特征确定的,具体到本设计中,即考虑如何设置FSMC读周期时序中地址建立时间和数据建立时间参数,使得其满足AD转换芯片AD7609BSTZ的读周期时序。

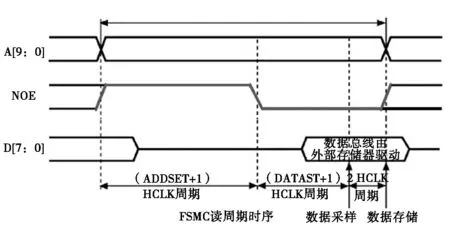

如图5所示为FSMC读周期时序,NOE是读信号,其高电平时长为ADDSET+1个HCLK周期(每个HCLK周期27ns左右),低电平时长为DATAST+3个HCLK周期,其中的2个HCLK周期是采集后的数据存储时间。

图5 FSMC时序建立原理图

通过比较,ADDSET的值设置为2个HCLK周期(约54ns),可满足AD7609BSTZ读信号高电平时长大于15ns的要求,所以在初始化中设置AddressSetupTime = 0x01。同理,FSMC低电平时长不能小于AD7609BSTZ的19ns的要求,为了保证采集数据可靠性,低电平持续时间设置较长,为13个HCLK周期(约351ns),即DataSetupTime = 0x0A,足以保证AD7609BSTZ的数据从总线上返回[4-5]。

4 测试结果

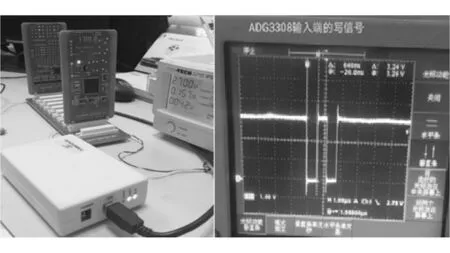

图6如示为点火控制板基于FSMC接口的控制信号波形,主控板通过FSMC接口输出数据和读写控制信号,用示波器测试从电平转换电路ADG3308输入端测得,两个连续的写控制信号(NWR)从高电平变为低电平,幅度3.2 V,宽度640 ns。FSMC数据总线和地址总线经CPLD译码后能正确控制AD芯片及继电器,测得点火回路阻值为6.5 Ω,输出点火电流1.5 A。

图6 点火控制装置FSMC总线测试

5 总结

本文基于ARM处理器的FSMC接口设计了一种点火控制装置,实现了继电器控制和点火回路阻值采集。主控程序执行上位机指令,采用轮询机制完成各个通道的阻值等集,在满足点火条件下输出点火电流,FSMC接口开发不需要操作系统支持,运行速度快,便于小型化设计,是一种高效的嵌入式控制解决方案。