X频段八波束接收组件的设计与实现

2024-02-29李佳津王鹏毅

李佳津,王鹏毅,王 新

(中国电子科技集团公司 第54研究所,石家庄 050081)

0 引言

近年来,低轨卫星数量逐渐增多且有向大规模星座发展的趋势,负责卫星测控设备需求量越来越大。多波束有源相控阵系统可对多个目标同时进行跟踪并接收信号,具备一站多星管理能力,可以很好地解决星座发展地面管理方面的瓶颈。接收组件作为有源相控阵系统的关键组成部分之一,具有对各个通道进行信号放大,相位调节以及波束合成等功能,其体积、重量、成本以及功耗等指标直接决定整个相控阵系统的性能[1]。在多波束有源相控阵系统中,每一个天线单元中均需要射频接收组件,在有限空间内同时形成多个波束,组件内部合路网络复杂,含有众多分立器件实现高集成难度大、成本高;此外组件内部信号的传输效率对整个相控阵系统有很大的影响。因此研究和设计集成度更高、体积更小、性能更优的接收组件具有重要意义。

随着高密度微组装工艺的发展,电路布局形式由传统的二维平面布局向三维立体高密度布局发展,接收组件形式也逐渐由体积较大、集成度较低的砖块式向体积较小、集成度较高的瓦片式组件发展。目前高密度微组装技术主要有微波多层印制电路(PCB)技术、低温共烧陶瓷(LTCC)技术、高温共烧陶瓷(HTCC)技术共3种。其中LTCC技术是以低温烧结的陶瓷材料为基板进行三维叠构,这种材料高频传输性能好且烧结厚度小,用于组件设计中可以提升其集成度[2-4],但由于陶瓷基板材料机械强度差以及散热能力差,采用这种基板进行设计时其叠层数量受到限制,不适用于较多层数的组件设计;HTCC则是高温烧结的陶瓷材料,相较于LTCC,这种材料具有较高的热导率,散热性能更好,且同样具有多层布线能力[5-7],但同时这种材料导电性能较差,金属经过高温烧结后会使得导电性能下降;最后一种则是多层印制板(PCB)技术,这种技术以印制板为基板进行三维的叠构,具有低损耗、优良的高频特性以及低膨胀系数等优点[8-10],相较于LTCC和HTCC材料加工难度较小且成本较低,因此基于多层印制板技术对组件进行设计可以满足其高集成度与低成本需求。

在组件设计中,波束合路网络作为接收组件的关键组成部分,将各个天线单元对应通道的输出信号分别进行合成,最终形成多个波束,当组件工作在高频段时,天线布阵间距小,在有限空间内实现多套合路网络存在较大难度。此外,合路网络的通道间隔离度以及相位一致性、插入损耗等指标对接收组件的整体性能有较大的影响,因此高效率的小型化合路网络也是组件设计中的一个难点。合路网络由若干个功分器级联而成,常用的功分器主要有T型功分器、Wilkinson功分器以及Gysel功分器等,T型功分器是最早应用的功分器形式,其结构简单,设计难度小,但其输出端口间隔离度较小不能够满足组件设计要求。Wilkinson功分器[11]相对于传统T型功分器,在两个输出端口间存在隔离电阻从而保证了输出端口间的隔离度且结构相对简单,能够保持端口间良好的隔离度[12-14],而Gysel功分器相对于Wilkinson功分器结构较为复杂,体积更大,且传输损耗较大[15],不适用于小型化应用。因此,基于Wilkinson功分器对合路网络进行设计可以满足其小型化以及高效传输信号等需求。

使用多层印制板技术可以实现组件的三维分层布局,有效地减小其尺寸提高组件整体的集成度,但在多层印制板上实现层间低损耗垂直互联也是一个需要解决的大问题。目前多层板间的垂直互联结构主要有以下几种:第一种则是耦合形式的垂直互联结构,通过电磁耦合来进行层间的信号传输[16-17],这种基于耦合形式的垂直互联结构在高频段使用受限,且回波损耗较大,在工作带宽内回波损耗大,且在信号传输过程中易受到其他无源结构影响,致使传输效果不理想。第二种则是通过圆柱形的同轴孔来进行不同层之间的信号传输[18-21],这种垂直互联结构应用较广,传输损耗小于耦合形式的垂直互联结构,且实际加工中也常采用这种结构作为多层板不同层间的信号传输结构,但在高频段同轴孔与传输线之间存在不连续性且同轴孔会存在较为严重的寄生参数,因此需要对其进行精确的建模分析,来降低结构的传输损耗。

本文以X频段八波束接收组件为研究对象,基于多层印制板技术实现了有源器件以及多套波束合路网络的高密度布局,提升了组件的集成度,基于Wilkinson功分器形式设计了高效小型化的合路网络,并对组件内部的垂直互联结构进行了建模分析,通过优化结构参数的方法降低组件内部信号传输损耗。在此基础上对组件进行了加工测试,结果表明,在7.5~9 GHz频率范围内组件增益大于18 dB,输出驻波比小于1.5,通道间相位一致性小于±5°,满足多波束有源相控阵系统的工作需求。

1 接收组件方案设计

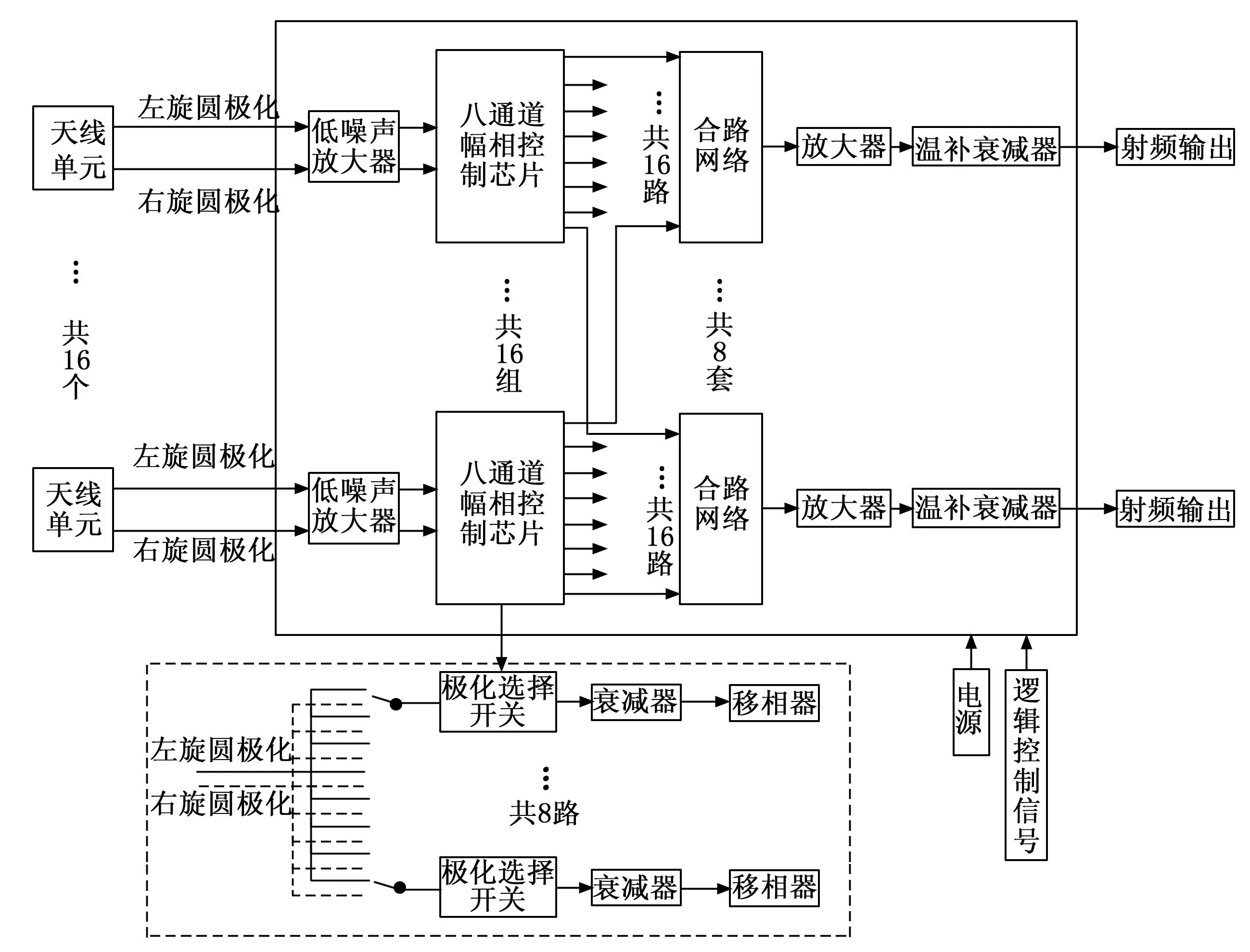

X频段八波束接收组件组成原理如图1所示,组件主要由低噪声放大器、八通道幅相控制芯片、八波束合路网络及放大器等构成。组件对来自16个双圆极化天线单元的双圆极化接收信号首先进行低噪声放大,放大后的信号再分别送入16个八通道幅相控制芯片,每个八通道幅相控制芯片集成了两套一分八功率分配网络以及8个极化选择开关、8个衰减器和移相器。左旋圆极化与右旋圆极化信号进入八通道幅相控制芯片后,分别进入两套一分八功率分配网络,分配网络输出的信号再经过极化选择开关,以实现对任意极化信号的选择,8个极化选择开关的信号再分别经过衰减器与移相器对信号进行幅度与相位控制,然后由八道幅相控制芯片8个输出端口输出,再分别进入8套波束合成网络完成八波束信号的合成,合成后的信号再经过放大送入下一级电路,考虑到组件工作时温度变化对放大器的影响,组件又在放大器后增加了一级温补衰减器,为其提供一定增益补偿。此外,组件的电源控制单元通过电平转换、稳压的方式,给组件的有源器件提供稳定的电平;逻辑控制单元通过输入不同的控制信号,控制组件中的有源芯片工作在固定的工作模式。

图1 八波束接收组件原理图

X频段八波束接收组件设计工作频率为7.5~9 GHz,设计要求通道增益大于17 dB,噪声系数小于1.8 dB,通道间增益小于±5°,输出驻波比小于1.5,组件链路指标分配如图2所示。

图2 接收组件链路指标分配

根据噪声系数[4]计算公式:

(1)

通过式(11)可计算出接收链路噪声系数为1.7 dB,增益为17.8 dB,满足系统指标设计要求。

2 组件设计与实现

2.1 高密度叠层设计

为提升X频段八波束接收组件集成度,降低组件剖面,组件基于多层印制板技术进行设计,纵向实现低噪声放大器、八通道幅相控制芯片、放大器等有源器件以及8套路波束合成网络的高密度布局,并通过控制不同层间所用印制板的板材厚度来降低组件剖面,进一步降低组件的尺寸。

组件三维叠层结构如图3所示,组件的叠层结构共44层,不同层间通过垂直互联结构进行信号的传输,印制板采用TSM-DS3板材(介电常数Dk=3,损耗角Df=0.001 1),SIG1层为组件顶层,用于放置16组低噪声放大器与八通道幅相控制芯片,所用板材厚度为0.13 mm。SIG2、SIG3、SIG12-17层为芯片电源以及逻辑控制电路走线层,其主要为SIG1层的有源芯片提供工作所需电平以及控制信号,所用板材厚度均为0.13 mm。

图3 八波束接收组件叠层结构

SIG4-SIG11为八波束合成网络层,通过分层设计将8套合路网络分别放置于8层印制板上,且每层走线形式均采用带状线形式,使得每个合路网络上下均有两个地层,保证了不同合路网络之间不会存在串扰,且分层布局可以使得8个波束网络可以采用相同的布局结构,降低了多套合路网络设计的复杂度,每个合成网络的输入信号由SIG1层八通道幅相控制芯片输出后经垂直互联结构分别输入至8套合路网络进行波束合成,合路输出信号再经垂直互联结构输出至组件底层SIG18,合路网络层所用印制板的厚度均为0.25 mm。

底层SIG18层放置有低噪声放大器以及电源、逻辑信号控制单元,低噪声放大器对于来自合路网络的信号进行放大,电源以及逻辑信号控制单元为组件的有源芯片提供工作所需的电源以及控制信号。

2.2 合路网络设计

基于多层印制板技术的八波束接收组件的8套合路网络分别位于组件的不同层,每套和路网络结构基本一致,且所有合路网络的电磁环境基本相同,在实际仿真过程中可以只对一层合路网络进行仿真,然后添加垂直互联结构,建立完整模型对印制板整体进行仿真验证。本组件中的合路网络针对来自16个天线单元的射频信号进行合路并输出,其整体结构为由多个一分二功分器经过四级级联而成十六合一的合路器。基于组件的小型化设计以及高隔离度、低传输损耗等指标需求,合路网络基于尺寸更小、结构简单、端口间隔离度更好的Wilkinson功分器形式进行设计。

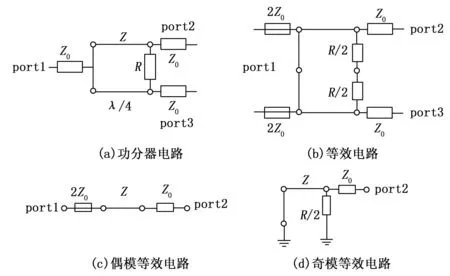

一分二Wilkinson功分器电路结构如图4(a)所示,其主要由四分之一波长传输线以及一个隔离电阻构成。通过奇偶模理论对其进行分析,如图4(b)所示将功分器port1端口的源阻抗Z0等效于两个阻值为2Z0的阻抗并联得到,当port2与port3端口施加偶模激励时,在两个端口施加大小相同方向相同的电压,此时电阻R两端电压相同,电阻R相当于断路,则功分器的偶模电路如图4(c)所示,此时偶模电路等效于一个源端阻抗为2Z0负载阻抗为Z0的单节传输线匹配电路,传输线长度为四分之一波长,当功分器正常工作时port2端口与源端口port1阻抗匹配,根据四分之一波长传输线的阻抗特性[14]可知传输线阻抗:

(2)

图4 Wilkinson功分器

同理,对功分器施加奇模激励,等效于port2与port3两个端口被施加方向相反,大小相同的两个电压,如图4(d)所示,此时电流由port2端口流向port3端口,电阻R可等效为两个R/2的电阻串联,两个电阻之间等效于接地。此时源端阻抗2Z0被短路,经过四分之一波长传输线后相当于开路,因此电流只流过隔离电阻R,当port2端口处阻抗匹配时,由图4(c)可得:

(3)

根据此式便可得到Wilkinson功分器中隔离电阻R的阻值。经过上述推导即可得到一分二Wilkinson功分器的所有电参数。

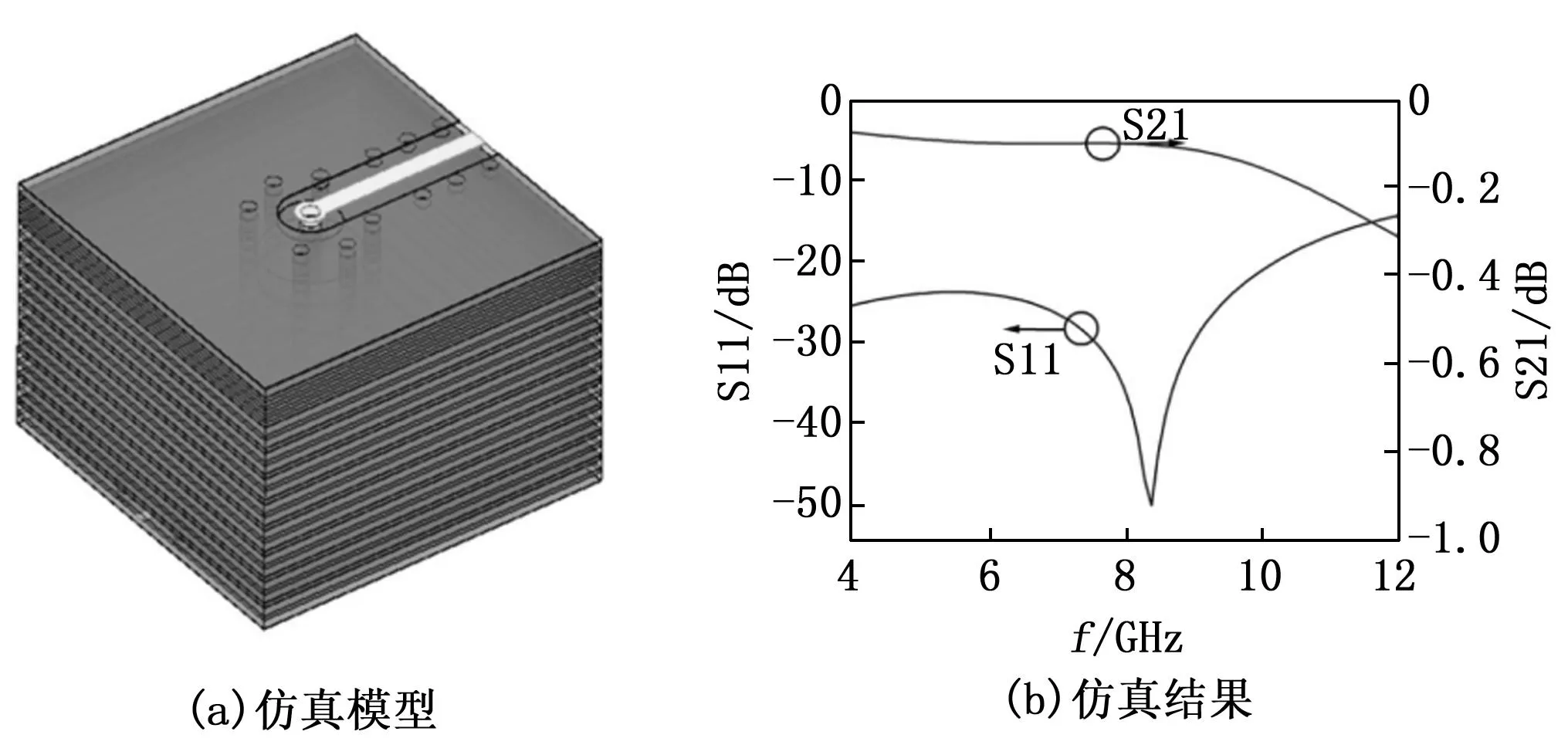

根据上述分析步骤可以得出,通过奇偶模分析的方法可以把Wilkinson功分器的设计问题转化为求解阻抗匹配的问题。因此基于上述分析方法,设计了一款工作中心频点为8.3 GHz的带状线一分二功分器,其端口阻抗均为50 Ohm,根据式(2)计算可得四分之一波长传输线阻抗为70.7 Ohm,根据式(3)计算可得隔离电阻阻值为100 Ohm,带状线功分器基于TSM-DS3 印制板材进行设计,板材厚度为0.25 mm。对其进行仿真设计,其设计结果如图5所示。

图5 带状线一分二功分器

观察仿真结果,所设计的一分二功分器在7.5~9 GHz内回波损耗以及端口间隔离度均小于-20 dB,插入损耗小于0.2 dB左右,满足组件设计要求。

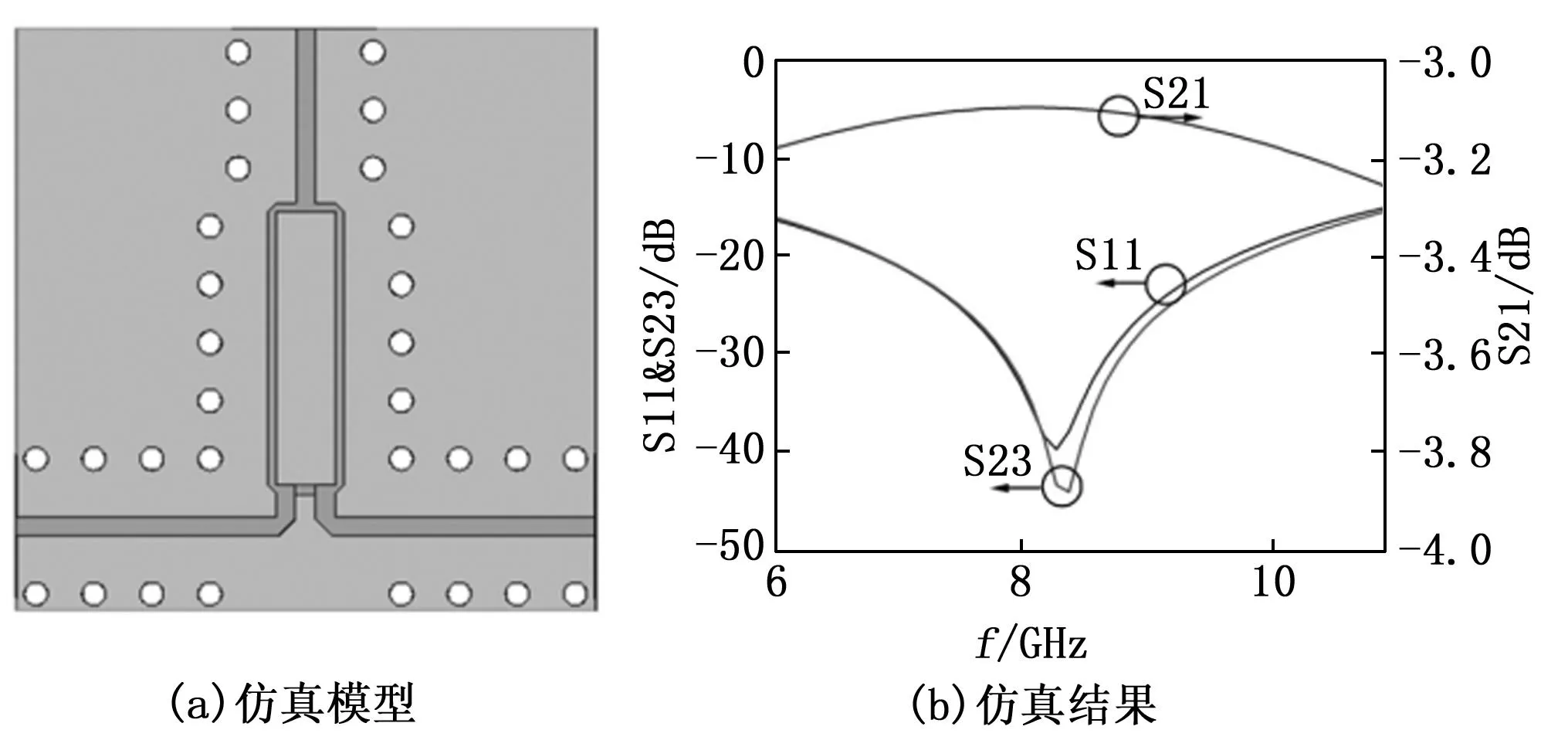

本文所设计的合路网络需要对16个输入端口的信号进行合成,因此在上述一分二功分器基础上需对其进行级联组成十六合一的合路网络,级联时需要保证合路网络结构的对称性来保证各个输入端口的幅度相位一致性,但同时合路网络各个输入端口位置由组件表面贴装的有源器件位置确定,因此合路网络的设计也需要综合考虑组件表面有源器件布局。以单个合路网络为例,其设计如图6所示,组件顶层的16个八通道幅相控制芯片输出的信号通过垂直互联结构分别进入8套合路网络,单个合路网络的布局整体上保持了对称结构,在输入端口处受限于器件布局,其结构并不能做到完全对称,为了保证各个输入端口处的相位一致性需要对输入端口处的不对称结构进行仿真优化,其优化结果如图6所示,根据图6(c),两条不对称传输路径的相位之差在7.5~9 GHz范围内保持在0.6°以下,幅度之差保持在0.005 dB以内,幅度相位一致性良好。

图6 合路网络

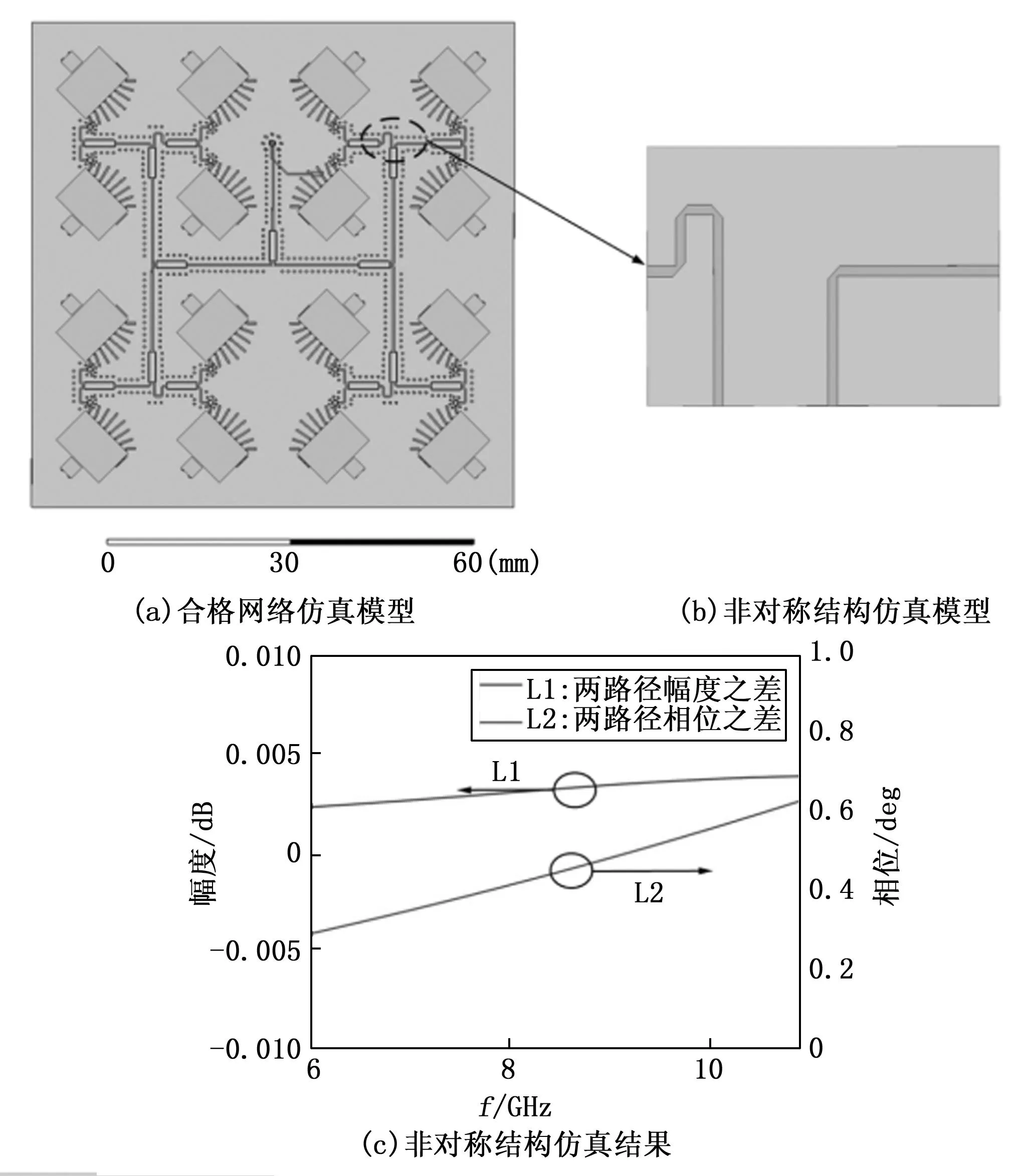

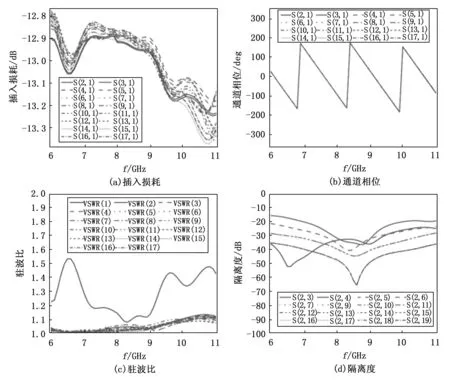

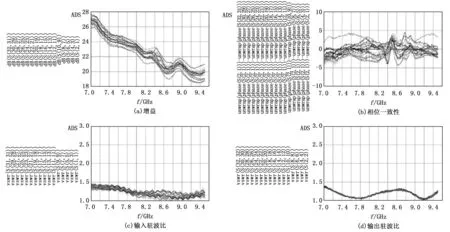

接下来对合路网络进行仿真,其结果如图7所示,根据7(a),在7.5~9 GHz范围内合路网络各通道的插入损耗小于13 dB,其各通道间幅度之差保持在0.2 dB以内,幅度一致性良好;根据图7(b)其各通道相位曲线几乎重合,相位一致性良好;根据图7(c),在7.5~9 GHz,各个端口驻波比小于1.2,传输性能良好;根据图7(d),不同通道间隔离度均保持在-20 dB以下,通道间隔离度良好,满足设计要求。

图7 十六合一合路网络仿真结果

2.3 低损耗垂直互联结构设计

在多层印制板电路中,由于电路分布在不同层,因此需要一种垂直互联结构将不同层间的电路相连接起来,以实现层间的信号传输,垂直互联结构在层间进行信号传输时会存在阻抗不连续以及寄生参数的问题,导致信号传输损耗增加,因此实现层间信号的低损耗传输是垂直互联结构设计中需要解决的问题。基于此需要对垂直互联结构建立精确的模型进行分析,从而对其进行有效地优化设计,实现层间信号的低损传输。

首先确定组件表层以及内层的传输线形式:微带线和共面波导常用于印制板表层信号传输,共面波导结构如图8(a)所示,其相对于微带线,其两侧存在两条地平面,这种包含在导体和地之间的电场结构,减小了邻近传输线之间的电场耦合,使得邻近传输线之间达到良好的隔离,此外这种特殊结构的导体与地的空间占用率很小,更适合应用于多层印制板电路中表层布线,由于其拥有相较于微带线更好的信号隔离效果,所以在本组件设计中,表面传输线形式采用共面波导形式。多层印制板的内部传输线形式则多采用带状线,如图8(b)所示带状线埋置于两层介质板之间,上下两侧均是地平面,能够很好地将该层信号与其他层间隔离开来,因此本组件内部走线形式采用带状线,并在此基础上在带状线两侧加入接地通孔,可以防止同层内带状线之间的信号串扰,以实现良好的层内信号隔离。

图8 垂直互联结构示意图

本组件中用于层间信号传输的垂直互联结构基于同轴孔的形式进行设计,因此,本文的垂直互联结构形式为共面波导-同轴孔-带状线。其等效模型如图8(c)所示,其主要由3部分构成,分别是同轴孔、与层间传输线连接的焊盘结构,以及将过孔与地层或者电源层隔离开的反焊盘结构,在此基础上在过孔的周围加上一圈接地通孔,可以有效减少过孔信号传输的辐射损耗,提供信号回流路径,改善过孔传输信号的质量。

基于同轴孔的垂直互联结构在信号传输中存在两个问题:

1)同轴孔在传输线上会表现为阻抗不连续的断点,会使得传输的信号发生反射,增大信号的传输损耗;

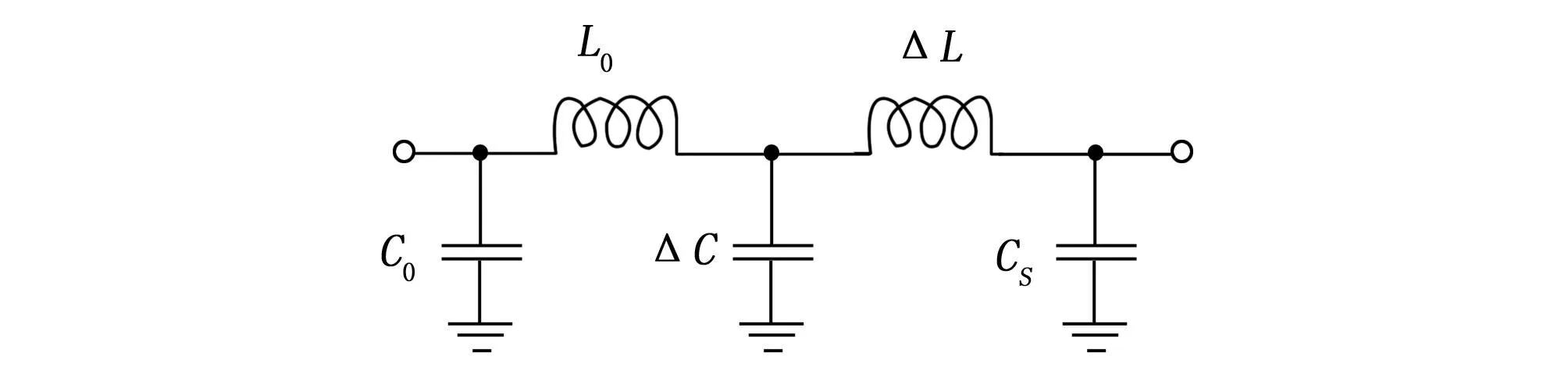

2)在高频段,同轴孔会与周围地层之间存在严重的寄生参数效应,这些寄生参数会使得过孔的传输性能受到影响。因此同轴孔的设计不合理会使得信号传输损耗增加,从而影响整个组件的工作性能。接下来将对此结构进行建模分析,其等效电路如图9所示。

图9 垂直互联结构等效电路

首先对其传输阻抗的不连续性进行分析,从上层共面波导过渡到下层带状线时,垂直同轴孔可以等效为电感,其电感值根据经验公式[22]可近似为:

(4)

式中,lvia为垂直通孔的长度,v为自由空间的波速,γ=0.577 2为欧拉常数,ω为传输线线宽度,λ0为信号的波长,εr为传输线等效介电常数。这个电感与传输线原有的电感L0串联,导致在传输线与同轴孔在过渡段的总电感增加为:

L=L0+△L

(5)

根据传输线特性阻抗计算公式,过渡段传输线特性阻抗变为:

(6)

而过渡段外传输线线的特性阻抗仍然是:

(7)

其中:C0为传输线原有电容,为了减少反射降低驻波,使得信号优良传输,保证阻抗匹配,需要在过渡端引入补偿电容△C,使得过渡段阻抗变为:

(8)

根据式(9),补偿电容△C经计算可表示为:

(9)

在垂直互联结构中,同轴孔与周围接地孔形成同轴结构,在同轴孔正下端提供了所需补偿电容的焊盘结构,电感计算公式是近似的,因为附加电感的大小会随频率的变化而变化,所以补偿电容的大小也在变化中,因此需要采用电磁场仿真软件HFSS进行分析。

接下来对同轴孔的寄生参数进行分析,首先根据同轴孔结构示意图可知过孔与周围底层之间存在着寄生电容Cs,其可以近似估算为[20]:

(10)

其中:εr为板材的介电常数,t为板材厚度,Rpad为焊盘半径,Rantipad为反焊盘半径。可以看到过孔的寄生电容主要受焊盘半径以及反焊盘半径的影响。

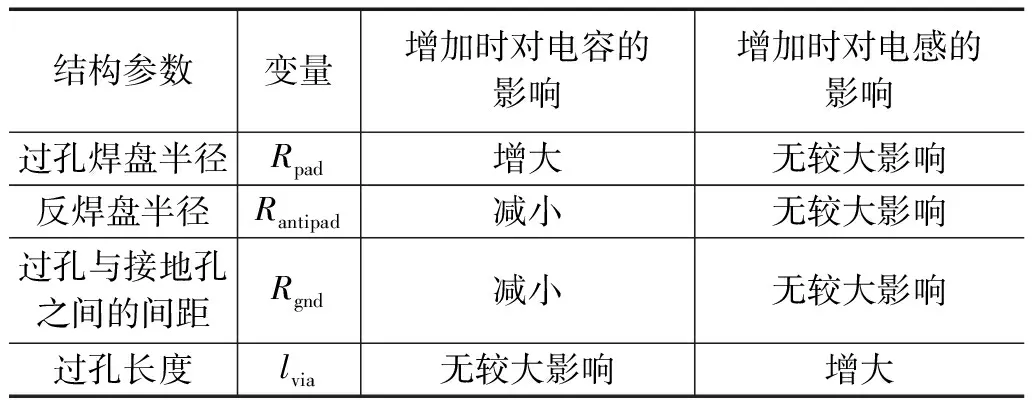

综合式(9)和式(10)可得同轴孔的不同结构参数对于其电参数均有不同的影响,如表1所示。

表1 过孔结构参数对寄生参数的影响

根据表1,在仿真设计中,可以根据过孔信号传输效果,对其结构参数进行优化,从而对同轴孔的电感以及电容参数大小进行平衡,降低信号传输损耗。

综上,针对同轴孔的阻抗不连续性以及寄生参数等问题,均可以采取优化焊盘尺寸等结构参数来减小其影响,由于过孔半径以及长度需根据组件实际尺寸确定不能任意变更,因此主要对焊盘半径、反焊盘半径以及过孔与接地孔间距这3个结构参数来对其进行优化。根据组件叠层结构,以表层(SIG1)八通道幅相控制芯片输出端口到第一层波束合路网络(SIG4)输入端口的垂直互联结构和第一层波束合路网络的输出端口(SIG4)至底层放大器(SIG18)输入端口的垂直互联结构为例进行优化仿真。

首先对表层(SIG1)八通道幅相控制芯片输出端口到第一层波束合路网络(SIG4)输入端口的垂直互联结构进行仿真,根据图3所示的组件叠层结构由SIG1层至SIG4层的同轴孔共需穿越3层印制板、3层半固化片以及两个地层,同轴孔长度为0.906 mm,同轴孔半径定为0.3 mm,周围地孔半径定为0.2 mm,仿真结果如图9所示。根据图9(a),同轴孔与地孔间距在1.4~1.8 mm范围内,当同轴孔与地孔间距增大时,回波损耗曲线的谐振点也随之改变,这是因为随着地孔与同轴孔距离的改变,其间的寄生电容也随之改变,因此导致曲线谐振点发生变化,同时随着同轴孔与地孔间距变大回波损耗也有一定增加,这是由于地孔与同轴孔间距增大的同时导致地孔之间的间距也有一定增大,对同轴孔信号的屏蔽作用有一定减小;观察图9(d)可知随着地孔与同轴孔间距的增大其插入损耗变化并不是很明显,但随着频率的增加,插入损耗明显有增大的趋势,这是因为随着频率的增加过孔的寄生参数影响愈发明显,传输损耗也逐渐变大。在同轴孔与地孔的间距为1.8 mm时,回波损耗的谐振点在中心频点8.3 GHz左右,回波损耗小于-35 dB,且插入损耗小于0.1 dB传输效果更好,因此同轴孔与地孔之间的间距设为1.8 mm。

根据图9(b)和图9(e),可以观察到反焊盘半径在0.6~0.8 mm范围内,随着反焊盘半径的增加回波损耗以及插入损耗逐渐变小,且谐振点发生了变化,这是由于反焊盘的增大使得同轴孔与周围地层之间的寄生电容发生了改变,从而使得回波损耗谐振点发生了改变,且反焊盘过小时会使得上下层之间的信号传输受阻,因此随着反焊盘半径增加传输损耗逐渐变小;但同时在0.8~1mm范围内随着反焊盘半径的增大,传输损耗又逐渐增加,这是由于反焊盘尺寸过大使得表层传输线的信号失去了自身的地,使得传输性能变差。在反焊盘半径为0.8 mm时,在中心频点8.3 GHz处回波损耗最小,小于-35 dB,插入损耗小于0.1 dB,传输损耗最小,因此反焊盘半径设为0.8 mm。

根据图9(c)和图9(f),可以观察到同轴孔焊盘半径在0.3~0.4 mm范围内,随着焊盘半径的增加回波损耗的谐振点发生了改变,且回波损耗有一定程度的减小,且插入损耗也逐渐减小,这是由于随着焊盘的增大,为过渡段传输线提供了补偿电容,一定程度上减小过孔与传输线之间的不连续性,改善了信号的传输效果,但同时在0.4~0.7 mm范围内,随着焊盘半径的增大回波损耗与插入损耗又开始逐渐变大,这是因为焊盘继续增大时,补偿电容超出了所需补偿值,且其与周围地层之间的寄生参数也逐渐变大,从而增加了信号传输的损耗,使得传输效果变差;在焊盘半径为0.4 mm时,在中心频点8.3 GHz处回波损耗最小,小于-35 dB,插入损耗小于0.1 dB,传输损耗最小,因此焊盘半径设为0.4 mm。

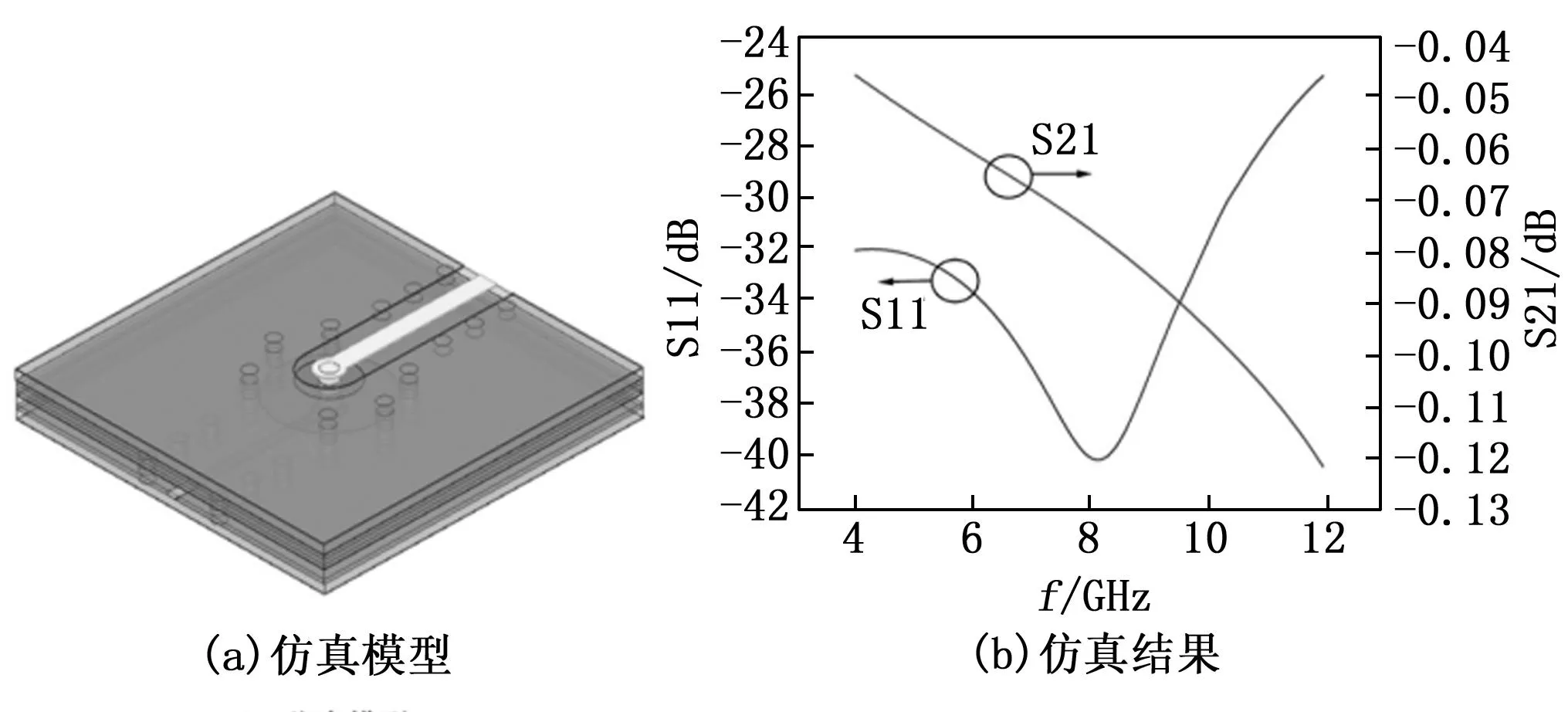

根据上述优化结果,SIG1层至SIG4层的垂直互联结构优化后的设计参数如表2所示,最终优化后的过孔仿真结果如图10所示,根据图10(b)可知过孔在工作频点8.3 GHz处回波损耗小于-40 dB,插入损耗小于0.1 dB,传输性能良好,满足实际工作需求。

表2 SIG1层-SIG4层垂直互联结构参数

图10 SIG1-SIG4垂直互联结构仿真结果

接下来对第一套合路网络输出端口(SIG4)至组件底层放大器输入端口(SIG18)的垂直互联结构进行优化设计,由SIG4层至SIG18层过孔长度为6.718 mm,同轴孔半径为0.3 mm,地孔半径为0.2 mm,对其进行优化,优化后结构参数如表3所示,其优化结果如图11所示。根据图11过孔在工作频点8.3 GHz处回波损耗小于-50 dB,插入损耗小于0.2 dB,在10 GHz频率范围内传输回波损耗小于-20 dB,插入损耗小于-0.2 dB,传输性能良好,满足实际工作需求,但对比于前面所仿真的SIG1层-SIG4层的垂直互联结构其传输性能变差,这是由于随着同轴孔穿层的数量增多,其周围电磁环境愈发复杂,优化结构参数只是相对平衡了垂直互联结构中寄生电容和电感的影响,并不能完全消除,因此在多层板的设计中要尽量合理设计电路的布局,尽量减少较长的垂直互联结构的使用。

表3 SIG4层-SIG18层垂直互联结构参数

图11 SIG1-SIG4垂直互联结构

图12 SIG4层-SIG18层 垂直互联结构

3 实物与测试

加工完成的接收组件体积为80 mm×80 mm×7.66 mm,工作频段为7.5 ~ 9 GHz,组件共有16个接收模块,每个模块含有低噪声放大器以及八通道幅相控制芯片,对来自16个双圆极化天线单元的射频信号进行接收,每个模块有两个输入端口分别接收左旋圆极化信号以及右旋圆极化信号,经过低噪声放大器与八通道幅相控制芯片后分8路输出,分别送入8套波束合路网络进行合成,合路完成的八波束信号分别从组件的八路输出。

对组件进行测试时,一路输出通道为一组,测试组件16个接收模块的增益以及相位一致性等指标,以其中一路输出通道为例其测试结果如图13所示,在7.5~9 GHz范围内,组件增益大于18 dB,各模块之间相位之差小于5,相位一致性良好,输出驻波比小于1.5,具有良好的射频传输特性,满足低损耗传输需求。

图13 组件测试结果

4 结束语

本文设计了X频段八波束接收组件,基于多层印制板技术实现了组件上众多有源器件以及多套波束合成网络的高密度布局,提升了组件的集成度。基于Wilkinson功分器的形式设计了高效的小型化合路网络,并对组件内部的垂直互联结构进行了精确的建模分析,得出了不同结构参数对于信号传输的影响,通过优化结构参数的方法降低了组件的传输损耗,最后对组件进行了加工测试,在7.5~9 GHz范围内,组件增益大于18 dB,各模块之间相位之差小于5,相位一致性良好,输出驻波比小于1.5,具有良好的射频传输特性,满足低损耗传输需求,且组件尺寸仅为80 mm×80 mm×7.66 mm,更加符合有源相控阵系统的小型化需求。