基于FSMC技术的NorFlsah功能验证系统研究

2024-02-04张思佳李佳俊韦纯进吴佩雯张亭亭

廖 勇,张思佳,李佳俊,韦纯进,吴佩雯,张亭亭

(1.航天科工防御技术研究试验中心,北京 100854;2.西南石油大学 电气信息学院,成都 610500)

0 引言

对于闪存存储器NorFlash而言,国内外大多数生产或测试厂家采用的主流测试方式是使用ATE机台或者存储器专用测试设备进行测试,这些设备可通过编写测试程序完成对NorFlash的功能和各类参数测试,同时可设置多SITE模式实现批量测试,但ATE和存储器专用测试设备的价格往往十分高昂,同时对于传统ATE机台进行存储器功能测试与参数测试而言,还存在测试开发流程复杂的情况,需要编写pin configuration文件、level文件、timing文件、pattern文件、testflow文件等测试程序配置文件,这些测试文件中时序设计和向量文件一般编写较为复杂、编写时间过长,开发效率较低[1]。并且基于NorFlash芯片的特点,在进行测试程序开发时,需要将其容量和功能模式完全覆盖,而测试开发人员在编写存储器测试向量时一般的测试机台无法自动生成测试向量,也无法完成地址的动态递增,单纯靠手动或靠编代码的方式实现半自动地址递增会使得测试向量编写困难,特别是对于256Mbit及以上的NorFlash芯片通过手动复制上千万行测试向量时会使得计算机变得卡顿,完成一个完整的向量编写通常需要几十小时,开发效率极低,而且NorFlash的功能测试涵盖大量控制命令以及种类繁多的控制时序,靠测试人员手动编写测试向量和调整时序会存在较大开发难度,并且由于测试机台测试向量深度的限制,上述方式往往难以覆盖大容量的存储器,进而会增加测试程序开发难度,延长开发周期[2-3]。

针对NorFlash测试存在的问题,可采用FSMC扩展技术进行解决,此技术是STM32系列微控制器单元采用的一种新型的存储器控制技术[4-5]。其中,FSMC内部包含4个模块:AHB接口(包括FSMC配置寄存器)、NOR闪存和PSRAM控制器、NAND闪存和PC卡控制器、外部设备接口等[6]。FSMC接口可以支持扩展静态的内存,如SRAM、NorFlash、NandFlash、ROM等存储器。在进行NorFlash验证测试时,通过设置FSMC控制器,实现对存储器芯片的优化调度,通过对待测NorFlash芯片ID的读取,可以自动匹配不同厂家、不同型号、不同封装的NorFlash芯片测试算法,减少了基于传统ATE机台的存储器芯片测试开发需要编写的pin configuration文件、level文件、timing文件、pattern文件、testflow文件的工作,并且由于要覆盖NorFlash的所有存储空间,常规采用ATE利用手动或者半自动的方式极大依赖于测试机台的向量存储深度和测试机台的编程灵活性,而往往通用大规模集成电路测试机台,如:日本爱德万公司的V93K和美国泰瑞达公司的Ultra-Flex在这两方面做的均不好,除非花费极大的成本完成软硬件升级才能满足大容量的NorFlash的功能测试,但是测试向量编写困难、测试流程复杂且冗余的缺点仍然存在,这样就会极大的增加了测试开发人员的效率,而自主设计的NorFlsah功能验证系统可以较好的解决此问题,可以通过编写代码灵活的完成测试向量中地址动态递增和存储空间数据动态赋值的工作,并且外围电路可配置大容量的存储介质以用于测试向量的存放,从而较好的应对常规测试机在进行NorFlsah测试程序开发时所面临的问题,而且由于编程软件采用Visual Studio 2022进行嵌入式开发,编程的灵活性和可用的函数库更加丰富多样,从而使得测试程序编写的兼容性和可行性大为提升。此外,针对传统的ATE机台的扇区擦除及整片芯片擦除测试时间长的问题,本系统内部集成MATCH功能,可以实时判断芯片的BUSY输出信号及时控制擦除操作,省去芯片额外的擦除时间,极大地增强了系统的测试效率。针对NorFlash而言,在测试时设置具有特殊功能的寄存器,动态调整发出的控制指令[7],动态实现NorFlash存储空间的遍历访问,控制时序设置简单,可便捷的完成对NorFlash的功能测试。

1 NorFlash功能验证技术方案设计

1.1 FSMC拓展技术的应用

本文选择单片机STM32F407IGT6在不增加外部的器件的条件下,可以扩展不同型号、不同类型、不同容量的外部静态存储器[8-10]。在STM32系列单片机,一些引脚被专门设置为地址线、数据线、控制线,这些地址线、数据线等对应着固定的地址[11-12],使用时只需外部存储器将数据线与STM32对应的数据线连接,配置FSMC即可完成访问操作。针对NorFlash而言,选择FSMC内部集成的NorFlash控制器,通过配置特殊寄存器直接完成NorFlash的访问[13-14],其核心工作原理是利用STM32F407-IGT6的高性能 Arm○RCortex○R-M4,32位的RISC内核通过AHB高速总线连接到FSMC,再由FSMC连接至扩展NorFlash的外部总线[15-18]。FSMC接口在CPU与外部扩展存储器实现通讯时起到转换的作用,将CPU对外部NorFlash的访问信号转换为可被外部扩展NorFlash所识别到的信号,并发送给外部扩展NorFlash,实现CPU与外部扩展NorFlash的数据通讯[19-20]。

1.2 NorFlash功能验证系统框架搭建

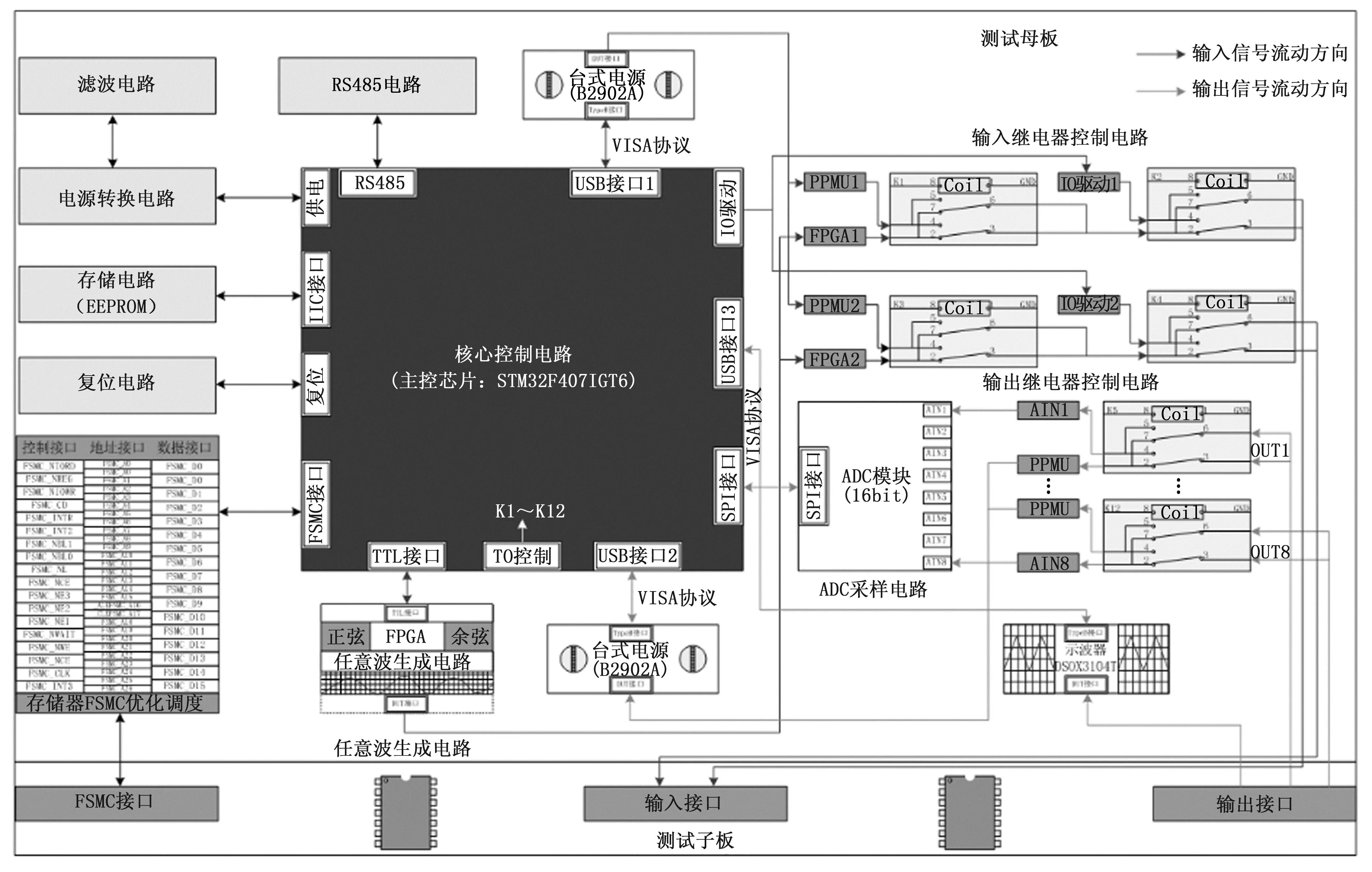

NorFlash功能验证系统框架如图1所示,此系统框架主要涵盖12个部分,分别是:以STM32F407IGT6为核心的主控电路、供电电路模块、RS485电路、AD7606电路、输入继电器控制电路、输出继电器控制电路、输入源控制电路、输出源控制电路、波形产生电路、示波器及通讯电路、台式电路及通讯电路、数字万用表及通讯电路;

图1 NorFlash 功能验证系统框架

图1详细的展示了测试母板中各部分电路的连接1关系,图中,深色线标识输入信号的流动方向,浅色表示输出信号的流动方向。输入信号即被测芯片的激励信号流动轨迹如下:输入激励信号(单片机激励源、高精度台式电源、波形产生电路)→输入信号选择电路→输入接口→被测芯片;输出信号即被测芯片输出信号的流动轨迹如下:被测芯片输出信号→输出接口→输出测试源选择电路→测试源(高精度台式电源、高精度AD采样电路和高性能外部示波器)。各个组成单元都承担着十分重要的作用:

核心控制电路是整套功能验证系统的关键组成部分,它以STM32F407IGT6为主,该芯片内部集成了可变静态存储控制器FSMC,通过集成的Thumb-2高密度指令集设置特殊功能寄存器,如图1所示,然后FSMC接口利用控制接口、地址接口和数据接口可以依据不同的外部存储器类型发出相应的数据/地址/控制信号以匹配信号的速度,在不增加外部器件的情况下就可以实现对不同厂家、不同容量、不同协议的NorFlash进行地址的遍历、向量的动态生成、时序的便捷设置,极大增强了该系统的兼容性和灵活性。

基于VS2022开发平台,它涵盖大量的库函数固件库,在进行初始化时便用到会用到FSMC_ NORInit()、FSMC_NANDInit()、FSMC_ SRAMInit()等库函数,还有FSMC 的使能函数FSMC_ NORInit()、FSMC_NANDInit()、FSMC_ SRAMInit()等,而且 FSMC 读写时序、地址建立保持时间,数据建立时间等配置也可以在调用库函数的基础上进行编程开发。总之,库函数调用十分方便,嵌入式软件编程非常灵活。

但是在嵌入式编程时也有需要注意的地方,FSMC进行NorFlash访问时有几个寄存器非常重要,其中FSMC_BCRx控制寄存器可配置要控制的存储器类型、数据线宽度以及信号有效极性能参数,FSMC_BTRx时序寄存器用于配置NorFlash访问时的各种时间延迟,如数据保持时间、地址保持时间等,FSMC_BWTRx写时序寄存器专门用于控制写时序的时间参数,但是在所调用的ST官方库中,并没有定义FSMC_ BCRx、FSMC_BTRx、FSMC_BWTRx等寄存器,而利用一些规则进行组合而得到,其中FSMC_ BCRx和FSMC_BTRx组合成BTCR[8]寄存器组,其规则如表1所示。

表1 FSMC_ BCRx、FSMC_BTRx与BTCR[8]对应关系

而FSMC_BWTRx则组合成BWTR[7],表2为其对应关系:

表2 FSMC_BWTRx与BWTR[7]对应关系

表3 VOL测试结果

表4 VOH测试结果

表5 VIL测试结果

表6 VIH测试结果

供电电路模块,由于不同芯片的供电范围不同及大量驱动器的驱动,因此设计了12 V转5 V,5 V转3.3 V的电路,用于母板与子板不同芯片的供电需求以及大量继电器的驱动。

RS485通讯电路,用于提供与上位机软件的通讯,使用的是RS485的半双工模式,只需要两根通信线(A,B)即可完成数据通信。

AD7606电路,16位精度、可8路并行的ADC模块,用于采集DUT的直流参数,再将采集完成的参数反馈给STM32F407IGT6进行数据的处理。

输入继电器控制电路、输出继电器控制电路,通过继电器,完成I/O通道的开启与关闭。

输入源控制电路,该电路主要用于输入激励信号的选择,激励信号可以选择单片机激励源、高精度台式电源、波形产生电路作为DUT的输入激励源。核心控制算法可以根据器件的不同频率、不同精度的激励需求,对这3种激励信号灵活选择。通过VISA协议,本系统可以对高精度台式电源进行程控,实现程序对激励信号幅值的动态调整;单片机激励源可提供常见的高电平、低电平驱动信号;波形产生电路可提供常见的正弦波、余弦波等激励信号,可以根据不同器件动态调整驱动需求。

输出源控制电路,该电路主要用于对测试芯片输出信号测试源进行选择,输出信号测试源包括高精度台式电源、高精度AD采样电路和高性能外部示波器3种。通过VISA协议可以在上位机对高精度台式电源进行程控,根据不同芯片动态的进行VIH、VIL、VOH、VOL等直流参数的测试。高精度AD采样电路以16位精度的AD7606为核心,可同时采集8路输出信号的数据,提高采样效率。外部高性能示波器主要用于对交流参数的测试,可以实现对输出使能到数据有效时间tOE、片选到数据有效延迟时间tCE、地址到输出延迟时间tACC等交流参数的抓取。波形产生电路,由于不同的DUT对输入激励需求不同,常规的存储器输入激励包括:驱动高、驱动低等,同时对激励信号的测试频率要求较高,通常高速存储器的输入激励频率要求达到150 MHz左右。因此设计以FPGA芯片XC7A100T为主控配合双路10位DA模块及部分外设电路的任意波生成电路,满足不同频率的激励需求,该电路可以同时生成4路不同频率的信号,而且信号最大频率可以达到200 MHz,能够覆盖大多数存储器的输入激励需求。根据不同的DUT输入激励需求,核心CPU STM32 -F407IGT6可通过TTL接口对该电路发出控制指令,产生不同类型、不同频率的激励信号,输出包括:正弦波、余弦波、锯齿波、方波、高电平、低电平、差分信号等,电压覆盖:2.7~5 V动态变化,频率覆盖:0~200 MHz动态变化,核心CPU可以根据不同被测器件的需求改变输出信号的相位及幅值。

示波器及通讯电路,利用type-B接口通过VISA通讯协议,实现对芯片的交流参数的测试高精度台式电源及通讯电路,利用type-B接口通过VISA通讯协议,以及输入、输出源继电器,可以实现对芯片电信号的施加、直流参数的测试与采集、输入源的激励。

数字万用表及通讯电路,7位半精度,利用GPIB通过VISA通讯协议,实现对DUT高精度的电信号测试。

整个NorFlsah功能验证系统的所有组成可以大致分为两大核心,第一部分是:基础功能验证,包括ID读取,读操作,写操作和擦除操作等,这是整套验证系统的关键和前提;第二部分是:参数测试系统,参数的测试除了完成芯片手册的基本规定指标之外,它也是功能验证非常关键的一种辅助验证手段,换而言之,参数测试更加系统和全面的支撑了NorFlsah的功能验证。

2 NorFlash功能验证系统测试流程

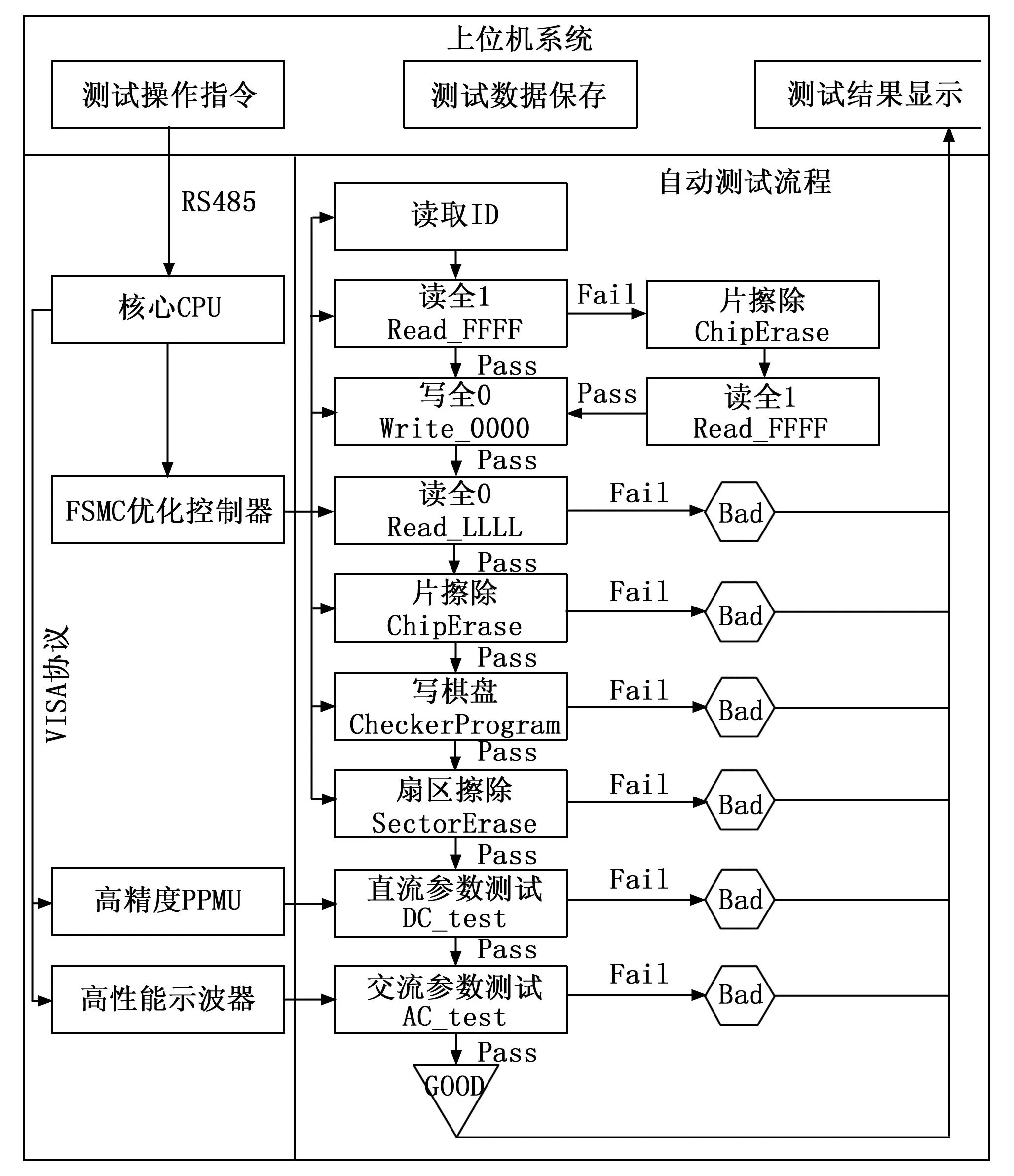

本系统的验证流程设计如图2所示:上位机通过RS485总线给测试母板核心CPU下发测试指令,母板接收到测试指令后启动测试流程,整体NorFlash验证流程包含:功能验证与参数测试。

图2 NorFlash 验证流程

其中,对于NorFlash 功能验证,首先要完成FSMC拓展接口的配置,其核心为STM32F407IGT6调用内置的FSMC拓展接口,FSMC内部有3个控制寄存器,配置FSMC_BCR控制寄存器完成NorFlash 类型选择、数据线宽度以及写使能操作;FMC_BTR读时序寄存器用来控制与读操作相关的时序,如数据保持、地址保持等时序;FMC_BWTR写时序寄存器用来控制与数据写入存储器相关的时序。对于被测芯片的功能测试输入激励形式,默认情况下功能测试采用FSMC接口,无需额外的外部输入激励即可完成功能测试。当需要特殊的外部激励,例如,目前大部分存储器芯片均具有高电压擦除功能,如需要验证该 功能,则需要特定引脚施加规定电压才能完成,基于以上特征,可对该引脚设定外部高精度台式电源作为输入激励源,完成程控配置后,点击测试按钮,系统将自动开始执行测试流程。与传统ATE机台相比,通过CPU内部的FSMC配置,可以省去对pinmap文件、level文件、timing文件、pattern文件、testflow文件的编写工作,提高测试开发效率。

然后,上位机软件通过RS485传输线下发控制指令,CPU接收到指令后调用FSMC拓展接口,FSMC内部根据芯片种类动态调整地址、数据和时序,实现自动测试操作,完成包括全0(0x00)、全1(0xFF)、棋盘(0x55)、反棋盘(0xAA)、片擦除、扇区擦除等测试图形的向量输入以及对应测试图形的数据读取,完成对NorFlash全地址覆盖的读写操作;在完成功能验证后进行参数测试,参数测试包含直流参数测试与交流参数测试,对于直流参数,CPU将控制输入输出继电器对DUT的对应通道的打开或关闭,可以实现对DUT的串、并行测试。根据不同器件的输入激励需求,CPU可以选择单片机激励源、高精度台式电源、波形产生电路为器件的输入激励源。CPU可以通过切换高速继电器选择使用TTL协议调用波形生成单元,产生供DUT使用的激励信号或者使用type-B接口利用VISA协议调用示波器或台式电源产生激励。

完成合适的激励源施加后,根据不同芯片的测试需求,可以进行包括高精度台式电源、高精度AD采样电路和高性能外部示波器3种输出测试源的选择。若不用PPMU功能,采用CPU利用SPI协议调用AD7606模块或者通过type-B接口利用VISA协议调用数字万用表实现对直流参数的测量;使用PPMU功能,利用type-B接口利用VISA协议调用台式电源,实现对DUT的四象限测试;CPU将测量完成后的数据进行采集,通过RS485接口,将数据发送至上位机软件进行数据分析与处理。

当测试开始后,一旦有测试数据上传至上位机软件后,数据就会被上位机软件进行处理,按照指定的数据解码协议(MODBUS协议)进行解码,然后将测试数据在上位机界面显示出来,同时,由于对测试参数进行了阈值设定,若采集的数据在设定的阈值范围内,则会出现“PASS”标志,测试程序按照顺序继续执行;反之,若测试数据没有达到关键阈值,则会出现“FAIL”标志。以此来完成对器件逻辑功能的验证,比如:对于NorFlash存储器,写入全0功能测试时,当读取的低电平信号在VOL的阈值范围内时,将会输出“PASS”,反之,则会出现“FAIL”。与此同理,其他参数的测试也是同样的判断机制和处理模式。因此,此系统可以很好地完成待测器件的功能验证以及交、直流参数测试,测试精度能够达到小数点后4位。并且所有的测试数据能够进行实时的波形显示,用于分析整个测试周期内测试数据的波动情况,极大的提高了对器件的性能分析。测试数据都能以专业的格式生成EXCEL表格导出。

3 NorFlash功能验证系统测试试验与数据分析

3.1 S29GL系列功能验证

本文选用S29GL系列芯片作为测试对象,具体选型为:S29GL128P10TFI101、S29GL256P10TFI101、S29GL512P10TFI102、S29GL01G13TFI102容量分别为16 MB、32 MB、64 MB、128 MB。测试系统搭建如图3所示,上位机软件通过USB转RS485连接线与NorFlash 功能验证装置进行硬件连接,通过USB转type-B连接线与示波器、高精度台式电源进行连接。

图3 NorFlash功能验证系统实验实物图

从图2可知,对于S29GL芯片系列来说,功能验证包括:读、写、擦除三部分,具体的功能设置项涵盖:读ID、读全1、写全0、读全0、片擦除、写棋盘、读棋盘等功能。

图4为S29GL128P芯片的功能测试截图,展示了读取设备ID、读取芯片及制造商ID、读取前128个扇区数据功能。

图4 读制造商ID和设备ID

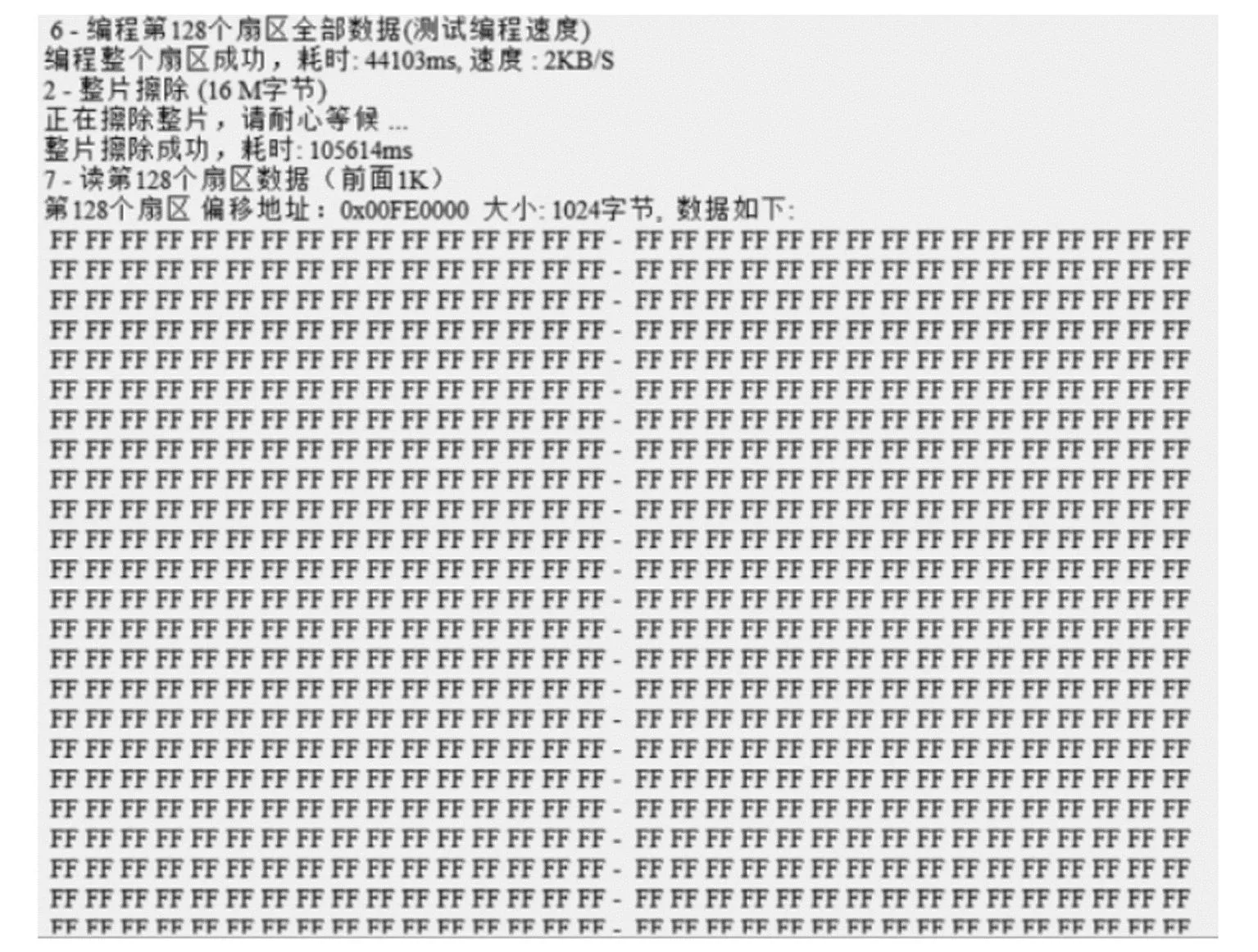

传统ATE机台对于NorFlash存储器的功能测试而言,由于需要对其大量的指令重复进行编写,重复进行读取,使得单片测试时间几乎都在30~40分钟。由于FSMC内部集成对NorFlash读、写操作不同的时序控制寄存器无需重复编写指令、时序文件,由图5~6可以看出,向前128个扇区编程得时间为44 103毫秒,约等于0.74分钟,并且在上位机软件窗口能够打印出读取编程的数据,以验证是否编写成功。

图5 向指定扇区编程

图6为整片芯片擦除,由图6可以看到,由于系统内部集成MATCH算法,可以实时的对芯片的BUSY输出信号进行判断,能够及时的控制擦除操作,因此整片擦除时间为105 614毫秒,约等于1.8分钟,使用传统ATE机台测试,无法实时对擦除时间进行动态监控,其整片擦除约为3~4分钟。擦除完成后再向芯片读取数据,以验证是否擦写完成。

图6 整片擦除

对于存储器功能验证而言,相较于ATE机台,本系统通过使用FSMC技术,减少了对于数据的写入和读取时大量重复的指令输入,减小芯片功能验证的时间,由原来的ATE机台单片测试30~40分钟降低为10分钟以内,极大的缩小了测试等待时间;同时,本系统内部测试算法MATCH则将原来的ATE机台片擦除时间由3~4分钟降低至1.8分钟。

3.2 关键参数测试分析

选取VOL、VOH、VIL、VIH、ICC1、ICC4、tACC作为芯片关键测试验证参数,直流参数每个容量选取3个器件,取平均后进行分析比对。交流参数器件后缀不同,器件的读写速度不同,因此交流参数为同容量3个器件互相对比分析。其中,VOH、VOL为器件的输出高、低电平,可以检测器件在指定电流条件下输出电压的能力,VIH、VIL为器件的输入高、低电平,用于判断芯片输入高电平和低电平的最低限制数值,ICC1、ICC4为器件的工作电流(动态电流)和静态电流,反应器件在工作和不工作情况下的功耗,tACC为器件地址到输出延迟时间。

3.2.1 VOL测试

测试条件为:选取VIO=VCC =3.0 V,IOL = 100 μA。

3.2.2 VOH测试

测试条件为:选取VIO=VCC =3.0 V,IOH=-100 μA。

3.2.3 VIL测试

选取VIO=VCC=3.0 V,根据测试原理,测试参数应该具有覆盖性,当测量VIL值时,应该选取手册规定值的最大值作为测试卡限的最小值。

根据测试规范VIH和VIL测试值的卡限应该在VIH的最小值与VIL的最大值之间,四型待测芯片测试得到的实际VIL的数据符合芯片手册的参数卡限值,说明该系统方案对VIL的测试符合测试规范。

3.2.4 VIH测试

选取VIO=VCC=3.0 V,根据测试原理,测试参数应该具有覆盖性,当测量VIH值时,应该选取手册规定值的最小值作为测试卡限的最大值。

四型待测芯片测试得到的实际VIH的数据符合芯片手册的参数卡限值,说明该系统方案对VIH的测试符合测试规范。

此处对VIH和VIL的测试是通过采集VOH和VOL的值进行判断的,具体过程为:以VIH测试为例,通过编写一个FOR循环,设置一个VIH的起始值,然后按照一定的步长动态增加VIH的数值,然后判断VOH的数值是否符合高电平的卡限值,FOR循环起始执行过程使得输出为低电平,当VIH的数值到达一定值后,芯片输出VOH符合高电平的数值,此时的VIH的值即为测试值,提取此时输入高电平的值VIH,然后上位机判断此时的VIH是否在芯片手册规定的卡限内,如果在那么此时测试数据正确,反之不正确。同理,VIL的测试过程与VIH相反,本文不再赘述。

3.2.5 ICC1测试条件为:CE#=VIL,OE#=VIH,VCC=3.6 V

由表7可知,四型被测芯片的工作电流ICC1随着工作频率的增加而增加,各系列的ICC1均在器件手册给的典型值上下浮动。总体而言,四片待测芯片测试得到的实际ICC1的数据符合芯片手册的参数卡限值,说明该系统方案对工作电流ICC1的测试符合测试规范。

表7 ICC1测试结果

此处,被测器件的动态电流测试过程中,一直会持续给芯片的地址进行赋值操作,会持续对数据引脚进行输出电平判断工作,既让“测试向量”持续运行,其目的在于是芯片处于工作状态,进而让测试的电流为工作电流。

3.2.6 ICC4

测试条件为:CE#、RESET#=3.6 V±0.3 V,OE#=VIH,VCC=3.6 V,VIL=VSS+0.3 V/-0.1 V。

由表8可知,四型待测芯片测试得到的实际静态电流ICC4的数据符合芯片手册的参数卡限值,说明该系统方案对静态电流ICC4的测试符合测试规范。

表8 ICC4测试结果

此处,被测器件的静态电流测试过程中,不会持续给芯片的地址进行赋值操作,不会持续对数据引脚进行输出电平判断工作,既让“测试向量”持续不运行,其目的在于是芯片处于非工作状态,进而让测试的电流为静态电流。

3.2.7 tACC

S29GL128P10TFI01:将三片器件分别命名为A-S29GL128P10TFI01、B-S29GL128P10-TFI01、C-S29GL128P10TFI01。测试条件为VIO = VCC = 3.0 V。

S29GL256P10TFI01:将三片器件分别命名为:A- S29GL256P10TFI01、B- S29GL256P10TFI01、C-S29GL256 P10TFI01。测试条件为VIO = VCC = 3.0 V。

S29GL512P11TFI02:将三片器件分别命名为A- S29GL512P11TFI02、B- S29GL512P11TF -I02、C- S29GL256P -11TFI02。测试条件为VIO = VCC = 3.0 V。

S29GL01GP13TFI02:将三片器件分别命名为A- S29GL01GP13TFI02、B- S29GL01GP -13TFI02、C-S29GL01GP13TFI02。测试条件为VIO = VCC = 3.0 V。

由表9、表10、表11、表12可知,四型待测芯片测试得到的地址到输出延迟时间tACC的数据符合芯片手册的参数卡限值,说明该系统方案对地址到输出延迟时间tACC的测试符合测试规范。

表9 S29GL128P系列tACC测试结果

表10 S29GL256P系列tACC测试结果

表11 S29GL512P系列tACC测试结果

表12 S29GL01GP系列tACC测试结果

3.2.8 片擦除

由表13可知将每个容量3片芯片片擦除后取平均,最终测试值均略高于典型值,远小于最大值,符合测试规范。

表13 片擦除测试结果

4 结束语

本文介绍了基于STM32F407IGT6作为核心主控采用FSMC拓展技术实现NorFlash全地址动态访问、时序灵活配置、向量自动生成进而完成功能验证的全过程,解决了基于传统ATE机台存在的测试机台向量深度不足、全地址存储空间覆盖困难、测试时序编写复杂的问题,同时也增加相应的外接源表程控方法可实现部分交直流参数测试,该系统逻辑功能判断准确,数据采集高效且精准,测试系统操作简单。

并对S29GL系列不同容量的芯片进行读、写、擦除等全功能验证,完成VOL、VOH、VIL、VIH、tACC等交直流参数测试,完成片擦除工作,验证了NorFlash功能验证系统的可靠性,为闪存存储器测试与验证提供一种新的经济、高效、可定制的测试方案。