一种抗噪声折叠宽范围低杂散小数分频锁相环

2024-01-06蔡剑茹尹勇生滕海林杨文杰

蔡剑茹, 尹勇生, 滕海林, 杨文杰, 孟 煦

(1.合肥工业大学 微电子设计研究所,安徽 合肥 230601; 2.合肥工业大学 教育部IC设计网上合作研究中心,安徽 合肥 230601)

Ⅱ型锁相环(phase locked loop,PLL)具有良好的性能折衷和技术成熟度,已成为当下各类片上系统中最为常用的时钟产生电路架构。 基于环形振荡器(ring oscillator,RO)的设计具有多相位输出、输出频率范围广、芯片面积小等诸多优点,受到设计者的重视。 根据输出频率精度是否受限于参考源频率fREF,PLL可以分为整数型和小数型2种类别。 小数型PLL利用和差调制器(delta-sigma modulation,DSM)控制多模分频器(multi-modulus divider,MMD)的分频比动态变化,从而在平均效果下实现N.f分频。 传统小数型PLL结构如图1所示。

图1 传统小数型PLL结构

灵活的输出频率使得小数PLL逐渐替代整数PLL成为时钟和频率产生的主流架构。 由于只能实现动态锁定,小数锁相环路中的电荷泵(charge pump,CP)会随着反馈信号的超前或滞后,对环路滤波器进行相应的放电或充电。 从图1可以看出,当电荷泵电流存在失配ΔICP时,流入环路滤波器的净电荷量为:

(1)

其中,t0为鉴频鉴相器(phase frequency detector,PFD)的复位延时。 由式(1)中右边的第2项可以看出,PFD/CP的输入输出特性中存在非线性关系,即非线性环节存在,会将DSM搬移至高频偏处的量化噪声重新折叠回低频偏处,恶化带内噪声性能[1-4]。

文献[5-6]通过刻意偏移PFD/CP的工作区,实现对环路的线性化,但在控制电压上引入的波动恶化了参考杂散性能;文献[7]通过提出基于采样保持的线性化电荷泵及其时序控制电路,在参考信号脉宽发生变化时,仍具有较好的杂散抑制效果,但是时序控制模块较为复杂;文献[8]使用连续线性电流替代传统电荷泵,对参考杂散的改善效果有限;文献[9]通过使用脉冲偏移电流实现环路的线性化,降低了控制电压上的波动,但是固定的脉冲宽度仅适用于单一输出频率的情况,与RO所能提供的宽输出范围相悖。

本文提出一种根据输出频率变化、自适应调节偏移脉冲电流宽度的线性化技术,在避免噪声折叠的同时,始终保持环路良好的参考杂散性能。

1 抗噪声折叠技术回顾

避开PFD/CP非线性工作区间是有效抑制噪声折叠的方法,如在PFD充电[5]或者放电[6]路径的复位端引入一段延时,或是在电荷泵与低通滤波器之间加入直流偏移电流,因而PLL环路会在PFD的输入端引入反向的偏移以达到平衡,维持锁定。 PFD/CP线性化技术如图2所示。 图2b中,Inet=IUP-(IDC+IDN)。 图2d中,Inet=IUP-(IPul+IDN)。

图2 PFD/CP线性化技术

由图2a可知,若直流偏移电流大小为IDC,则环路锁定后,为了维持参考电压即输出频率的不变,参考信号REF相对于反馈信号FB的平均值将提前IDCTREF/ICP的时间到达。 根据DSM的设计及行为级仿真结果,当选择足够大的IDC,即可保证在FB存在瞬时跳变的情况下,REF仍始终领先。 PFD/CP的输入输出特性可表述为:

Qnet(Δt)=IUPΔt-IDCTREF+ΔICPt0

(2)

其中:IUP为充电电流大小。

由式(2)可知非线性的分量得以去除。 由图2b可知,偏移电流IDC的引入,会使得控制电压VC上出现约IDCTREF/C2的波动,恶化参考杂散。

由图2c、图2d可知,通过将偏移电流改为大小为IPul、宽度为TPul的脉冲电流[9]形式,即通过满足IPulTPul=IDCTREF的关系,可引入与前文相同的偏移电荷量,实现对环路的线性化;进一步保持脉冲的开启与参考源大致同步,可使环路控制电压上的波动大大改善。

2 基于自适应脉宽的线性化技术

上述仿真中的电流脉宽是为当前输出频率所定制化选取的。 考虑到DSM在反馈信号FB上所引入的跳变量与输出信号周期TVCO相关,因此当输出频率减小时,所设定的脉冲电流的宽度可能不再足以将环路完全线性化,令噪声折叠现象不能被完全移除。 相对地,根据PLL输出的最低频率设计一个较宽的偏移脉冲电流,虽然可以始终保持环路的线性化,在输出高频率时却令CP额外导通了不必要的时长,同样导致带内噪声性能较理想情况有所下降。

为了实现在输出频率变化时,依然能实现合适的偏移量,兼顾去噪声折叠和适当的CP导通时长,有必要令偏移电流的脉宽实时跟踪VCO的输出频率,因此本文提出自适应脉宽产生电路(pulse generator,PG),如图3所示,其核心之处在于采用了与VCO相同的延时单元产生所需的脉冲宽度。 若组成振荡器的延迟单元延迟时间为td,则N级环形振荡器的工作频率为:

图3 窄脉冲产生结构原理

fVCO=1/TVCO=1/(2Ntd)

(3)

因此使用m×2N个延迟单元即可实现m×TVCO长度的延迟,且由于与PLL共享了控制电压,所产生的延迟具有良好的抗PVT波动特性。

3 电路设计及仿真结果

本文设计的小数分频PLL结构如图4所示。

图4 小数分频PLL结构

环路内嵌低压差线性稳压器(low dropout regulator,LDO)[10]提升了振荡器对电源噪声的抑制能力,从而可以简化振荡器的设计。 仿真显示,设计的DSM在反馈路径上引起的瞬时跳变范围约为3.5TVCO,因此在脉宽产生电路中应输出约1.8TVCO的延迟以线性化环路。 锁定检测(locked detector,LD)[11]电路与PFD输出信号的相位差比较,当两者相位差维持低于设定值时,开启偏移脉冲电流产生模块。 本文偏移电流的大小等于电荷泵电流大小,简化了整体设计考量。

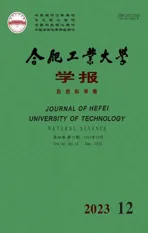

因为环路结构具有优越的电源噪声抑制能力,所以在VCO的设计中采用9级单端反相器级联的形式,多相位的输出亦为后续的应用提供充足的便利性。 脉冲产生模块仿真结果如图5所示。 由图5a可知,当控制电压VC从0.60 V变为1.35 V时,输出频率覆盖0.6~2.7 GHz,VCO增益KVCO为3 GHz/V;当VC为1.05 V时,输出目标频率为2.0 GHz,功耗为7.5 mW。

图5 脉冲产生模块仿真结果

由式(3)可得,偏移脉冲电流的脉宽应由约32个(1.8×2×9)延迟单元构成,但如此数量的延迟单元会引起面积的大幅增加及功耗的上升。 以反相器放电为例,考虑到反相器放电过程中的总寄生电容Ctot和MOS管的等效导通电阻Rn[12],即

(4)

(5)

其中:Wp、Lp分别为PMOS管的栅宽和栅长;Wn、Ln分别为NMOS管的栅宽和栅长;m为每一级反相器的NMOS与PMOS的并联个数;Wn/Ln为NMOS的宽长比;Kn为NMOS的场效管增益系数;ID,sat指MOS管处于饱和区时的电流大小;Cox为单位面积栅氧化层电容大小。 图5a中,Wp=700 nm,Wn=300 nm,Lp=Ln=130 nm,m=50。

单级反相器所引入的延迟时间td=0.7RnCtot,实则为一个与NMOS晶体管和PMOS晶体管宽度W的比值相关的量。 这使得可以在实现目标脉宽的32个延迟单元中采用等比复制技术,如将m缩小为原值的1/50,进而实现脉宽产生电路面积和功耗大大降低。 本文通过在振荡器和延迟单元中采用尺寸相同、数量不同的方式,进一步提高复制的精度。 由图5b可知,在VCO的输出频率范围内,基于1/50等比复制单元所产生的脉宽始终与1.8TVCO的目标宽度极为接近,两者误差最大仅为3.75%。VC为1.05 V时所消耗的功耗也仅为14.7 μW,相对于非等比复制的结构,功耗降低了50倍。

DSM使用MASH1-1-1结构的3阶DSM调制器。 使用基于脉冲吞咽计数器的多模分频器,输入频率为55.25 MHz时,通过分频比的调整,可输出范围为0.6~2.7 GHz的信号。 环路中内嵌的LDO结构的非对称性有利于实现LDO的低功耗。 当VC=1.05时,LDO的电源噪声抑制能力约为60 dB。 电荷泵的电流大小为8 μA,充电电流设置失配电流单元,失配电流单元选取0.08、0.08、0.16、0.32 μA,分别代表1%、1%、2%、4%的失配,模拟电荷泵范围为1%~8%的电荷泵失配的情形。

表1 PLL设计参数

最终的PLL设计参数见表1所列。 需要指出的是,相对于常规设计,本文充分考虑了线性化技术在CP中引起的额外导通时间,并通过增加CP电流的方式达到预期的带内噪声。

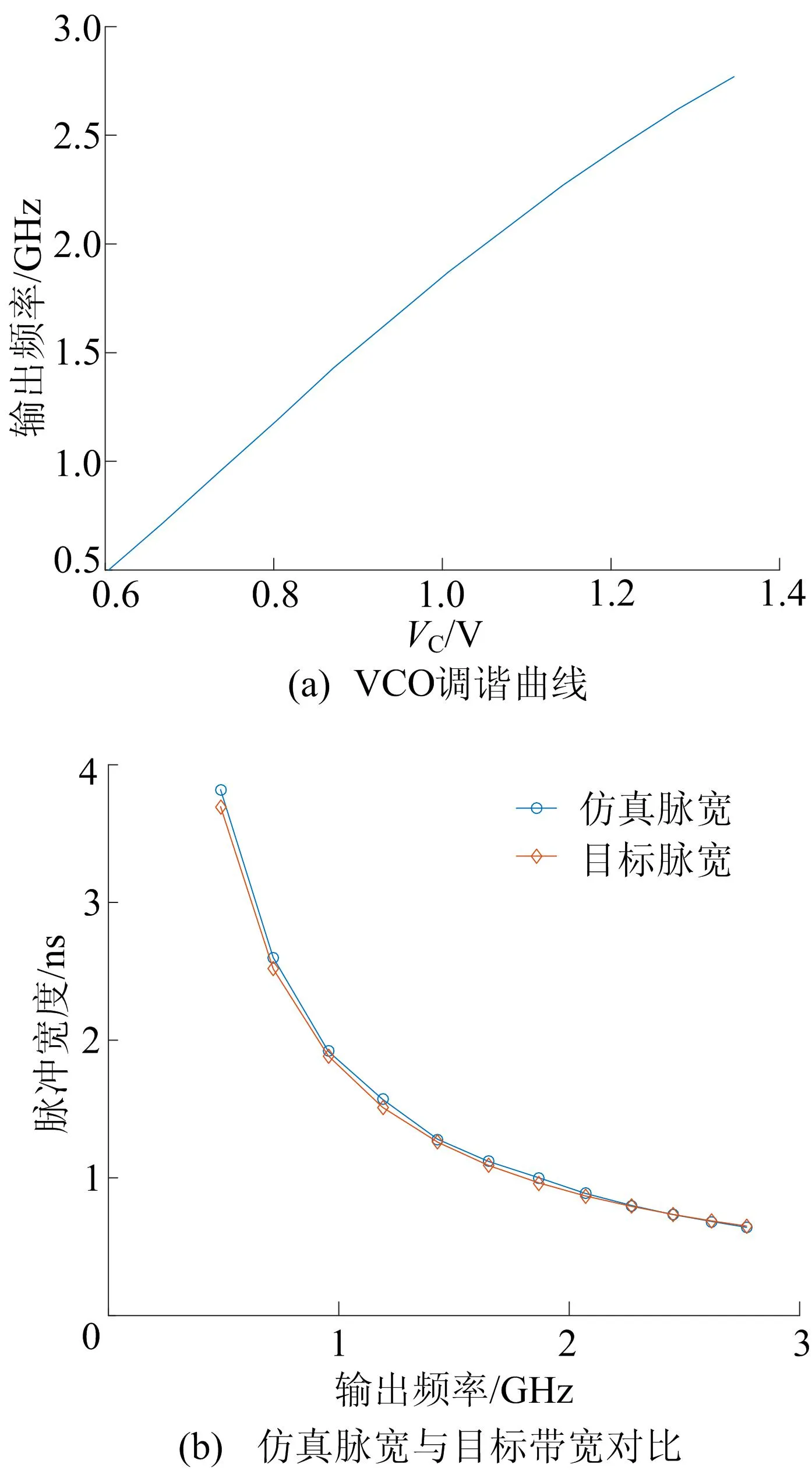

输出频率为2.0 GHz且CP中存在8%失配情形下,锁相环的各项仿真性能如图6所示。

图6 自适应脉宽补偿性能仿真结果

由图6a可知,在Cadence Spectre下,对电路进行瞬态仿真后得到输出频谱,此时参考杂散约为-63 dBc。 由图6b可知,通过Cadence Spectre仿真提取电路各模块的参数和性能指标后,带入系统仿真软件CppSim得到相位噪声曲线,通过脉冲偏移电流线性化环路后,带内噪声性能优化了7 dB,噪声折叠现象得以避免。 由图6c可知,通过使用固定脉宽(1.2、1.5 ns)与使用自适应脉宽2种线性化方案下带内(@100 kHz)相位噪声的对比,所提出的自适应脉宽的线性化方案在全部的输出频段内均可以避免噪声折叠现象,且通过维持最优的脉冲宽度,在输出高频时达到了相对优化的带内噪声性能。 文献对比结果见表2所列。

表2 文献对比结果

4 结 论

本文设计了一个具有自适应抗噪声折叠能力的宽输出范围小数分频PLL。 通过等比复制技术所设计的脉宽产生电路能够在工艺、电压、温度变化的情况下,始终适应PLL的工作频率,以最优的电流脉宽实现对环路的线性化,避免噪声折叠现象,且维持良好的参考杂散性能。 所提出的自适应脉宽产生方案对于其他结构的设计同样适用。