一种基于flash 的硬件ECC 设计原理及实现

2023-12-28段曦冉

段曦冉

(中国电子科技集团公司第四十七研究所,沈阳 110000)

1 引 言

随着芯片技术的进步,对flash 的容量要求也在快速增加。但由于工艺的局限性和复杂性,往往越大容量的flash 越容易出现位翻转问题。为提高系统可靠性,尽可能避免数据错误的发生,不仅要提高工艺可靠性,也要对数据进行校验。针对这种情况,需要在flash 控制器中加入ECC(Error Checking and Correction)校验纠正设计。传统的校验方法有奇偶校验、循环冗余校验(CRC)和汉明校验。奇偶校验是最常见的校验方法之一,其原理是在数据末尾加上1 位校验位。这种算法仅需1 位校验码就可以检测出1 位数据出错或奇数个位出错。CRC 校验是通过模2(mod 2)运算,其特征是信息字段和校验字段可以任意选定长度。这种算法优点是错误检测能力很强。汉明校验是在有效信息位中加入校验位形成汉明码。汉明码编译简单,不仅能校验数据,还能定位数据错误位置,因此基于汉明码的ECC 技术被广泛使用[1-2]。在此对flash 控制器中错误检测纠正的设计原理和实现过程展开研究。

2 ECC 工作原理

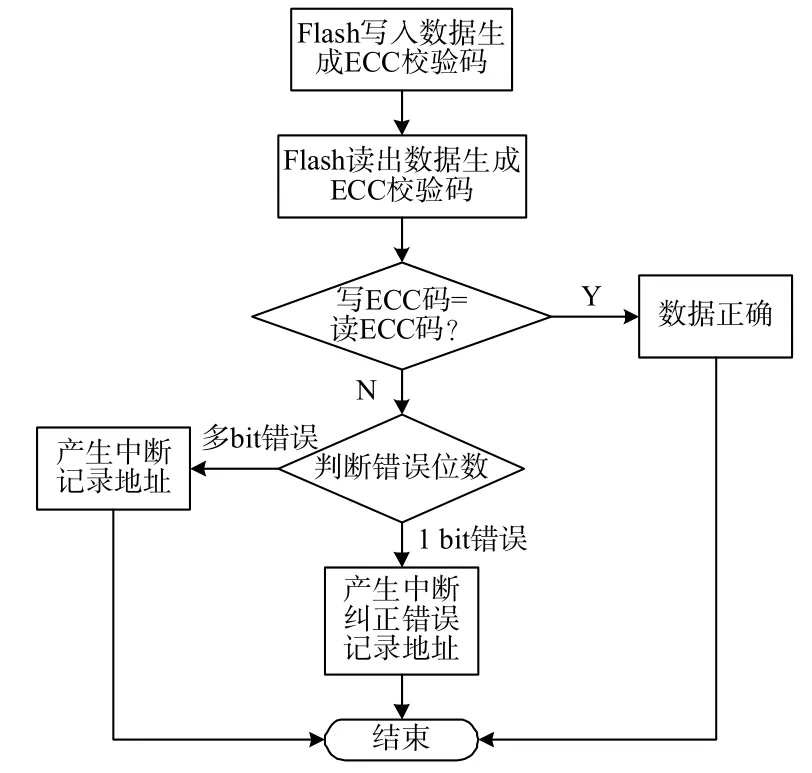

对于flash 读数据出现错误的情况,1 位错误的处理措施是产生单错误中断标志、纠正1 位错误并记录错误地址;多位错误的处理措施是产生多错误中断标志并记录错误地址。ECC 工作原理的简单之处在于,在使用时一定会检测并纠正1 位错误,一定会检测到2 位错误。

基于汉明码的ECC 校验由奇偶校验发展而来,改进了以往校验只能检测出错误而无法纠正的弊端。其工作原理为在数据后加入校验码,当1 位数据发生翻转时,会发生半数校验码计算值不一致。通过对不一致校验码进行比较,可以确定具体错误比特位,进而纠正数据。当2 位发生翻转时,会发生校验码计算值不一致,只可以确定具体地址错误,无法判断具体比特位。当多位发生翻转时,且校验码计算值不一致时,只可以确定具体地址错误,无法判断具体比特位。多位发生翻转时校验码计算值可能不变,但是概率极低、基本不会发生。

在此设计的ECC 是基于144 位flash,以128bit数据为单位计算校验码,将128bit 数据分为16 个字节,相应的校验位有14 位。在flash 写入数据时,同时写入校验码,读取数据后就可进行校验码比较。当校验码不一致时便可判定数据错误,此时判断数据错误是1 位错误或是多位错误。1 位错误产生中断、记录地址并在纠正错误后输出正确数据,多位错误数据产生中断、记录地址输出错误数据。具体流程参考ECC 校验流程图,如图1 所示。

图1 ECC 校验流程图

为直观描述校验码计算过程,将128bit 数据分为16 个字节并排列为计算矩,共计8 列16 行数据。ECC 校验码计算如表1 所示。

表1 ECC 校验码计算表

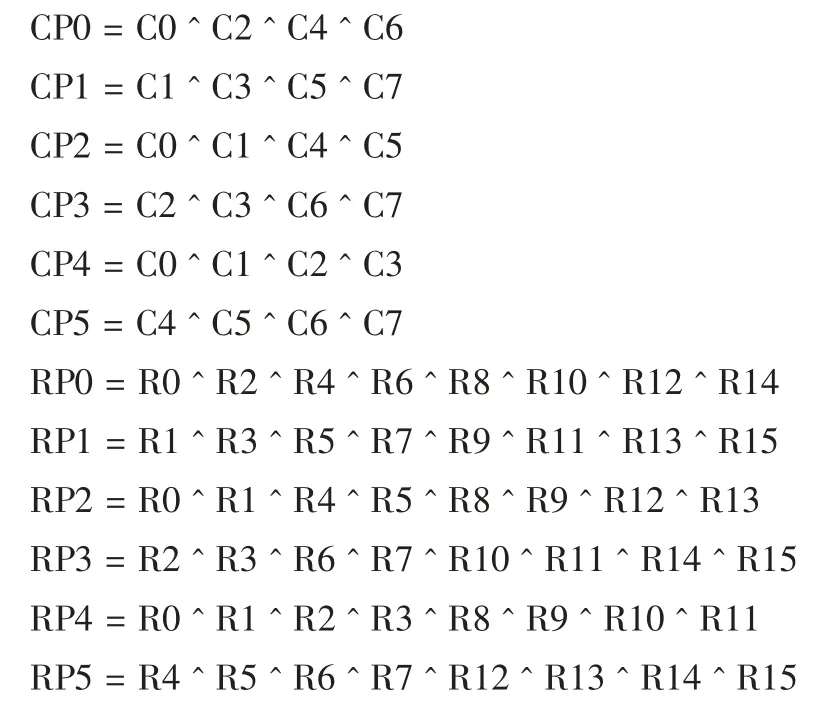

相应的ECC 校验码计算为一系列的异或操作,算式如下(Cn代表n 列数据,Rn代表n 行数据):

计算后将数据位和校验位存储在flash 中,读出后根据数据位重新计算校验码比较。

3 ECC 设计与实现

基于设计和实际的硬件情况,ECC 整体上由三个模块组成,即:ECC 校验码计算模块、ECC 校验纠正模块和ECC 寄存器模块。其中,ECC 校验码计算模块在写flash 时起作用,ECC 校验纠正模块在读flash 时起作用,ECC 寄存器模块则用于存储ECC标志位和flash 错误地址。所设计的ECC 的结构框图如图2 所示。

图2 ECC 结构框图

ECC_en 是ECC 寄存器中ECC 使能位,可以由系统总线控制。信号data_e 为数据错误标志。ADDR为flash 地址。

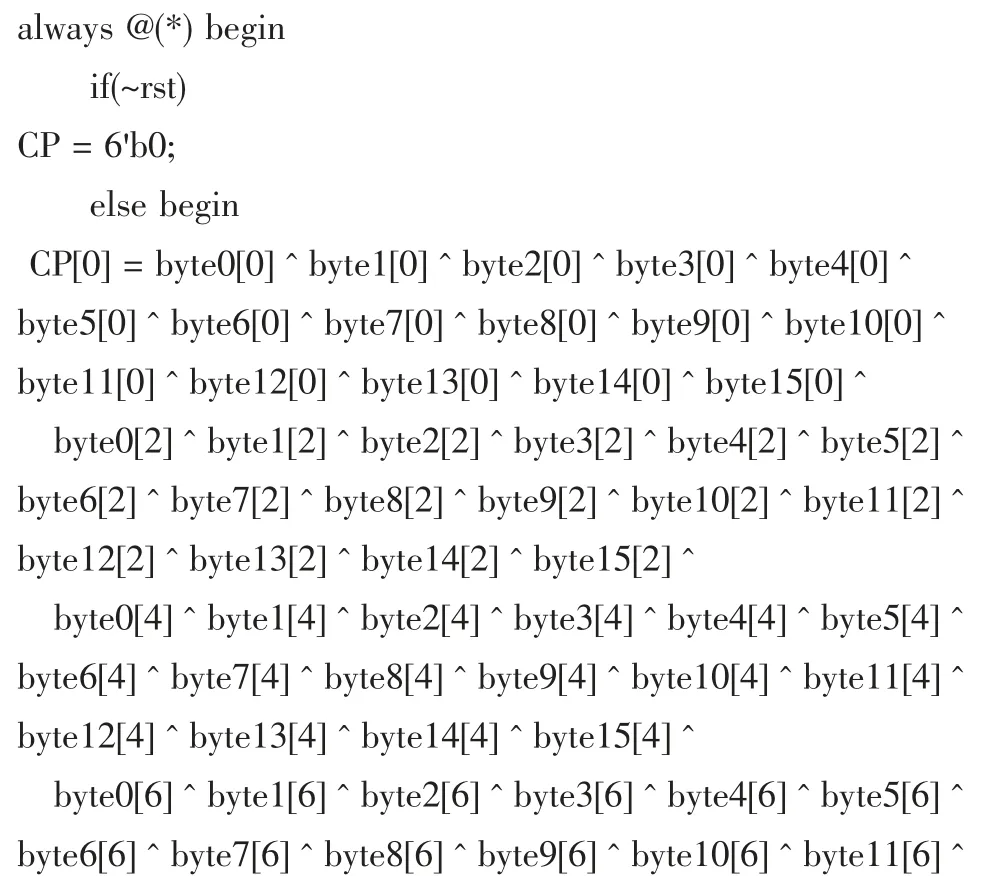

ECC 校验码设计便于实现。此处给出部分flash控制器ECC 模块的verilogHDL 的RTL 级实现。flash控制器的ECC 校验码计算模块设计采用分半异或,同时计算14 次,得出ECC 校验码。校验码计算过程如下述代码[3-8]:

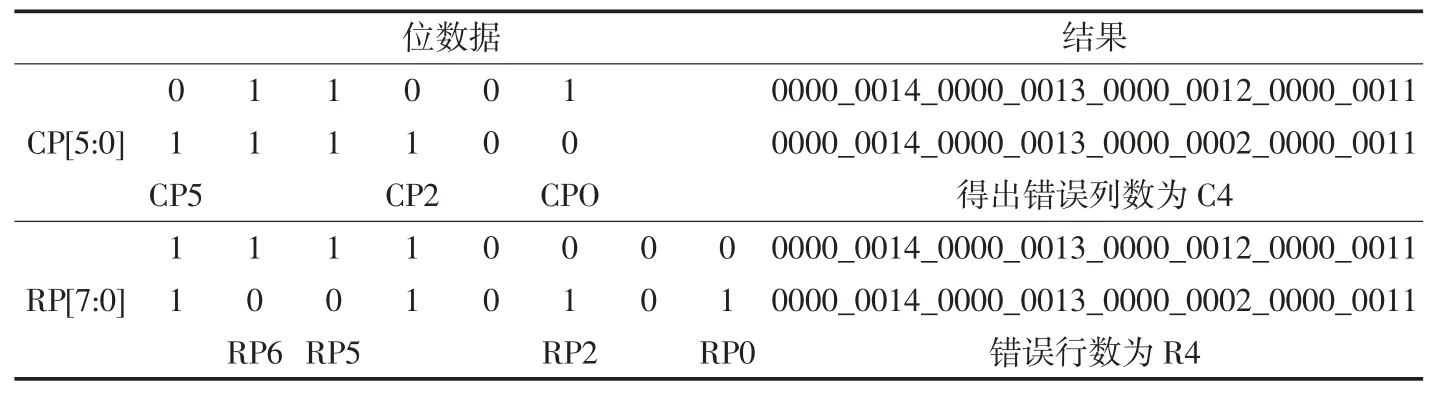

在ECC 纠正模块设计中校验码计算方法与校验码计算模块计算方法相同,增加了1 位错误纠正功能,其纠正原理如表2 所示(以正确数据为144'h9 995_0000_0014_0000_0013_0000_0012_0000_0011,错误数据为144'h9995_0000_0014_0000_0013_0000_0002_0000_0011 为例)。

表2 纠错原理表

对比表1 的ECC 校验码计算表,便可以清楚地看出错误位位数为bit36,将该错误位取反即可得出正确数据。

对于2 位及2 位以上错误,目前还没有方法进行纠正,但本设计可以检测大部分的数据错误情况并记录错误数据存放地址。

4 功能仿真

在ECC 模块设计完成后,将其与其他IP 进行整合,并挂接到Cortex-M4 为核心处理器的一款MCU 设计中,搭建仿真验证平台进行功能验证以及FPGA 验证。仿真结果如下:

(1) 写数据

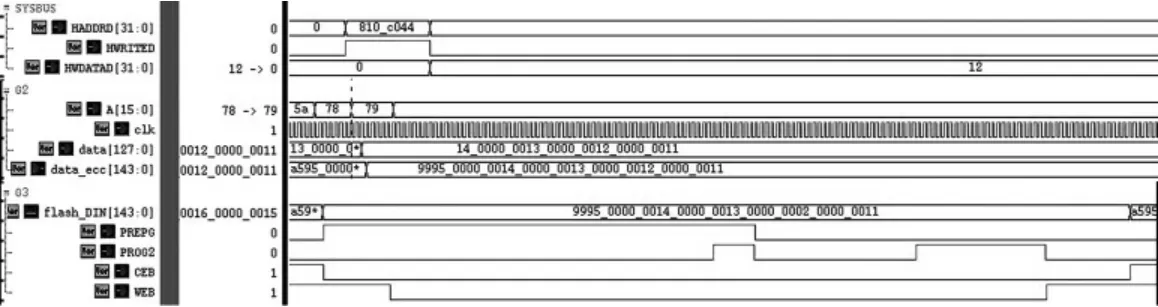

使用总线写flash,使能ECC,对flash 写操作进行功能仿真,仿真结果如图3 表示(以正确数据为144'h9995_0000_0014_0000_0013_0000_0012_0000_0011,错误数据为144'h9995_0000_0014_0000_001 3_0000_0002_0000_0011 为例)。

图3 校验码计算

(2) 读数据1 位错误

使用总线读flash,使能ECC,对读flash 模式进行功能仿真,强制翻转1 位数据,仿真结果如图4 表示(以正确数据为144'h9995_0000_0014_0000_0013_0000_0012_0000_0011,错误数据为144'h9995_000 0_0014_0000_0013_0000_0002_0000_0011 为例)。

图4 读数据1 位错误

在仿真中,强制将第36 位置0,使flash 输出结果错1 位。32'h810_c040~32'h810_c04C 地址为数据128'h 0000_0014_0000_0013_0000_0012_0000_0011地址,所以在系统总线中32'h810_c044 为32'h0000_0012 地址。

5 结束语

通过对设计的研究与分析,完成了基于144 位flash 的硬件ECC 设计,并将设计集成在flash 控制器中。设计采用VerilogHDL 硬件描述语言设计并实现了ECC 校验。该设计方法简单且易于实现,可1位错误检测纠正、2 位错误检测并记录错误地址。记录错误地址也可以避免其继续使用,在芯片实际应用时可以优化flash 坏区管理策略。