基于实验与仿真的SiC JFET单粒子效应研究

2023-12-26黎荣佳贾云鹏周新田胡冬青许明康马林东赵元富

黎荣佳,贾云鹏,*,周新田,胡冬青,吴 郁,唐 蕴,许明康,马林东,赵元富

(1.北京工业大学,北京 100124;2.上海精密计量测试研究所,上海 201109)

碳化硅(SiC)作为第3代半导体材料,具备宽禁带、高临界击穿电场、高饱和速度以及高热导率等优势[1-2]。随着制造工艺技术的发展,近年来SiC功率器件已经实现商用,在部分高压、高频与高温应用场景替代硅基器件[3-4]。SiC较高的禁带宽度使得SiC半导体在常温下本征载流子几乎为0,因此SiC材料非常适合制造高温耐辐射器件,具备潜在的空间宇航应用潜质[5-6]。然而,迄今为止SiC器件尚未在太空中使用,因为SiC器件易受单粒子效应(SEE)影响,单粒子漏电退化和单粒子烧毁(SEB)是器件在阻断态下受高能粒子辐照的2种失效模式[7-8]。据报道,商用SiC器件仅仅在其额定阻断电压的10%偏置电压下经历重离子辐照就可能会出现漏电流增大的变化,即单粒子漏电退化;在其额定阻断电压的50%偏置电压下经历重离子辐照就会表现出灾难性的损伤,即SEB[9-10]。

目前,针对SiC器件SEE的研究主要集中在SiC二极管和SiC MOSFET器件[11]。Abbate等[12]报道了SiC MOSFET的氧化层被重离子辐照损伤,导致氧化层形成电阻通路。Martinella等[13]、Zhou等[14]研究认为漏电退化起始阶段栅极氧化层首先中间区域损伤,随着漏极偏压增大栅极氧化层损伤扩散到沟道区域,导致漏极与源极短路,这被认为是SiC MOSFET单粒子漏电退化机制。

SiC器件SEB机制也一直存在争议。Witulski等[15]研究发现器件SEB阈值会随入射离子线性能量传输(LET)值的增加显著降低,并且与离子入射位置密切相关,认为是寄生晶体管(BJT)的导通形成正向反馈使电流增大导致器件烧毁。Ball等[16]、Mcpherson等[17]通过研究SiC二极管和MOSFET SEB的类似现象认为由于离子诱导的高局域态能量脉冲作用,外延与衬底界面处较大的电场显著增加了碰撞电离,导致了SiC二极管和MOSFET的SEB。

目前国内外对SiC JFET器件的SEE研究较少,Steffens等[18]对SiC JFET器件进行了重离子辐照实验,发现SiC JFET器件也具有SEE,但并未对机理进行分析。由于没有对辐射敏感的栅极氧化层结构,SiC JFET器件的抗辐射能力可能高于SiC MOSFET。本文对1 200 V SiC JFET器件在不同栅极偏置电压与不同漏极偏置电压条件下进行重离子辐照实验,观测SiC JFET器件的SEE失效模式,探究SiC JFET器件单粒子漏电退化和SEB的影响因素,结合Sentaurus TCAD仿真分析SiC JFET器件的SEE机理。

1 SiC JFET重离子辐照实验

实验样品选用UnitedSiC制造的商用1 200 V/70 mΩ常开型SiC JFET器件,型号为UJ3N120070K3S,封装为TO-247-3。实验前进行开帽处理,并去除芯片表面的防护胶,将芯片表面直接暴露于重离子束流下,减少重离子入射芯片敏感区域的能量损失,使重离子完全穿透芯片外延层。开帽后,使用半导体分析仪Agilent B1500和B1505测量器件的击穿电压BVDS、栅极漏电流IG、漏极漏电流ID和阈值电压VG(th)等参数,剔除开帽之后电参数异常的器件,器件电参数与样品实测值如表1所列。

表1 SiC JFET器件电参数与样品实测值Table 1 Electrical parameter and measured value of SiC JFET sample

重离子辐照实验在中国原子能科学研究院HI-13串列加速器上进行,离子束流窗口为3 cm×3 cm的方形窗口,所有实验均在真空、室温条件下进行,入射离子为74Ge20+,入射角度为90°垂直入射。根据解剖分析,此款器件的外延层厚度约为9 μm,再加上顶部金属化层和钝化层总厚度约10 μm,总的有源层厚度不超过20 μm,可以确定LET值为37.3 MeV/(mg/cm2)的74Ge20+离子能完全穿透外延层。重离子其余实验参数如表2所列。

表2 重离子实验参数Table 2 Heavy-ion experimental parameter

SiC JFET样品需要施加一个负栅压,以保持器件处于阻断状态,使用吉时利2400源表给栅极与源极加偏置电压,同时记录栅极与源极的泄漏电流,使用吉时利2410源表给漏极与源极加偏置电压,同时记录漏极与源极的泄漏电流。实验电路原理图与实验电路板照片如图1所示。在不同栅极偏置电压(VGS)与不同漏极偏置电压(VDS)状态下进行重离子辐照实验,研究辐照损伤对VGS与VDS的依赖关系。将8个样品分为两组实验,#1和#2进行不同VGS下的VDS爬坡实验,#3~#8进行不同VGS下的固定VDS实验。

a——实验电路原理图;b——实验电路板图1 实验电路原理图与实验电路板Fig.1 Experimental circuit schematic and circuit board

1.1 不同栅极偏置电压下漏极偏置电压爬坡实验

选取样品#1、#2,分别对#1与#2施加-20 V(器件规格书推荐使用的VGS)与-14 V(器件阻断时的最小VGS)VGS,之后施加80 VVDS,进行重离子辐照实验,每当辐照注量达到3×105cm-2时,VDS增加1个电压等级,当VDS小于200 V时,每次增加20 V;当VDS大于等于200 V时,每次增加50 V,持续实验,直至器件发生烧毁。实验结果如图2所示。图2显示了SiC JFET器件在重离子辐照期间源表记录的ID与IG随时间的演变,可以看出在VDS较低(VDS≤300 V)时,器件的ID和IG均基本稳定,没有明显增加。说明SiC JFET器件此时还未发生单粒子漏电退化。而当VDS增加到350 V时,可以观察到ID和IG同时增加,且增加的速率大致相同,可以说明器件漏极与栅极之间形成了泄漏电流路径,SiC JFET器件在350 VVDS下发生了单粒子漏电退化。VDS进一步增加到400 V时,器件的ID与IG直接达到源表设置的限制电流10 mA,SiC JFET器件发生了SEB。

VGS:a——-20 V;b——-14 V图2 辐照期间ID与IG随时间的演变Fig.2 Evolution of ID and IG with time during irradiation

1.2 不同栅极偏置电压下固定漏极偏置电压实验

选取样品#3~#8,对样品#3、#5和#7施加-20 VVGS,对样品#4、#6和#8施加-14 VVGS,之后分别对样品#3和#4施加300 VVDS,对样品#5和#6施加350 VVDS,对样品#7和#8施加400 VVDS,进行重离子辐照实验,辐照注量为1×106cm-2。实验结果如图3~5所示。

图3 VDS为300 V时ID与IG随重离子注量的演变Fig.3 Evolution of ID and IG with heavy-ion fluence at VDS 300 V

图3分别显示了#3和#4 SiC JFET器件在VGS为-20 V和-14 V、VDS为300 V时重离子辐照期间源表记录的ID与IG随重离子注量的演变。从图3可看出,在300 VVDS下,样品#3的IG大于样品#4,但2个器件在重离子辐照过程中的ID与IG均基本稳定,没有明显增加,说明器件漏极与栅极之间没有形成泄漏电流路径,SiC JFET器件未发生单粒子漏电退化。

图4分别显示了#5和#6 SiC JFET器件在VGS为-20 V和-14 V、VDS为350 V时重离子辐照期间源表记录的ID与IG随重离子注量的演变。从图4可看出,在350 VVDS下,#5和#6两个器件在重离子辐照过程中的ID与IG均随重离子注量增加而同步上升,且ID与IG上升趋势一致,说明器件漏极与栅极之间形成了泄漏电流路径,SiC JFET器件发生了单粒子漏电退化。对比图4中#5和#6器件的漏电退化现象,在重离子辐照注量达到1×106cm-2时,#5器件的漏电流达到了13.8 μA,而#6器件的漏电流为4.3 μA,且可以观察到#5器件漏电流随重离子注量上升的斜率明显大于#6器件。

图4 VDS为350 V时ID与IG随重离子注量的演变Fig.4 Evolution of ID and IG with heavy-ion fluence at VDS 350 V

图5分别显示了#7和#8 SiC JFET器件在VGS为-20 V和-14 V、VDS为400 V时重离子辐照期间源表记录的ID与IG随重离子注量的演变。从图5可看出,在400 VVDS下,#7和#8两个器件在重离子入射后ID与IG瞬间达到源表设置的限制电流,漏极限制电流ID为10 mA,栅极限制电流IG为1 mA,SiC JFET器件发生了灾难性的SEB。

图5 VDS为400 V时ID与IG随重离子注量的演变Fig.5 Evolution ID and IG with heavy-ion fluence at VDS 400 V

重离子辐照实验可以得出,SiC JFET器件SEE与SiC MOSFET类似,存在单粒子漏电退化和SEB 2种失效模式。SiC JFET器件单粒子漏电退化与VDS有关,VDS较低时(≤300 V时),不会发生单粒子漏电退化;当VDS较高时(≥350 V),器件发生单粒子漏电退化现象。VGS几乎不影响器件的单粒子漏电退化起始点,但VGS绝对值越大,单粒子漏电退化时的漏电流越大,漏电退化现象越严重。器件单粒子漏电退化与重离子注量有关,发生单粒子漏电退化时,随着重离子注量的增加,器件的漏电流呈线性上升趋势,重离子注量对于单粒子漏电退化具有累积效应。当VDS≥400 V时,器件瞬间发生灾难性的SEB。VGS与重离子注量几乎不影响器件的SEB阈值电压。

2 SiC JFET单粒子效应机理

SiC JFET器件单粒子漏电退化现象与SiC MOSFET存在差异,SiC JFET器件的单粒子漏电退化起始点高于SiC MOSFET。在VDS较低时(约为180 V),SiC MOSFET的栅极氧化层损伤导致漏电退化现象,而SiC JFET器件由于没有栅极氧化层,因此在较低电压下不存在漏电退化现象。而当VDS增大到350 V时,器件栅极与漏极之间出现了漏电流路径。SiC JFET器件在阻断态工作时,需要在器件的栅极施加一个负的偏置电压,使P+栅极区与N-漂移区PN结反偏,耗尽层向N-漂移区展宽,两个栅极之间的漂移区被完全耗尽。文献[19-20]指出SiC MOSFET 在VDS较高时出现的漏极到源极的漏电流路径是体二极管PN结微损伤的结果,SiC JFET器件的栅极与漏极之间的PN结情况类似,如果P+栅极区与N-漂移区的PN结出现了微损伤,那么栅极与漏极之间就会形成漏电流路径,但两个栅极之间仍然处于相互耗尽的状态,所以漏极与源极之间没有形成漏电流路径。并且当栅极负偏压增大时,P+栅极区与N-漂移区的PN结处的电场会更强,PN结微损伤可能更加恶劣,漏电退化现象更为严重。

SiC JFET器件SEB阈值电压则与SiC MOSFET的基本一致,推测二者存在共同的烧毁机理,SiC MOSFET SEB的机制目前有2种观点:1) SiC MOSFET SEB是由于寄生BJT导通,ID持续增大,最终器件烧毁;2) SiC MOSFET SEB与寄生BJT没有关系,而是重离子辐照时的局部高温造成的。

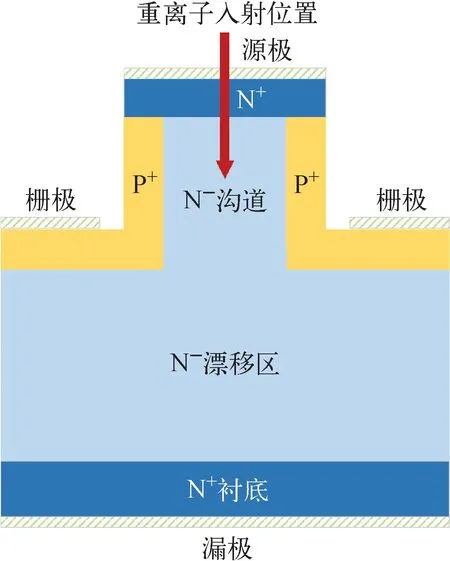

为了进一步研究SiC JFET器件SEB的机理,使用Sentaurus TCAD软件对器件进行SEE仿真,分析重离子辐照时器件内部电场、碰撞电离、电流以及晶格温度等参数的变化。SiC JFET器件仿真结构如图6所示,器件仿真元胞参数如表3所列。

图6 SiC JFET器件仿真结构示意图Fig.6 Simulation structure schematic of SiC JFET

实验中单粒子LET值为37.3 MeV(mg/cm2),换算到仿真设置中单粒子LET值约为0.25 pC/μm,单粒子入射位置为元胞中心,单粒子入射深度为20 μm。分别设置VGS为-20、-14 V,使SiC JFET器件处于阻断态,分别设置VDS为100、200、300和400 V进行单粒子仿真。图7为单粒子辐照之后器件内部最高晶格温度随VDS的变化。仿真结果表明:随着VDS的增大,SiC JFET器件内部最高晶格温度上升,当VDS达到400 V时,内部最高晶格温度超过3 000 K,超过SiC材料的升华温度,器件发生SEB。当VDS一定时,VGS绝对值越大,器件内部最高晶格温度越高,但差异仅为数十K,对SiC JFET器件的SEB阈值电压影响较小。

图7 SiC JFET器件内部最高晶格温度随VDS的变化Fig.7 Evolution of maximum internal lattice temperature with VDS in SiC JFET

为了探究SiC JFET器件SEB时BJT是否导通,提取VDS为400 V时单粒子入射之后内部最高晶格温度随时间的变化曲线与ID随时间的变化曲线,如图8所示。可以看出ID在7 ps左右达到第1个峰值,在1 ns左右达到最大值,随后快速减小,在6 ns左右恢复至较低值,若是寄生BJT导通,ID将持续增加或维持在较高值。而最高晶格温度较电流延时上升,在1 ns左右达到第1个平台,大约为2 700 K,持续一段时间之后,在80 ns开始继续上升,随即在100 ns超过3 000 K,导致器件烧毁,可以看出器件烧毁时,ID已经恢复至较低值,说明器件烧毁是由单粒子辐照产生的高温导致的。

图8 VDS为400 V时最高晶格温度与ID随时间的变化Fig.8 Evolution of maximum lattice temperature and ID with time at VDS 400 V

为了确定器件内部高温产生的原因和烧毁的位置,提取VDS为400 V时器件内部不同时刻的晶格温度和电场强度分布,如图9、10所示。单粒子辐照之后,单粒子辐照路径发生碰撞电离,N+衬底和N-漂移区结处的电场强度开始升高,在100 ps时达到第1个高峰,N+衬底和N-漂移区结处产生一个明显热点,在VDS为400 V下,随着电场的调制作用,N+衬底和N-漂移区结处的电场强度先降低后升高,在10 ns左右达到最大电场3.2 MV/m左右,且大电场持续时间足够长,引起显著的碰撞电离。碰撞电离产生的局部高密度电流导致温度持续增加,到100 ns左右N+衬底和N-漂移区结处局部温度超过3 000 K,超过SiC材料的升华温度。在Sentaurus TCAD仿真中SiC材料不会发生升华,然而在实验中,此时SiC材料升华,导致SiC JFET器件物理结构被破坏,发生烧毁短路现象。

图9 VDS为400 V时晶格温度随时间的变化Fig.9 Evolution of lattice temperature with time at VDS 400 V

图10 VDS为400 V时电场强度随时间的变化Fig.10 Evolution of electric field strength with time at VDS 400 V

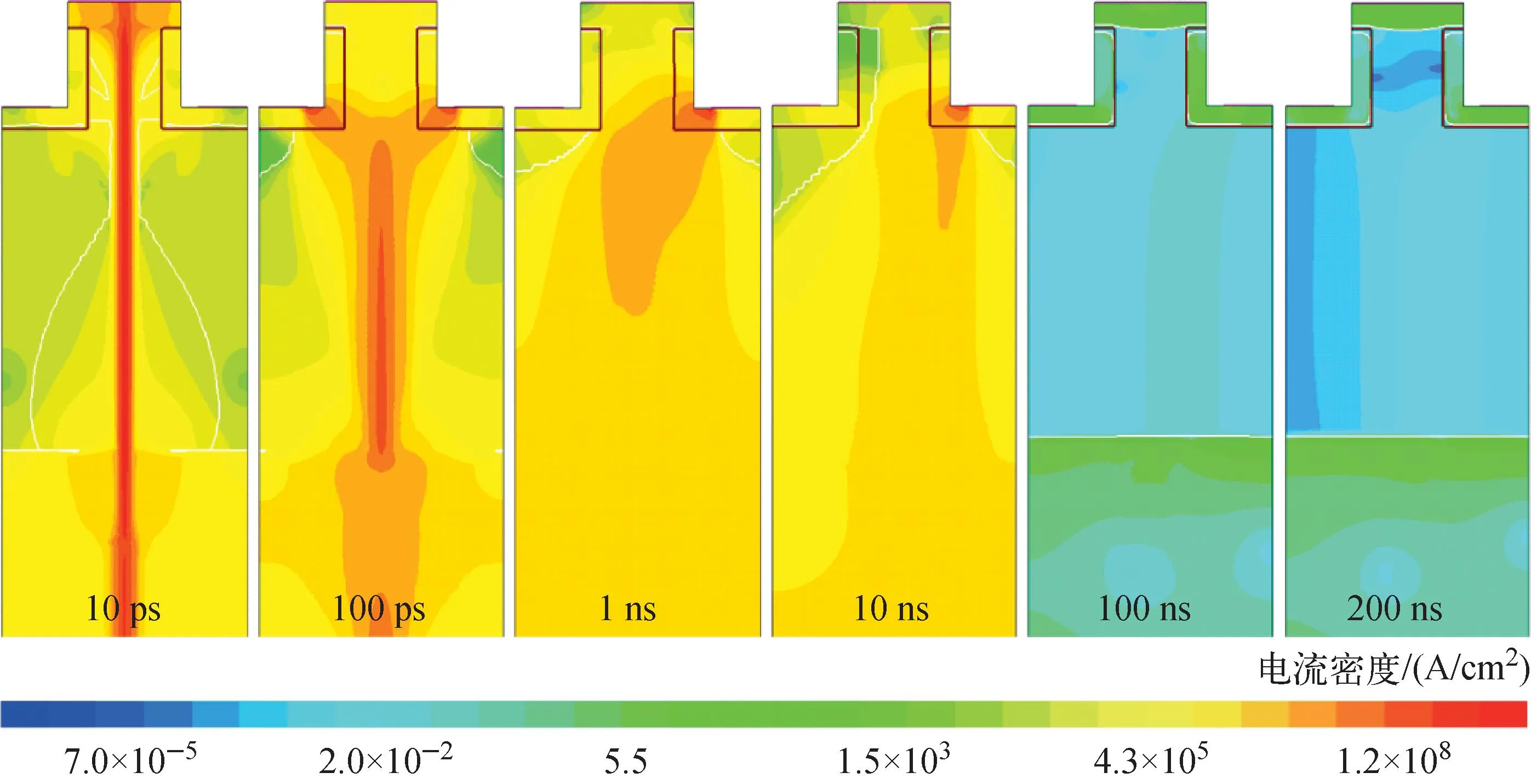

除此之外,器件2个P+栅极区与N-漂移区的PN结处也出现明显热点,但最终温度为2 500 K左右。提取VDS为350 V时器件内部不同时刻的晶格温度和电流密度分布,如图11、12所示。在350 VVDS下,器件内部最高晶格温度在P+栅极区与N-漂移区的PN结处,最高温度为2 500 K左右,而器件N+衬底和N-漂移区结处最高晶格温度为1 700 K,此时器件未烧毁。

图11 VDS为350 V时晶格温度随时间的变化Fig.11 Evolution of lattice temperature with time at VDS 350 V

图12 VDS为350 V时电流密度随时间的变化Fig.12 Evolution of current density with time at VDS 350 V

而P+栅极区与N-漂移区的PN结正是第2节分析的SiC JFET器件单粒子漏电退化的位置。结合仿真器件内部电场强度与电流密度分析,发现单粒子入射之后分为2个阶段,第1阶段为单粒子辐照引起的碰撞电离效应,产生大量的电子-空穴对,在VDS与VGS的作用下,电子向漏极移动,空穴向栅极移动,从漏极到栅极的高密度电流使得栅极边角处局部晶格温度升高,在VDS为350 V时能达到2 500 K,但这个温度下降较快,短暂的局部热应力可能使P+栅极区与N-漂移区的PN结存在潜在损伤,造成漏电退化。第2阶段载流子的运动使得电场调制,N+衬底和N-漂移区结处的电场强度开始增加,最大电场强度能达到3.2 MV/m以上,在VDS为350 V时,电场持续时间较短,在数十ns电场恢复;在VDS为400 V时,电场持续时间长,一直持续到200 ns,足够引起显著的碰撞电离,碰撞电离产生的局部高密度电流导致温度持续增加,直至超过3 000 K导致SiC JFET器件烧毁。

3 结论

本文对SiC JFET器件SEE进行研究。针对SiC JFET在重离子辐照条件下出现的单粒子漏电退化和SEB现象进行了失效机理分析,主要结论如下。

1) 重离子辐照实验结果表明,当漏极偏置电压在300 V及以下时,重离子辐照不会造成损伤;当漏极偏置电压增加到350 V时,辐照过程中重离子辐照造成了漏极到栅极的漏电流路径,出现了漏电退化现象。漏电退化与离子注量呈正相关,同时栅极负偏压的大小对单粒子漏电退化的程度也存在一定影响。结合Sentaurus TCAD仿真研究,发现局部热应力使P+栅极区与N-漂移区的PN结存在潜在损伤,可能是造成漏电退化的原因。JFET由于没有MOSFET中脆弱的栅极氧化层结构,SiC JFET器件的漏电退化起始点远高于MOSFET器件,意味着SiC JFET器件的安全工作区更高,有着更好的空间应用前景。

2) 当漏极偏置电压达到400 V时,辐照过程中重离子辐照使器件瞬间烧毁失效,发生了SEB。Sentaurus TCAD仿真结果表明,由重离子辐照产生的载流子在N+衬底和N-漂移区结处产生局部强电场。强电场存在的时间足够长,碰撞电离产生大量的电子-空穴对,形成局部高密度电流,使N+衬底和N-漂移区结处局部晶格温度迅速上升,超过SiC材料的升华温度,导致器件烧毁。在N+衬底和N-漂移区结处增加缓冲层可能提高器件的SEB阈值电压。