基于ZYNQ-7000与ADS125H02的高精度模数转换设计

2023-11-21邓肖丹李学砚段乐颖李行素

邓肖丹,李学砚,段乐颖,李行素

(1.自然资源部航空地球物理与遥感地质重点实验室,北京 100083;2.中国自然资源航空物探遥感中心,北京 100083)

自然界中大部分信号均为模拟信号[1]。模数转换(ADC)将连续变换的模拟信号转换为离散的数字信号[2],提取出有用信号,广泛应用在导航、监控、触控以及人工智能等系统中[3-5]。

基于ARM 内核的微处理以及近些年发展迅速的FPGA(现场可编程逻辑门阵列)芯片几乎都内置有模数转换部分,其中FPGA 没有指令周期,易于时序控制,具有特有的并行处理能力、强大的处理速度以及丰富的外设接口[6-8],但都受限于芯片本身的电压范围以及转换精度等因素,在许多应用中仍然需要使用单独的模数转换芯片[9-11];传统的模数转换芯片通过单片机进行直接控制,但受限于运算能力与硬件接口资源,会制约数据采集的速度与同步性[12];模数转换芯片有积分型、逐次比较型、流水线型以及Δ-Σ型等类型,每种对应不同的应用需求,Δ-Σ型适应于分辨率在20 位以上的高精度测量领域[13-14]。针对以上问题,该文基于ZYNQ-7000 的FPGA 微控制器,利用近两年TI 公司新上市的24 位Δ-Σ型模数转换芯片ADS125H02 设计高精度的数模转换。

1 总体设计

系统以ZYNQ-7000 系列中XC7Z020-2CLG484I作为微控制器的核心开发板,集成了双核ARM Cortex-A9 处理系统(Processing System,PS)与可编程逻辑(Programmable Logic,PL)系统[15],灵活性更高、可配置性更高、功耗更低、运行效率更高[16-17]。相较于自主研制微控制器核心板,使用当前技术成熟的开发板免去了对其外围基础电路的设计,减少了设计周期。硬件部分还包括模数转换电路、串口通信与电源电路。

电源模块为核心板、AD 芯片以及串口提供±5 V、+3.3 V 的电源电压。模数转换芯片与ZYNQ-7000核心板通过PL 端配置的SPI 接口进行双向通信,核心板通过在PL 端配置的UART 串行接口向PC 机发送数据。系统硬件模块连接框图如图1 所示。

2 核心电路设计

ADS125H02 可实现±20 V 双通道模拟电压输入,内部具有低噪声0.125~128 的可编程增益放大器(PGA),40 kSps 转换速率,具有内部基准电压源。内置的PGA 可根据输入模拟电压范围灵活调节增益放大器倍数,以对应内部基准电压源的幅值进行模数转换,可有效减少电路板面积,消除了对外部衰减器或外部增益的需要,降低了电路噪声,有利于高精度、小型化设计[18]。ADS125H02 共有32 个管脚,其中主要管脚功能如表1 所示。

表1 ADS125H02管脚功能

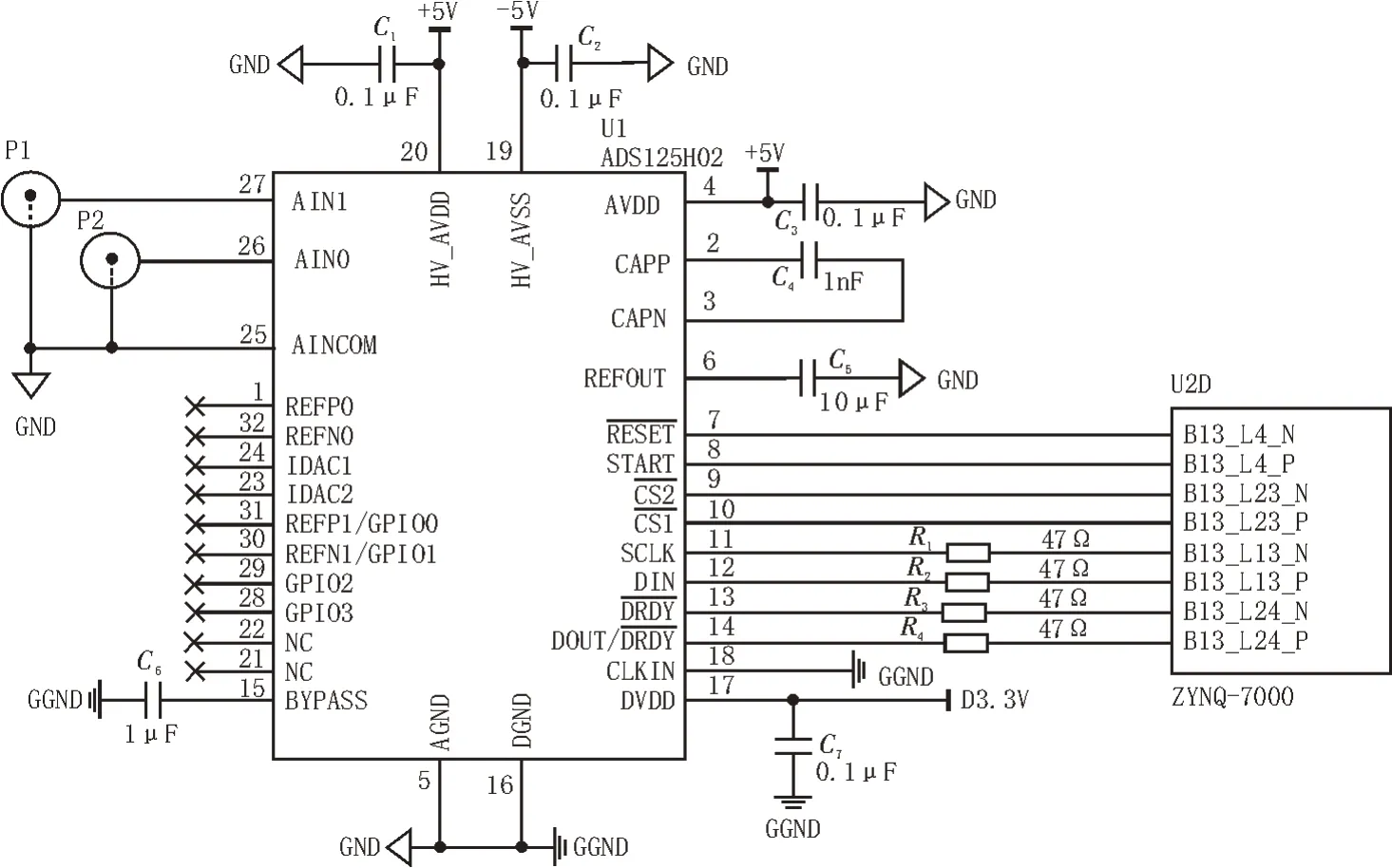

AD 转换电路作为系统的核心部分,根据芯片管脚功能与需求来设计电路。ADS125H02 只能采用串行外设接口(Serial Peripheral Interface,SPI)与ZYNQ-7000 进行通信,传统方式是在ZYNQ-7000 的PS 端使用内置的SPI 接口进行通信,可降低程序设计难度,但时速以及挂载数量受到限制,而在未植入操作系统的情况下,也无法实现数据的同步采集与转换,不利于将来多路实时AD 转换的扩展,利用在PL 端配置SPI 接口进行通信可有效克服这些弊端。AD 转换电路如图2 所示。

图2 AD转换电路

电路中两路单端输入范围根据HV_AVDD 与HV_AVSS 将输入电压控制在-5.3~+5.3 V 范围内,数字部分采用单电源+3.3 V 供电,模拟部分采用±5 V双极性供电,在电源附近使用0.1 μF 的去耦电容进行滤波,降低电源噪声,模拟地GND 与数字地GGND单点连接,抑制环路噪声,REFOUT 与BYPASS 可分别输出+2.5 V 与+2.0 V 的内部电压,在设计中不使用,直接连接电容接地,P1 与P2 外接两路模拟输入电压。

3 程序设计

系统以ZYNQ-7000 作为核心处理器,通过SPI与ADS125H02 进行通信,实时控制数据的采集转换,灵活调节寄存器参数,将接收到的二进制数值进行提取与处理,得到带符号的模拟电压值,由串口发送至上位机中,实现高精度的模数转换[19-20]。

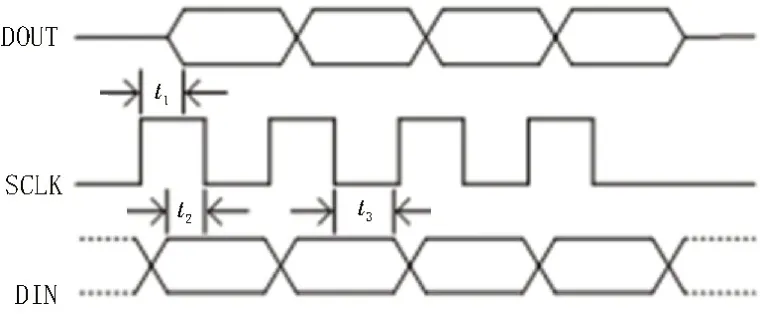

ADS125H02 作为SPI 通信的从设备,需要主设备提供时钟信号。串行通信的时序如图3 所示,t1表示时钟触发上升沿到输出有效数据的时间,为了正确地发送数据,t1的值在15~40 ns 之间;t2表示时钟触发下降沿前读取数据的启动时间,t3表示时钟触发下降沿后读取数据的保持时间,为了正确地读取数据,t2与t3之间最少需要保持25 ns。根据要求,以ZYNQ-7000 的50 MHz 晶振为时钟基准,通过软件处理获得7.14 MHz 的SCLK 时钟信号。特别注意的是,ZYNQ-7000 在时钟信号触发的同时读取/发送数据,但ADS125H02 需要在一定延时后才发送正确数据,因此,ZYNQ-7000 读取ADS12H02 发送的数据时应延迟一个时钟周期。

图3 串行通信时序图

软件设计基于ZYNQ-7000 的PL 端进行。在数据转换之前先对ADS125H02 的内部寄存器进行配置:先发送寄存器地址数据再发送寄存器配置数据,包括转换速率、参考电压、增益放大器倍数以及转换通道等。设计中有两路数据进行轮流转换,每次需重新开启转换配置,无论是对寄存器的操作还是数据转换读取都需要进行CRC 校验,校验通过则表明ADC 芯片正确实现了读写寄存器以及数据转换,否则需要重新进行操作。ZYNQ-7000 收到的数字信号为24 位二进制数,通过软件进行计算处理。Wait 控制两通道转换速度,在PL 端配置的串口输出带符号的模拟电压值,电压值保留到小数点后六位,小数点前一位,共七位。程序编写要严格按照器件的工作时序进行,程序设计流程图如图4所示。

图4 程序设计流程图

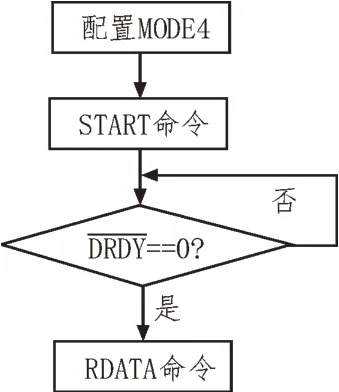

在程序设计中,CH0 与CH1 两通道数据的每一次交替转换,都需重新配置寄存器MODE4,MODE4寄存器的值决定了当前的转换通道。转换数据的开启可使用硬件控制也可使用软件控制,系统选择通过START 命令,利用软件方式开启转换,再读取DRDY 管脚的电平信息,为低电平则表示新的数据转换完成,可以利用RDATA 命令进行数据读取,否则继续等待,直到DRDY 管脚为低电平。数据转换流程图如图5 所示。

图5 数据转换流程图

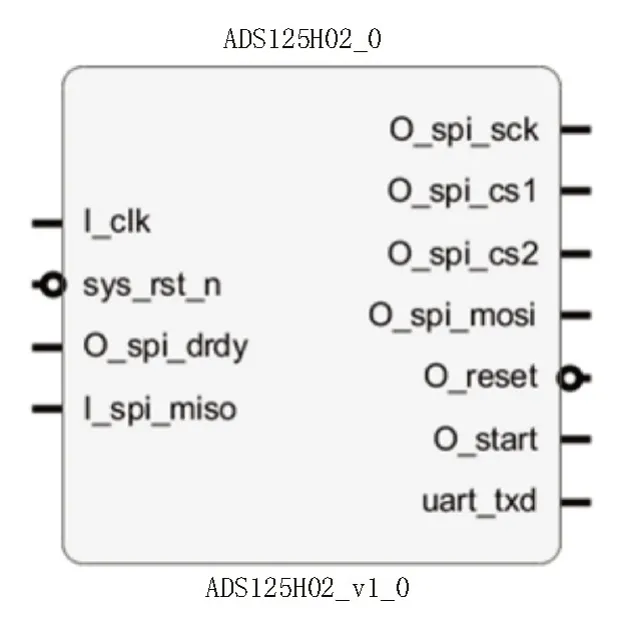

将完成的程序代码打包成IP 核,如图6 所示,便于以后移植调用,根据管脚对应的输入输出,可同时挂载多个AD 转换芯片,实现同步数据采集。

图6 ADS125H02 IP核

4 仿真结果与分析

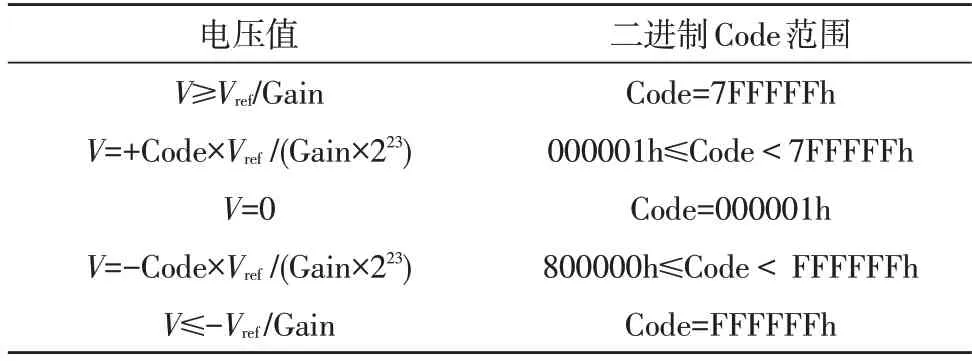

利用软件的仿真功能对程序中的部分算法进行仿真测试,确保接收到的二进制数可以准确无误地转换为十进制电压值,验证了结果的真实性。在程序中,ZYNQ-7000 收到ADS125H02 经过模数转换后的24 位二进制数据,按照芯片数据说明,通过算法将二进制数转换为有符号的10 进制数。二进制值Code 与电压值的对应公式如表2 所示,Vref是基准电压值,系统中为2.5 V,增益Gain 为0.5。

表2 模拟电压与24位二进制对应关系

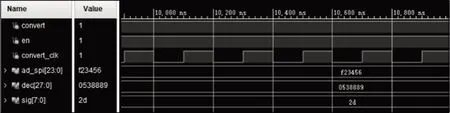

根据上述关系,在仿真程序中进行检验时,随意对24 位二进制数值进行设置。取其中值为0xF23456,根据计算可知对应的幅值应为-0.538 889 170 V,仿真结果如图7 所示,从图中可以看出,此时符号位的ASCII 码值为2d,对应为“-”,数值为0538889,在输出中小数点位数为六位,对应的电压值为0.538 889 V,仿真结果验证正确。

图7 仿真结果图

5 测试结果分析

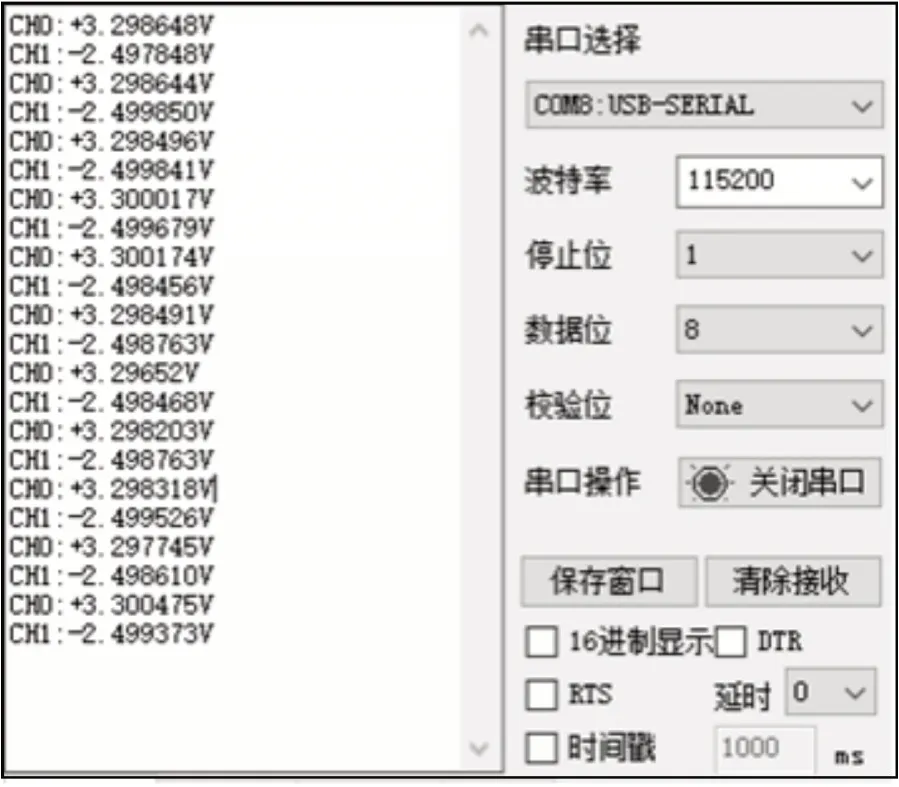

对系统进行上电测试,通过串口将输入模拟信号转换的电压值发送到上位机进行观测。将ADS125H02其中的两通道模拟输入连接幅值为+3.3 V和-2.5 V进行测试,通过数据处理,上位机软件接收数据,测试结果如图8 所示。从图中可看出,两通道数据轮流进行采集,输出带符号的7位电压值,分辨为1 μV。

图8 测试结果

6 结论

该文利用基于ZYNQ-7000 的可编程逻辑端与ADS125H02 实现了24 位、±5 V 的低噪声高精度数模转换,并验证了数据转换的正确性。基于ZYNQ-7000 核心处理器丰富的外设接口,高速的处理速度和同步性,可扩展多个AD 同时进行数据转换;ADS125H02 双极性的宽电压转换范围,集成的内部基准源、低噪声增益放大器与数字滤波,高达24 位的转换精度,使其在要求高精度、同步性、小型化等系统中具有良好的应用和前景。