可编程交流电压比率标准的研究

2023-11-02张书哲李瑞霖迟宗涛

张书哲, 李瑞霖, 陆 青, 迟宗涛, 杨 雁

(1.青岛大学电子信息学院,山东青岛266071; 2.中国计量科学研究院,北京100029;3.国家市场监督管理总局重点实验室(电学量子基准),北京100029)

1 引 言

电磁学单位量值复现与传递是电磁计量的重要研究内容,精准的电压比率技术是电磁单位复现水平的重要保证。推动电磁计量技术进步的一方面取决于实物、自然计量标准取得技术突破;另一方面取决于研究实现更高精度或便捷通用的比率技术,实现量值更加精准和快速的传递[1,2]。交流比率标准主要用于交流电量和阻抗量值的传递,研究可编程交流电压比率技术对交流参量计量技术的自动化具有重要意义。

构建交流电压比率的方法除了传统的交流电阻分压法外,主要有基于磁感应耦合原理的感应分压器[3](inductive voltage divider, IVD)、数模转换器(DAC)分压网络法[4]、可编程约瑟夫森电压(PJVS)比率标准[1]等。

近代交流电压比率技术的发展起源于计算电容技术的研究。上世纪60年代,为了提高阻抗单位复现精度,研究人员提出了计算电容原理以及基于端对定义[5]的阻抗电桥和基于感应分压器的交流比率技术。感应分压器(IVD)是由1个或多个相互连接的多抽头磁芯线圈形成的分压器,它通过绕组自身的匝比来获取精确比率的电压[6]。IVD应用于交流电桥后[7~9],成功将阻抗单位的复现精度优化了近2个数量级,达到10-8量级。但受限于单盘感应分压器匝比关系,交流电压比率输出被限制在几个固定值。而使用拨盘开关切换比率的多盘感应分压器体积较大,调节比率时需手动切换每一位的开关,在应用中操作繁琐,难以实现自动化测量。

为实现可编程交流电压比率标准,研究人员提出了基于可编程感应分压器[10](programmable IVD, PIVD)的交流电压比率方案。加拿大国家研究委员会(NRC)的Tsao S H使用CMOS开关实现了12位分辨率的PIVD[11],在10~80 Hz频率范围内的交流电压比率精度达10-7量级;但其输入额定电压仅为8Vrms(Vrms为交流电压有效值,指交流电压的均方根值),并且覆盖频率范围窄,且工作时CMOS开关引入较大的导通电阻(100 Ω)。德国联邦物理技术研究院(PTB)研制了便于计算机控制的24位2进制PIVD[12],其工作频率范围为50 Hz~5 kHz,在400 Hz频率下精度达到了10-7量级,后续又研制了工作在100 Hz~10 kHz频率范围内的PIVD[13],但仅在1 kHz频率下的精度达10-6量级。

研究人员也尝试采用高分辨率的DAC或ADC构建的数字交流电压比率技术[3],实现覆盖整个复数平面的电压比率及测量自动化[14~16]。此类数字交流电压比率的输出比率最佳精度能达到10-6量级,受限于分压网络的电阻电容元件的寄生参数影响,在宽频应用下比率精度下降明显。而基于PJVS的量子交流电压比率技术[1]比率精度虽然可达10-8量级,但其系统庞大、成本昂贵、操作较为复杂,一般只用于科研领域或计量基准配套使用。

目前PIVD和数字交流电压比率方案仅在较低频段或个别频率点下达到10-6或10-7交流分压精度,精准的交流比率尚无法覆盖较宽频段,无法满足宽频阻抗自动化计量的需求。本文提出了1种采用基于双级感应分压器的PIVD和基于乘法型数模转换器(multiplying digital-to-analog converter, mDAC)组合分压的宽频可编程交流电压比率标准设计方案,采用自锁型继电器实现双级感应分压器的可编程控制,提出的mDAC宽频比率分压误差修正方法将比率标准分压精度优化了1个量级,设计并实现了1种交流电压精密比较测量系统进行实验验证,在50 Hz~10 kHz频率范围内实现了10-7量级的高精度的可编程交流电压比率标准。

2 交流电压比率标准的原理

2.1 交流电压比率标准的架构

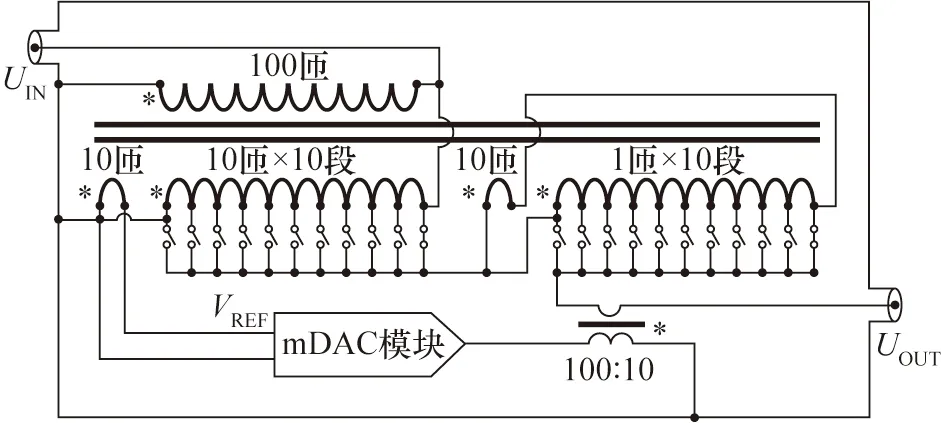

可编程交流电压比率标准目标为实现分辨率优于1 μV/V(6位小数)的任意比率精准分压。其中交流电压比率的高两位决定了其整体分压精度,因此采用高精度的双级感应分压器[17]作为高位分压器,并进行可编程设计。可编程交流电压比率标准低位分压采用mDAC模块实现,并通过注入电压法将PIVD和mDAC分压模块组合分压,从而实现交流电压比率的输出。图1为可编程交流电压比率标准的原理框图。

图1 可编程交流电压比率标准原理图Fig.1 Schematic diagram of AC voltage ratio standard

交流电压比率标准的传递比率误差(简称比率误差)定义[18]为

(1)

式中:e为传递比率误差;UOP为比率标准开路输出电压的标称值;UOUT为比率标准的实际开路输出电压;UIN为比率标准的输入电压。

交流比率标准的传递比率误差实际是包含同相分量和正交分量的复数量。传递比率误差的同相分量也称比差,传递比率误差的正交分量也称角差。

mDAC可利用交流电压作为参考电压VREF,利用芯片内部电阻分压网络通过设置数模转换值实现交流分压。因其设计输入参考电压上限为10Vrms并且VREF=0.1UIN,故设计比率标准的最大输入电压为100Vrms。低位分压器采用16位mDAC分压,其输出电压通过100:10的微差电势注入变压器叠加到可编程双级感应分压器的输出,从而实现与高位的双级感应分压器组合分压输出,理论上电压比率输出分辨率可以达到1/6 553 500。

比率标准的输出电压为

UOUT=(KI+0.01KM)UIN

(2)

式中:KI为双级感应分压器的分压比率,KI=n/100,n∈Z[0,100];KM为mDAC模块的分压比率,KM=N/65 535,N∈Z[0,65 535]。以输出比率0.123 456为例,则KI=0.12,KM=0.345 6。

2.2 双级感应分压器的原理

感应分压器具有高输入阻抗、低输出阻抗、高精度和高稳定性的特点,常用做高稳定性的精密电压比率参考标准。传统的感应分压器因绕线电阻、分布电容(在高频下尤为敏感)以及等效漏感的影响,不可避免存在泄漏阻抗。当激磁电流流过时,会产生一定的压降,从而引入分压误差。其分压精度一般能达到10-5~10-6量级。双级感应分压器[4]利用前馈原理,通过在第二级比率绕组上预置一个与输入UIN近似的电压,从而极大降低第二级比率绕组上的激磁电流,提高感应分压器的精度和工作频率范围。

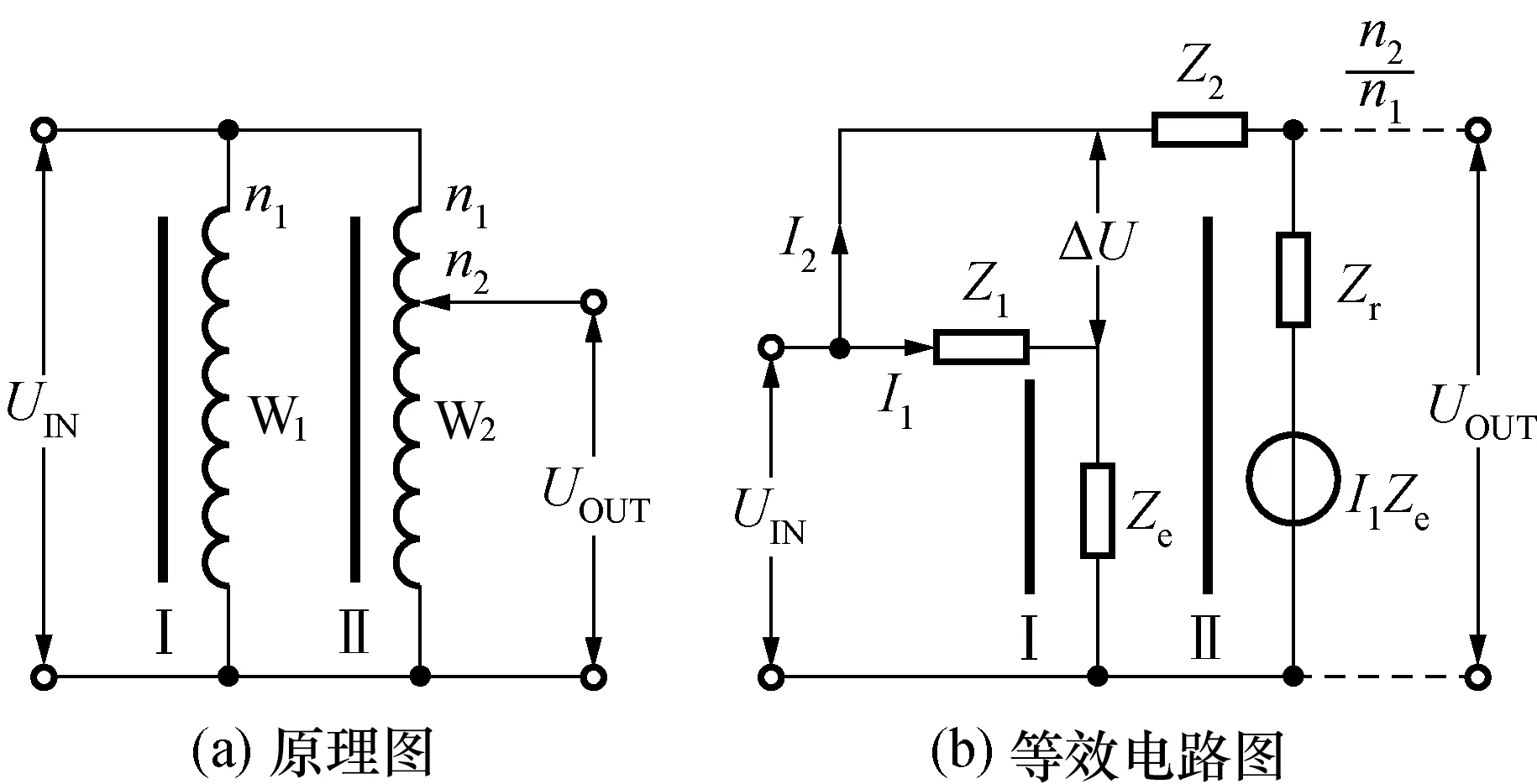

图2(a)为双级感应分压器原理图,激磁绕组W1绕在主铁芯Ⅰ上,比率绕组W2绕在主铁芯Ⅰ和辅助铁芯Ⅱ上,匝数均为n1,分压输出对应的匝数为n2。图2(b)为其等效电路图, 其中Z1、Z2分别为绕组W1、W2的漏阻抗,Ze、Zr为主铁芯和辅助铁芯的激磁阻抗。

图2 双级感应分压器原理图Fig.2 Schematic diagram of two-stage IVD

对于激磁绕组W1,有

UIN=I1Ze+I1Z1

(3)

式中:ΔU=I1Z1为电流I1流经激磁绕组W1漏阻抗Z1引起的电压误差;I1Ze为绕组W1和W2通过主铁芯Ⅰ产生的感应电动势。

根据图2(b)等效原理图可知,第二级铁芯Ⅱ的比率绕组W2激励电压等于ΔU,因此有

ΔU=I2Z2+I2Zr

(4)

式中:I2Z2为电流I2流经比率绕组W2铁芯Ⅱ漏阻抗Z2引起的电压误差;I2Zr为ΔU通过比率绕组W2在第二级铁芯Ⅱ上产生感应电动势。

整个双级感应分压器的输出电压为

(5)

根据公式(1),可知交流电压比率标准的传递比率误差为

(6)

故双级感应分压器的传递比率误差为两级误差的乘积,极大地减小了因激磁电流而引入的误差,并改善了高频下的交流分压性能。双级感应分压器的交流比率的传递比率误差在10 kHz范围内可达10-7~10-8量级左右。

2.3 mDAC分压原理

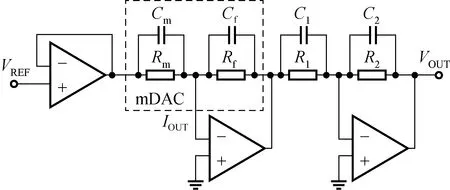

mDAC可视作1个数控电阻分压网络,其内部等效结构(虚框内)与典型电路原理图如图3所示。

图3 典型mDAC等效电路Fig.3 Typical equivalent circuit of mDAC

为表示清晰,图3未画出数字接口连接。其中,VDD是正电源输入;DGND是数字地;VREF是参考电压;RFB为反馈电阻;IOUT为电流输出;VO是输出电压。mDAC是一种电流输出型数模转换器,使用运放电路实现电压输出,输出电压为

(7)

3 可编程交流电压比率标准的设计

3.1 交流电压比率标准硬件设计

比率标准主要由基于PIC单片机的微控制单元(MCU)、包含两片数字开关模块的可编程感应分压器(PIVD)模块、mDAC模块和100:10的微差电势注入变压器组成。

如图4,UIN为电压源提供给比率标准的参考电压;VREF为mDAC经PIVD分压获得的0.1UIN参考电压;VOUT为比率标准的输出电压。上位机基于UART协议对MCU进行控制及数据交换,MCU通过GPIO控制数字开关模块、通过SPI通讯控制mDAC模块,实现输出比率的切换,同时通过内部程序实现比差的算法修正。交流电压比率标准局部实物图见图5。

图5 交流电压比率标准局部实物图Fig.5 Partial picture of AC voltage ratio standard

图6为数字开关模块框图(省略了部分电路连线),用以实现IVD的可编程控制,该模块通过5线IO控制。模块切换开关采用自锁型继电器,相比传统的CMOS开关[10],增大了工作电压范围,且导通电阻远低于CMOS开关,消除了模拟开关导通电阻的影响。自锁型继电器不需要持续的电平驱动,提供短时的驱动电平即可切换开闭状态,驱动电平消失则保持前一状态不变,可减少数字驱动电平对比率电压的影响。

图6 数字开关模块框图Fig.6 Block diagram of digital switch module

数字开关模块中译码器(74HC154)、边沿触发型D触发器(两片74HC273组成)、11片双路4选1选择器(74HC153)和继电器的组合,保证了同一时刻有且仅有1个继电器工作在闭合状态。Db[0:3]为MCU控制继电器的编码,EN[0]为控制IVD第一盘的使能信号(比率改变时提供10 ms宽的高电平信号,使继电器开闭状态改变),实现0、0.1、0.2…0.9、1.0共11种比率的输出控制。第二盘的数字开关模块使能信号EN[1]实现0.01到0.1比率的输出控制。利用两个数字开关模块,实现输出高两位比率的可编程控制,用以替代传统IVD的11位旋转开关。

mDAC模块电路设计如图7所示。图7中,虚框部分代表mDAC芯片(采用TI公司的16 bit mDAC芯片DAC8811),Cm、Cf代表mDAC芯片内由分布电容、寄生电容等组成的等效电容。利用运放、电容和电阻的外围电路设计是为实现电流输出转为电压输出和角差的修正。

图7 mDAC分压模块框图Fig.7 Block diagram of mDAC

由图7可知

(8)

令

(9)

则mDAC的分压比率KM为

(10)

3.2 比率误差的修正

由于比率标准采用高位分压器和低位分压器的组合分压架构,故比差来源于PIVD模块和mDAC模块2部分。

作为比率标准中的主比率器件,PIVD中造成比差的因素主要有等效电容、电感、导通电阻等参数,此类参数在频率一定时较为稳定,且在线路中分布较为均匀,因此随着分压比率增大呈线性增加。针对PIVD带来的比差,可通过mDAC模块进行软件上的修正。

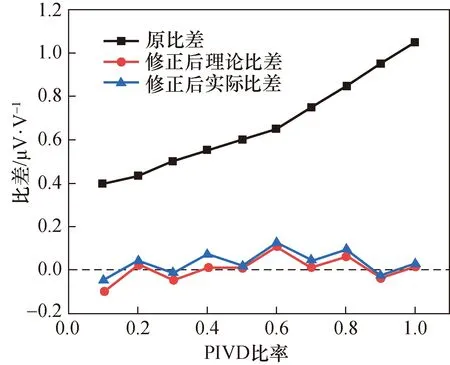

将次级分压器(mDAC)模块输出比率置0,即式(2)中KM为0。使用精密电压比较测量系统(见第4节)对输出比率在1 kHz下进行比差测试,测试结果如图8所示,其中横坐标为输出比率,纵坐标为比差。由图8可知,PIVD的比差与比率接近线性关系。

图8 PIVD比差修正Fig.8 In-phase error correction of PIVD

(11)

eI=aKI+b

(12)

式中a、b为拟合出的参数。此时,控制mDAC输出比率为

(13)

可以得到修正后的输出比率

(14)

修正后的理论比差如图8所示,基本在0.2 μV/V以内,经过实测,修正后实际比差与理论比差基本一致,验证了算法修正的有效性。

mDAC模块的比差是由于mDAC芯片的参数和运放电路的匹配电阻偏离理想值而产生的。这些参数同样分布相对均匀且稳定。因此,也使用拟合的方法,得到比差em和比率KM的拟合函数后,根据函数算得KM处的比差,再通过mDAC模块进行修正。对mDAC模块在1 kHz下测试,测试结果如图9所示,比差和比率基本呈线性,mDAC模块造成的比差最大可达4 μV/V,而经过算法修正后比差不超过0.2 μV/V,指标优化了1个数量级。

图9 mDAC比差修正Fig.9 In-phase error correction of mDAC

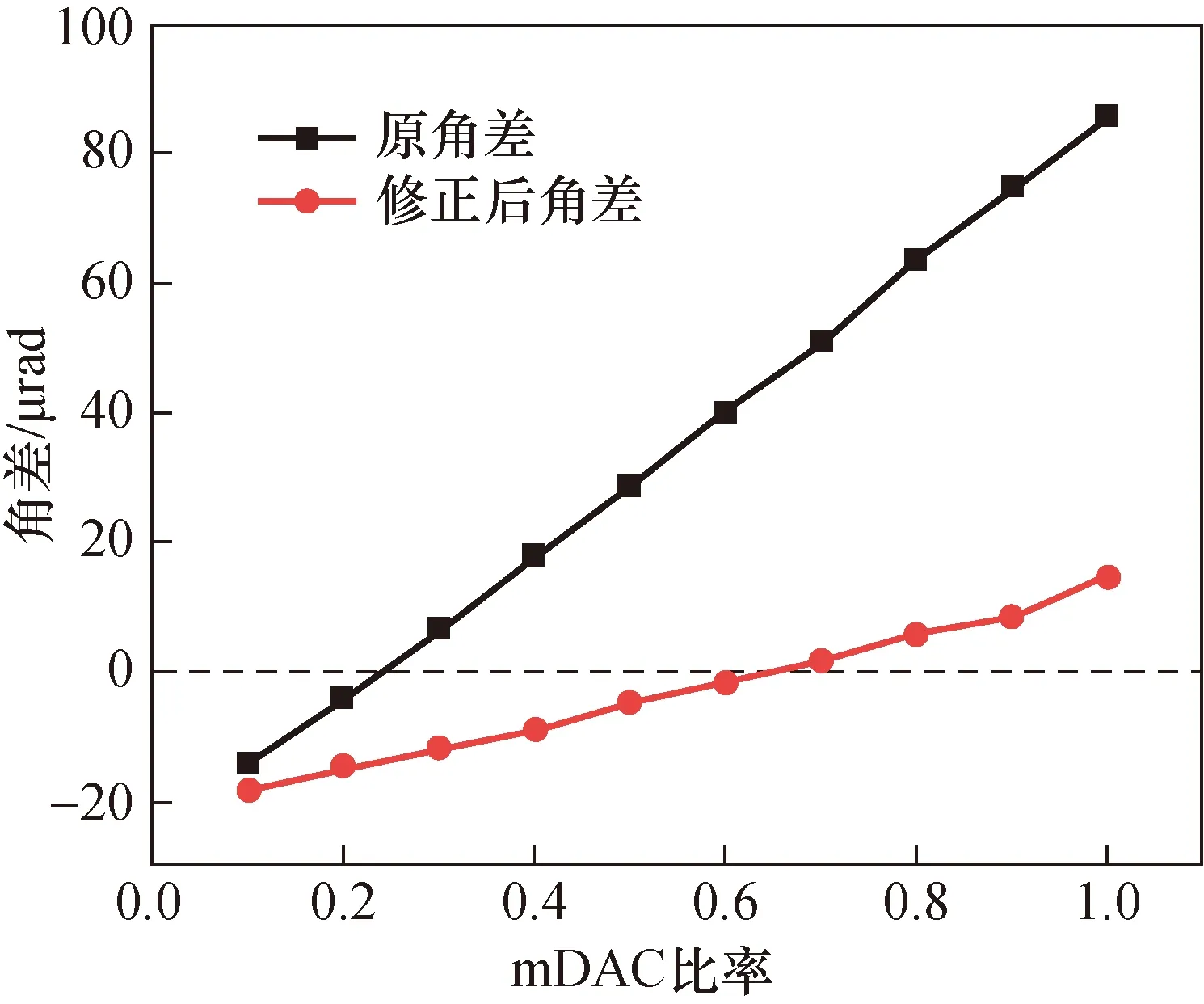

3.3 mDAC分压模块角差的修正

采用的mDAC芯片在10 kHz下的角差可高达10 mrad[19],因此需修正其对比率标准传递误差的影响。mDAC模块的相位偏移来源于芯片内部的等效输出电容与运放电路中的电容参数。由图7可知,调整C1、C2的容值,可将式(9)中p的虚数部分的绝对值降低,以减小mDAC模块的角差。

在10 kHz下,测试比率标准的角差随mDAC比率变化的结果如图10所示。可以看出,经过硬件修正后的角差明显降低,不超过20 μrad。

图10 mDAC角差修正Fig.10 Quadrature error correction of mDAC

4 实验验证

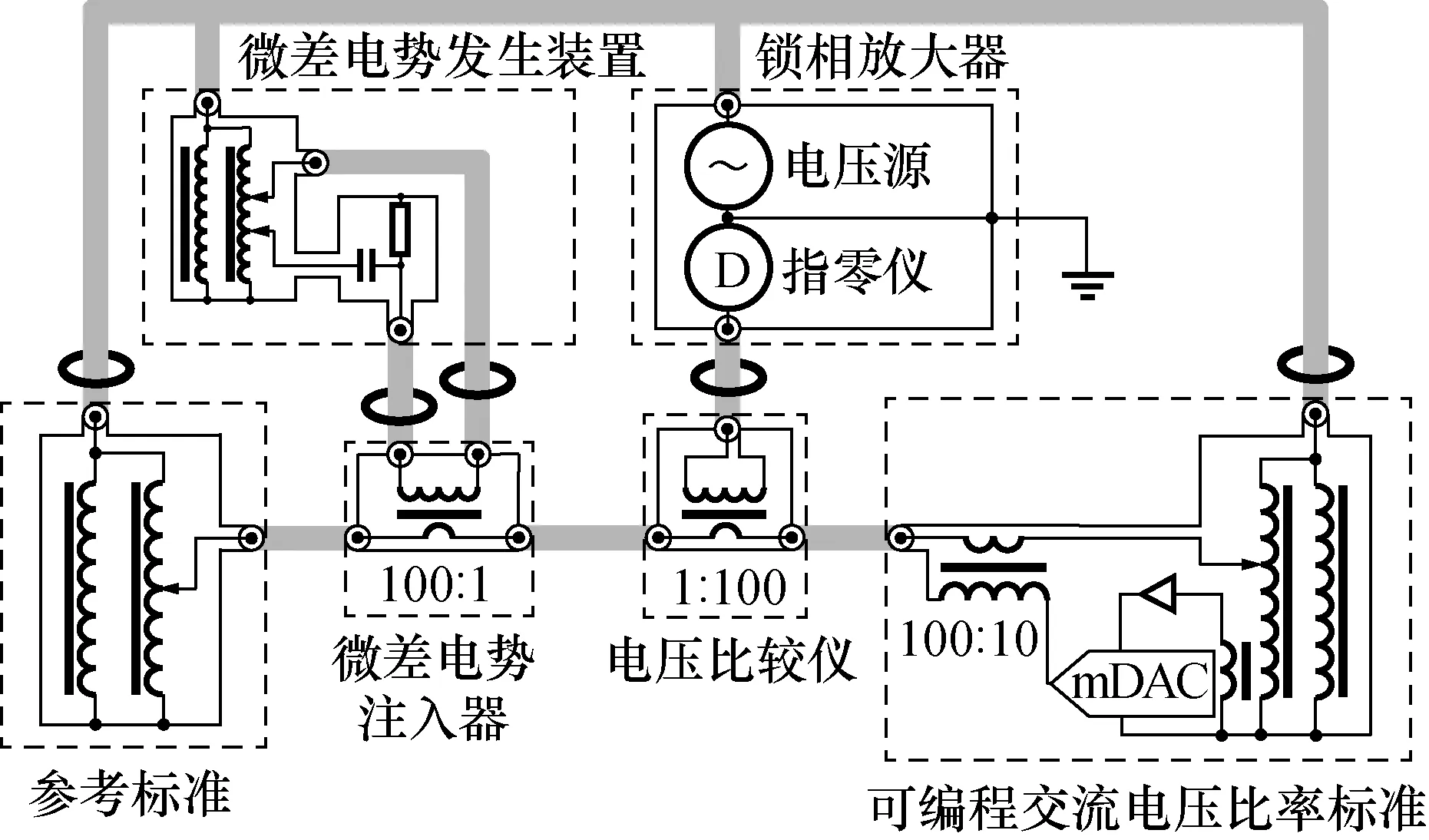

基于直接电压比较法设计并实现了1套精密交流电压比较测量系统,用以测试比率标准的精度、频率特性和时间稳定性等性能,该系统也可用于交流电压量值的传递用途。

如图11所示,交流电压比较测量系统包括被测的可编程交流电压比率标准、锁相放大器、参考标准、微差电势发生装置、微差电势注入器和电压比较仪。系统通过锁相放大器的内部电压源提供10Vrms参考电压,同时内部指零仪作为指零设备。

图11 精密电压比较测量系统框图Fig.11 Block diagram of the measuring system

参考标准采用的是经中国计量科学研究院(NIM)校准的七盘感应分压器。微差电势发生装置采用了2套七盘感应分压器,1套用作同相电势发生器,另1套的输出通过90°移相电路后输出正交电势,2路输出通过100:1的微差电势注入器注入到比较线路,可以产生10-2~10-9比率的微差电势用以平衡比较电压。

电压比较仪是1套精密无源交流电压差分放大器,其输出通过同轴电缆连接到锁相放大器的输入端进行放大比较。比率标准连接的同轴线皮线形成了短路回路,在线路上放置扼流圈形成无定向结构[16]来进行屏蔽防护。

4.1 比率标准精度测试

为验证比率标准中PIVD模块和mDAC模块的比率精度,使用表1中的3组组合比率在1 kHz下进行实验。组合比率1为PIVD第一盘工作,组合比率2为PIVD第一、二盘工作,组合比率3为PIVD及mDAC均工作。

测试结果如图12所示,横坐标为表1中的开关位置,通过查表可以得到该横坐标对应的分压比率,纵坐标表示对应比率的比差或角差。可以看出,在1 kHz下各组合比率的比差均不超过0.2 μV/V。由于组合比率3中mDAC模块工作的影响,引入的角差略大,但整体不超过1 μrad。

图12 1 kHz下组合比率的误差Fig.12 Error of combined ratio at 1 kHz

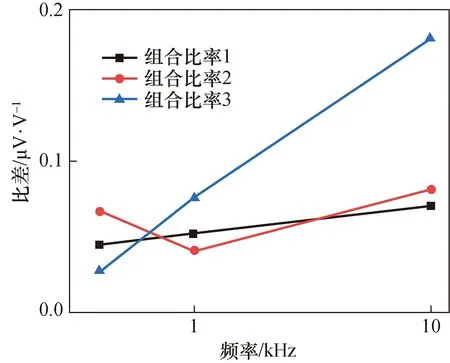

4.2 比率标准频率特性测试

使用测量系统对比率标准的频率特性进行测量。测试频率为400 Hz、1 kHz、10 kHz,分压比率采用表1的3组组合比率。在某频率下测量完1组组合比率的比差后,将该组比差的绝对值取平均后记为该频率下组合比率的比差。

图13 多频率下组合比率的误差Fig.13 Error of combined ratio at multiple frequencies

测量结果如图13所示。由图13可知,在10 kHz内,比差随频率增大而增大,且各组合比率的平均误差均不超过0.2 μV/V。

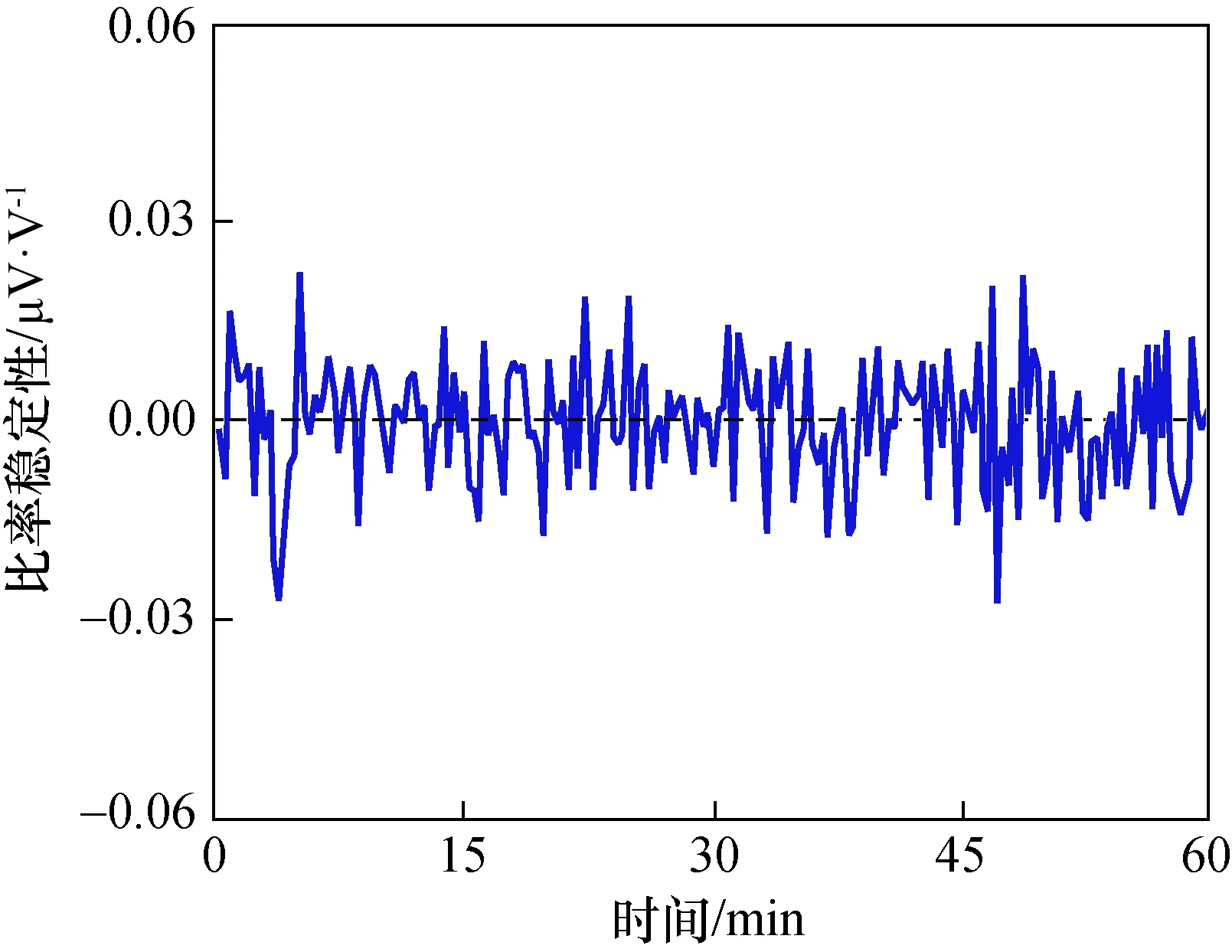

4.3 比率标准时间稳定性测试

比率标准的时间稳定性是其在各应用领域中的重要参数之一,图14显示了1 kHz下比率标准时间稳定性的测试结果。

图14 1 kHz下比率标准时间稳定性Fig.14 Time stability of the ratio standard at 1 kHz

此时比率标准分压比率为0.999 999,以保证高、低位分压器均参与分压。可以看出在60 min内,输出比率的变化在±3×10-8以内,比率标准有较好的时间稳定性。

4.4 测量系统不确定度评估

表2为精密电压比较测量系统的不确定度评估。其中A类不确定度主要来自于测量重复性,而B类的不确定度来源于微差电势注入装置、参考感应分压器以及锁相放大器的指零仪。

表2 测量系统不确定度评估Tab.2 Uncertainty budget of the measurement system

5 结 论

通过可编程双级感应分压器和mDAC分压模块组合分压的设计实现了1套高精度、可编程、便携式的交流电压比率标准。使用mDAC分压模块减小了设备体积,提高了输出电压比率的分辨率、比率切换速度和使用寿命。使用微差电势注入设计,降低了比率标准的输出阻抗。提出了比差的修正算法,将比率标准的分压精度优化了1个量级。设计并实现了1套精密交流电压比较测量系统,经实验验证,比率标准工作频率范围为50 Hz~10 kHz,工作频率范围内比差优于0.2 μV/V,在1 kHz下的角差优于1 μrad。