基于AES算法的eFlash控制器安全设计

2023-10-21林宇红

林宇红,肖 昊

(合肥工业大学 微电子学院,安徽 合肥 230009)

随着信息全球化和移动信息的迅猛发展,信息安全问题在各个领域备受关注。存储器是专用集成电路(ASIC)芯片中重要的组成部分,其作为密码信息的重要载体,主要存储芯片执行代码、芯片操作数据以及应用者密钥等重要信息。芯片数据的存储对客户安全应用具有重要意义,如果芯片自身的安全防护能力过于薄弱,将导致芯片存在安全缺陷漏洞或遭遇黑客攻击,带来较严重的安全威胁。因此,增强信息存储安全以禁止非相关人员进行人为操作或者非法篡改十分必要。密码算法加密实现平台主要由硬件、软件和芯片组成。软件实现安全特性会导致控制指令延时,从而影响功能安全特性的实现。硬件实现占用空间大,成本较大,影响使用场合。与硬件加密和软件加密相比,芯片加密具有集成度高、资源消耗少等优势[1]。设计ASIC芯片对嵌入内部的快闪存储器(eFlash)数据进行加密以确保数据安全是效果较好的设计方案。

目前已有学者在防御Flash安全攻击方面展开了研究。在软件层面,文献[2]基于JFFS2 (Journaling Flash File System Version 2)设计了符合嵌入式系统特点和Flash物理特性的加密文件系统。该加密方案基于嵌入式软件平台,将加密算法直接移植到嵌入式系统。由于软件主要是串行处理数据,高延时降低系统的性能,该加密方案使系统性能降低了28%。在硬件层面,文献[3]使用复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)设计了Flash存储加密,在处理器和Flash总线之间串联一块CPLD,对Flash地址线以及数据线进行加密处理。CPLD是可编程器件,虽然能够完成各类算法和组合逻辑控制电路,但其成本高且集成度低[4]。

高级加密标准(AES)算法是由美国国家标准技术研究所(NIST)为替代DES而发布的新一代数据高级加密标准[5]。AES加密算法是一种具有运行快、安全性高以及资源消耗少等特点的密码算法,在加密算法类型中,AES加密算法是较好的选择。本文在ASIC芯片内设计一种基于AES算法对eFlash存储数据加密的控制器,可有效避免他人篡改或攻击eFlash存储的关键信息。

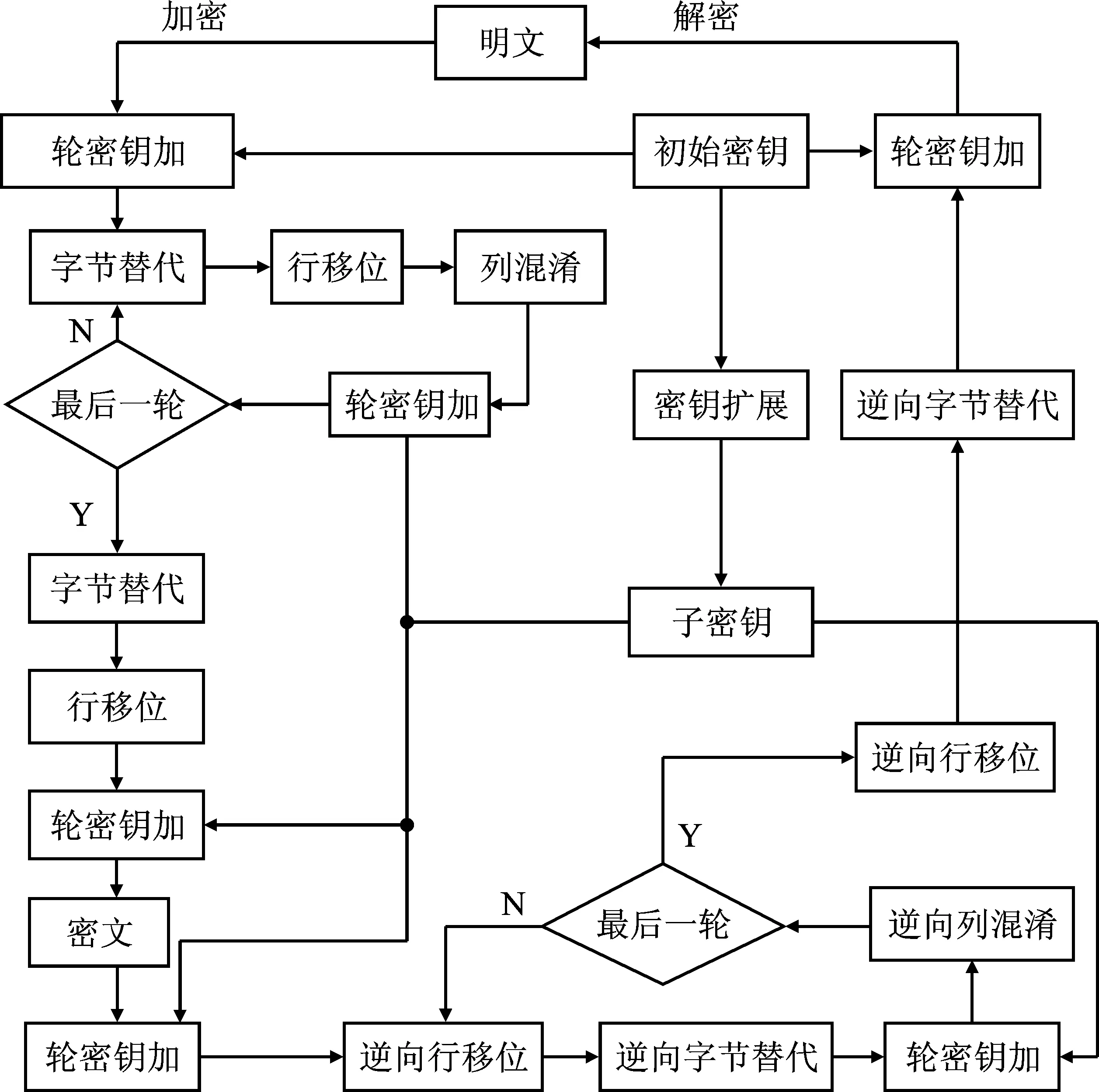

1 AES算法描述

AES是一种分组对称的密码算法,分组数据块长度为固定128 bit,密钥的长度可支持128 bit、192 bit和256 bit[6]。根据密钥长度不同,分组长度与加密轮数的关系为:AES-128的轮数为10,AES-192的轮数为12,AES-256的轮数为14[7]。AES的轮函数主要由下面字节替换、行移位、列混淆以及轮密钥加组成。

字节替换可视为16个并行的非线性元素S盒,且每个S盒的数据传输都是8位。实现8 bit输入到8 bit输出的映射,输入的低4位值是位列标,输入的高4位值是位行标。在此过程中,每个状态字节Ai都被替换为另外一个字节Bi,计算式为B[h,k]=S(A[h,k]),其本质是一个查表过程[8]。

行位移用于提供算法的扩散性,基于字节替换的状态矩阵对其向左循环移位的操作。状态矩阵第1行不移位,第2行、第3行和第4行则分别向左循环移位1个、2个和3个Byte[9]。

列混淆对状态矩阵的每列进行线性变换[10]。状态矩阵的每列来自有限域GF(28)的多项式s(x),与一个固定多项式a(x)相乘的结果再与x4+1进行取模得到s′(x)[11],其数学关系如式(1)和式(2)所示。

a(x)=(03)×x3+(01)×x2+(01)×x+(02)

(1)

s′(x)=a(x)⊕s(x)

(2)

轮密钥加是列混淆后的矩阵S与密钥矩阵K进行异或处理,其数学关系为S′[a,b]=S[a,b]⊕K[a,b],a,b∈[0,3]。

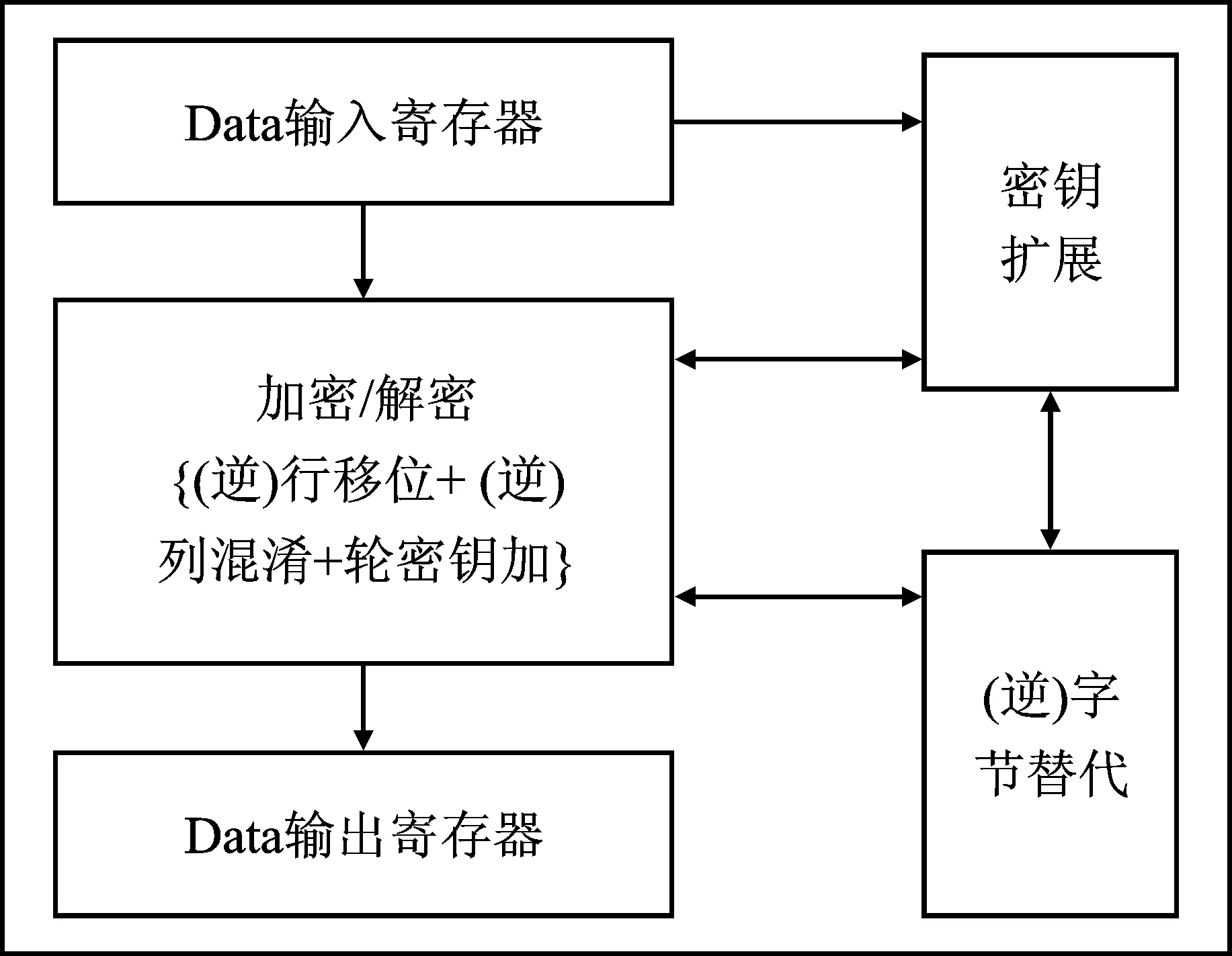

AES由不同的层组成,每一层操纵数据路径对应的数据。AES算法的加解密流程如图1所示。

图1 AES加解密流程Figure 1. AES encryption and decryption flow

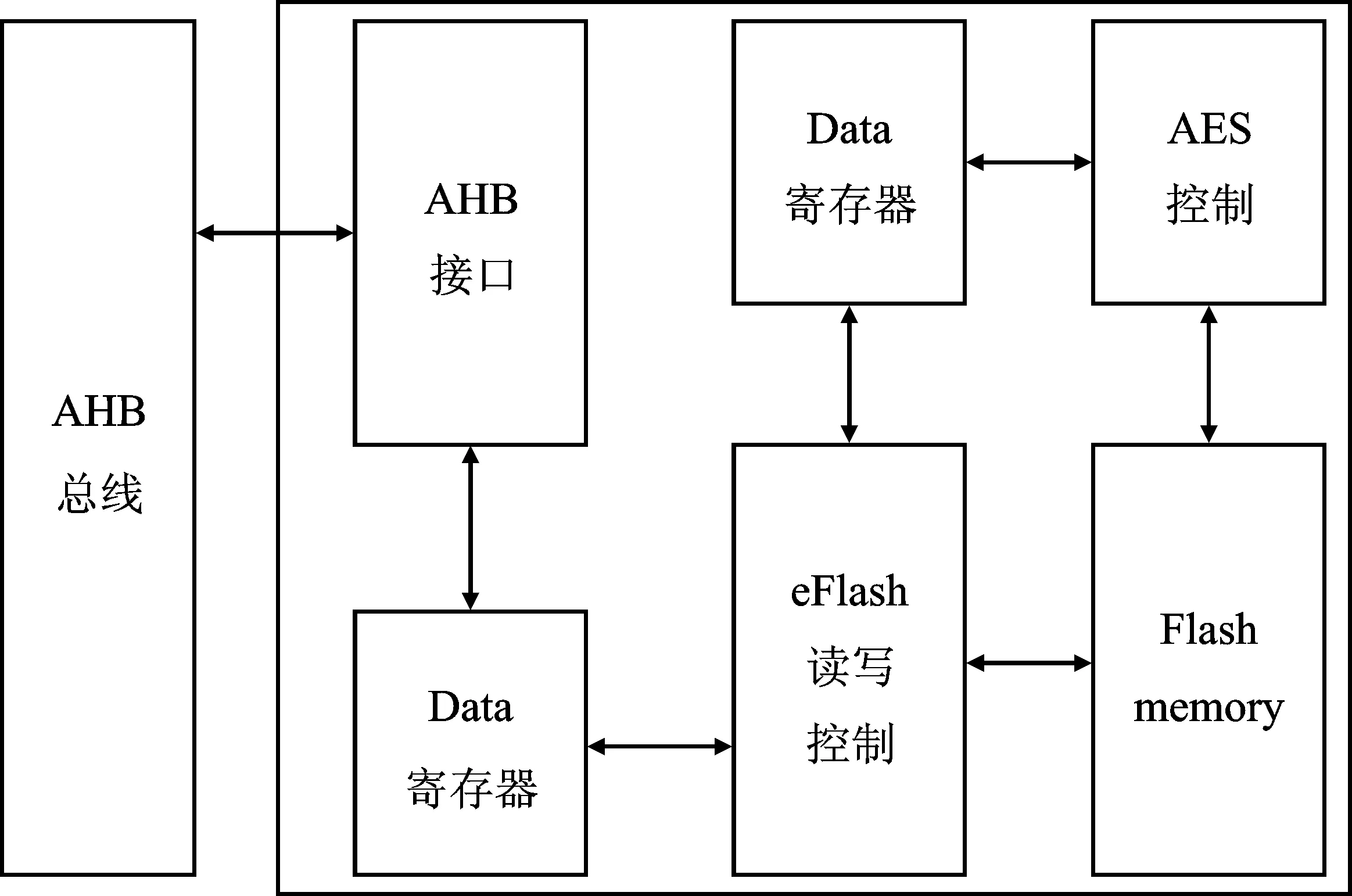

2 控制器安全设计

2.1 控制器的总体实现

eFlash控制器的功能是对eFlash数据存储操作(读/写/擦除)的控制[12]和对存储数据加密,由AHB接口模块、eFlash控制模块和AES加密模块等组成[13],其系统控制架构[14]如图2所示。

图2 eFlash系统控制器模块Figure 2. eFlash system controller module

AHB接口模块接收来自AHB总线发送的控制信号、地址信号和数据信号并对其做分析处理。eFlash地址,配置是根据AHB地址配置由译码器转换成相应的eFlash地址。AHB接口信号根据组合逻辑和时序逻辑组成逻辑电路对eFlash控制模块的接口信号进行信息交互控制。

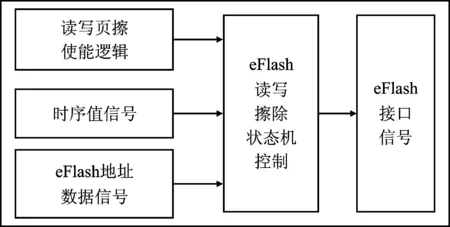

eFlash控制模块接收AHB接口模块发送的总线地址和命令信号,生成eFlash数据读写擦除时序、逻辑控制信号和eFlash地址信号对eFlash的读、写和擦除的操作控制,同时产生对应的eFlash状态信息,并反馈到AHB接口模块中进行分析和判断。其控制结构如图3所示。

图3 eFlash控制模块Figure 3. eFlash control module

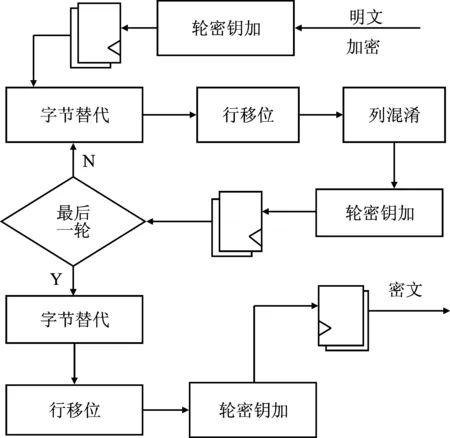

eFlash控制器内部增加AES控制模块对eFlash存储数据加密。AES加密控制模块设计主要由Data输入寄存器模块、Data输出寄存器模块、字节替换模块、密钥扩展模块以及加解密模块等组成[15]。

在AES加密时,将需要写入eFlash的数据先传输到Data输入寄存器中,根据控制信号模式配置输入密钥或者明文,将数据输入到密钥扩展模块或者加密模块进行数据解析。由密钥扩展模块生成子密钥与加密模块中的轮密钥加层生成的数据进行异或处理,经10轮迭代处理生成密文,随后将密文传输到Data输出寄存器中等待eFlash控制模块解析处理写入到eFlash里。

在AES解密时,从eFlash中读出相应数据到Data输入寄存器中,将数据提取到解密模块中进行数据解析。由密钥扩展模块生成子密钥与解密模块中轮密钥加层生成的数据进行异或处理,经10轮迭代处理生成明文,产生的明文输出到Data输出寄存器等待eFlash控制模块解析处理后输出到AHB接口模块。其AES控制模块如图4所示。

图4 AES控制模块Figure 4. AES control modul

2.2 加解密流程实现方案

2.2.1 数据流水线结构

对于分组密码加密实现有迭代结构、循环展开结构和并行流水线结构等方法[16]。迭代结构运算周期内完成一个数据的加密操作,此实现方法操作速度慢且逻辑资源消耗小,比较适合对速度要求低但对面积要求高的情况采用。将迭代结构展开就是循环展开结构,标准的AES方案属于循环展开结构,此方法虽然提高了运算速度,但需要更多的逻辑资源增大芯片面积。在设计芯片时,尽量对速度和面积进行折中处理,在满足速度要求的前提下尽量减少资源损耗。流水线结构介于迭代结构和循环展开结构之间,符合此设计。

使用流水线技术关键是加密时将数据切分多级执行降低分组数据处理时间,在执行过程中插入寄存器储存执行结果。此过程并未改变硬件逻辑流程,但是可以在较少周期内同时处理多个数据块加密,提高了并行处理能力,从而加快数据处理速度。本文设计在循环展开结构加密流程的每轮间插入寄存器存储每轮执行结果,寄存器控制采用同步时钟处理,当时钟触发时保存上轮变换结果,同时将上次保存结果送至流水线处理并将处理结果保存至下一级寄存器中,其流程结构如图5所示。

图5 AES加密流水线结构Figure 5. AES encrypted pipeline structure

2.2.2 数据加解密流程

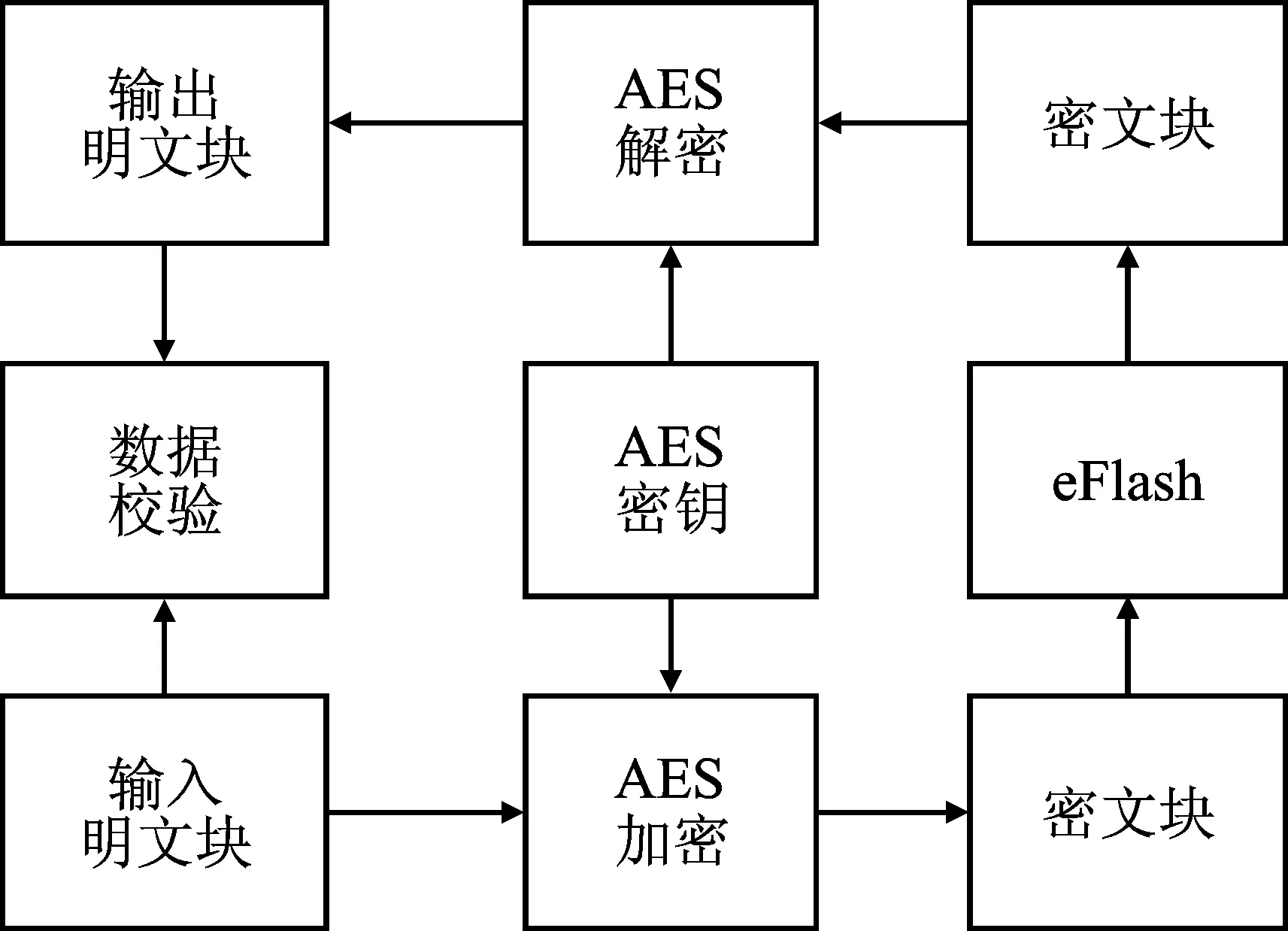

eFlash控制器加密流程为:首先,eFlash控制模块写入密钥数据,存储到寄存器缓存中得到密钥,密钥在加解密中公用;其次,配置数据状态模式为输入模式,将数据写入明文块;最后,将密钥与输入明文进行加密处理生成密文块并写入eFlash。

eFlash控制器解密流程为:首先,eFlash控制模块配置数据状态模式为输出模式,将eFlash数据读出到密文块;其次,调用加密时的密钥与输出密文解密处理生成明文块输出;最后,在解密过程中将解密输出的明文与加密输入的明文进行数据校对以判断数据有效性[17]。整体流程如图6所示。

图6 eFlash加解密流程Figure 6. eFlash encryption and decryption process

3 模块仿真及结果分析

3.1 仿真及结果分析

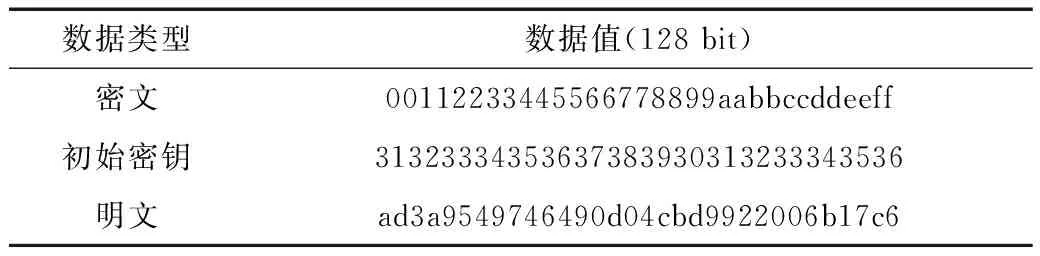

系统采用可综合的Verilog行为级RTL代码实现,在VCS和Verdi的联合环境下构建Testcase对系统功能进行了联合仿真和验证。在对eFlash数据读写加解密运算后,得到的加密和解密结果如表1和表2所示。

表1 加密数据测试Table 1. Encrypted data test

表2 解密数据测试Table 2. Decrypted data test

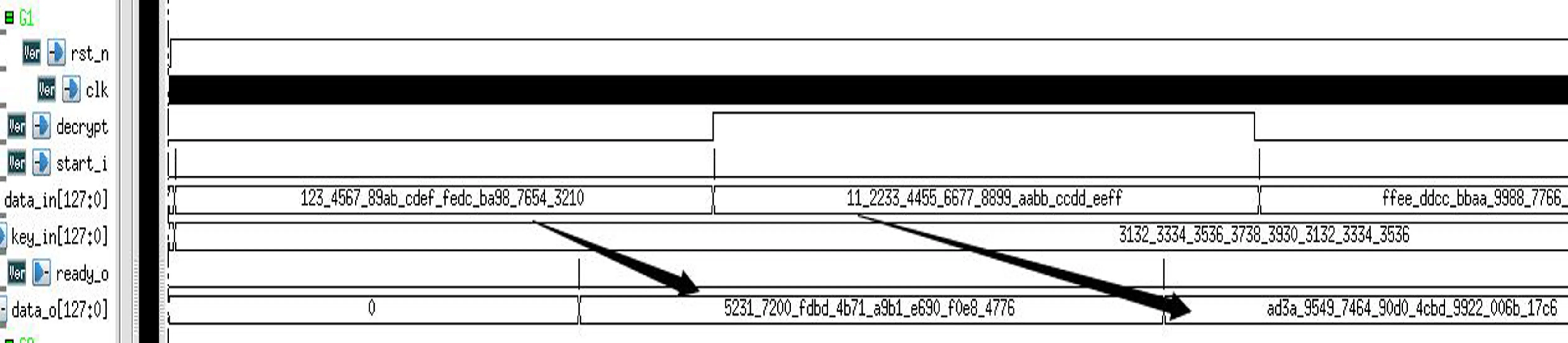

将表1和表2中的运算数据与图7的仿真数据对比可知,在加密测试时输入表1所示的明文和密钥的测试结果得到的密文与仿真结果一致;在解密时输入表2所示的密文和密钥的测试结果得到的明文与仿真结构一致。

图7 加解密数据仿真Figure 7. Simulations of decrypted data

3.2 性能分析

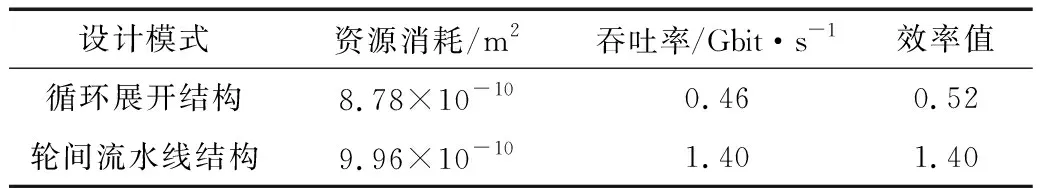

在180 nmCMOS工艺下利用综合工具对系统设计进行逻辑综合。仿真结果表明可实现的最高工作频率为120 MHz,AES最大吞吐率可达1.4 Gbit·s-1。128 bit密钥扩展产生10轮子密钥的加密流程需要33个时钟周期。流水线设计密钥扩展和加密运算并行处理会提高数据处理速度,使整体运行周期只需11个周期,AES实现方法对比结果如表3所示。本文的流水线结构设计在加密流程轮间插入寄存器和选择器,虽然逻辑资源消耗比循环展开结构设计高,但加密运算耗费的时钟周期减少,使得加解密的数据吞吐率具有较大提升。采用吞吐率与消耗资源的比值衡量其效率值,流水线结构设计效率比提升2.7倍。eFlash控制器增加AES模块前后读、写、擦除耗时关系如表4所示,eFlash控制器综合得出的消耗面积为4.77×10-9m2,其中AES模块消耗资源面积占9.96×10-10m2,可得出AES在系统资源占比并不大,说明在确保eFlash存储数据安全前提下增加AES模块带来资源消耗是可以接受的。

表3 AES实现方法对比Table 3. Comparison of AES implementation methods

表4 eFlash控制器加密128 bit耗时对比Table 4. Comparison of 128 bit encryption time of eFlash controller

由表4可知,eFlash控制器增加AES模块会导致控制数据时序有一定延时。eFlash正常读128 bit数据需要28个时钟周期,加AES模块后读128 bit数据时,AHB总线32位传输、AES加密模块功能和选择器会产生18个时钟周期的延时。同样,eFlash正常读写128 bit数据需要22 988个时钟周期,增加AES模块后写128 bit数据同样会产生18个时钟周期的延时,擦除功能延时比较小。虽然基于ASIC芯片设计对数据加密需要消耗逻辑资源并降低运算速度,但与基于软件和硬件的加密模式相比,其仍具有集成度高和运算快的优势。

4 结束语

本文设计实现了基于AES算法的eFlash安全存储数据控制器,在通用eFlash控制器基础上增加了AES模块,eFlash控制器在正常控制存储的同时加强了存储数据安全。对系统功能仿真测试和逻辑综合验证了本文设计基本满足设计规格要求。该控制器完全由硬件实现,具有集成度高和安全性强等特点,可以在其他场合推广应用。