基于现场可编程门阵列与用户数据报协议的测功机动态加载系统设计

2023-09-27竺春祥郎向荣张众杰钱嘉程

竺春祥,郎向荣,张众杰,钱嘉程,宋 畅

(1.中国计量大学工程训练中心/创新学院,杭州 310000;2.杭州威衡科技有限公司,杭州 311112;3.浙江方圆检测集团股份有限公司,杭州 310016)

随着我国“工业4.0”和中国制造2025 战略的持续推进,国家大力提倡走中国特色新型工业化道路,以促进传统制造业转型升级为主题,以提质增效为中心,以加快新一代信息技术与制造业融合为主线,以满足经济社会和国防建设对重大技术装备需求为目标,完成制造业从大变强的历史跨越。这对我国电机制造业来说,既提出了挑战,也是一种机遇。电机是一种重要的机电产品,其广泛应用于从农业生产到人们日常生活的各个领域和部门。尤其在新能源汽车行业、工业机器人行业、航空航天等领域[1-4],不仅需要大量使用电机及其控制系统,甚至对其性能要求也与日俱增。而电机测试技术是提高电机及其控制系统质量的一项重要保障,在电机的转型升级中发挥着重要的作用,因而多年来一直受到电机界的重视和关注。

本文设计了基于UDP(用户数据报协议)的电机测试系统。随着电机在工业生产中的广泛应用,对其性能的测试和分析变得越来越重要。传统的电机测试方法通常采用传感器等硬件设备进行数据采集和处理,但这种方法成本较高、复杂度较大。随着网络技术的发展,基于网络的电机测试系统也得到了广泛的应用,具有成本低、便于管理、数据传输速度快等优点。UDP 是一种无连接的协议,具有传输速度快、开销小等特点[5-10]。因此,UDP 协议被广泛用于需要快速传输数据的应用中,如流媒体、视频游戏等。本文采用UDP 协议作为不同模块之间的通信协议,以实现电机测试数据的快速、高效传输。

1 电机测试系统总体结构设计

系统硬件主要由FPGAC、ADC 模块、DAC 模块和隔离模块组成。FPGA 主控系统主要包括脉冲输出电路、转速/转矩测量输入模块、高速ADC 输入模块AD7606、高速DAC 输出模块AD9767、低通滤波电路和网口电路等。装置主要工作流程为FPGA 各路控制线程启动,等待接收上位机指令,当接收到上位机通过UDP 协议从网口传来的测试波形的指令时,FPGA 测量相应的Vpp 与频率值; 当接收到上位机的输出波形指令时,实时输出相应波形的精确信号。为测功机的典型结构组成图如图1 所示。

图1 测功机实物

2 硬件电路设计

FPGA 主控采用Cyclone-IV 系列芯片,型号为EP4CE10F17C8,使用立创EDA 和Altium designer 设计电路板,完成产品设计,包括FPGA 最小系统电路、以太网电路、ADC 电路和DAC 电路等。硬件实物图如图2 所示。

图2 硬件设计实物图

2.1 FPGA 最小系统

FPGA 最小系统电路主要包括电源电路、GPIO 接口、Jtag 下载接口和其他接口电路,FPGA 的型号为EP4CE10F17C8,核心板采用Intel(原Altera)公司Cyclone IV E 系列FPGA 作为核心主控,配以256 Mbit大容量SDRAM 存储器,可以嵌入式软核CPU NIOS II,实现SOPC 系统,或者使用Verilog 逻辑实现各种数据采集系统。核心板是武汉芯路恒科技有限公司针对企业和高校用户开发的一款工业级、易用型FPGA 核心板。板载资源包括85 个通用双向IO、5 对LVDS IO(也可作为双向通用IO 使用)、1 对LVDS 时钟输入IO(也可以作为通用的输入单向IO 使用)、12 个时钟输入IO(不含LVDS 时钟输入IO)、5 个GND(硬件连通)、4 个VDD3.3 输入(硬件连通)、1 个VDD2.5 输出(用作底板上JTAG 接口供电电源)、1 个VDD1.2 输出(预留,一般不使用)及4 个JTAG IO 口。

2.2 以太网UDP 接口电路模块

以太网电路采用W5500 为核心的电路,电路原理图如图3 所示。W5500 芯片是一种硬接线TCP/IP 嵌入式以太网控制器,可为嵌入式系统提供更方便的互联网连接。W5500 使用户只需使用嵌入TCP/IP 堆栈、10/100 以太网MAC 和PHY 的单个芯片,就可以在其应用程序中实现互联网连接。支持硬接线TCP/IP 协议有TCP、UDP、ICMP、IPv4、ARP、IGMP 和PPPoE。在本文中,采用UDP 连接做为上下位机的通信。

图3 ADC 电路原理图

2.3 ADC 电路

ADC 电路图如图3 所示,ADC 芯片为AD7606,AD7606 是ADI 公司针对电源设计、工业检测、闭环控制等工业应用推出的一款,16 位、八通道同步并行采样adc芯片,采样率最高为每通道200 KSPS,输入电压范围±5 V,最高可达±10 V,该芯片满足工业级应用的温度范围。

2.4 DAC 电路

本设计使用在模拟半导体领域享有盛誉的ADI公司AD9767 型DAC 芯片,该芯片为双通道,14 位、125 Msps 转换速率的高性能DAC 芯片,支持I、Q 输出模式(该模式常用于数字通信领域)。输出形式为差分电流输出,输出电流满量程范围为可设置为2~20 mA。芯片本身自带1.2 V 的参考电压,无需外部提供参考源。DAC 电路图如图4 所示。

图4 DAC 电路原理图

3 软件设计

本文设计的电机测试系统基于UDP 协议,使用Visual Studio 和C#语言进行开发。软件程序设计总体结构如图5 所示,包括上位机软件开发和硬件程序设计。上位机软件在Qt 开发环境下,使用QChart 绘图库,通过不断测试优化过的UDP 协议与下位机完成通信连接,实现电机系统的实时数据测量以及数据存储并且实时显示。FPGA 使用Quartus 13.0 设计并完成测控电路系统的实施搭建,实现ADC 采集数据、DAC 输出及频率测试等功能。具体实现过程如下。

图5 软件流程图

3.1 数据采集模块

通过连接电机传感器和信号放大器等硬件设备,将测试数据采集并封装为UDP 数据包进行传输。

3.2 控制模块

接收并解析UDP 数据包,实现对电机的控制和数据采集协调。

3.3 数据指令解析模块

接收并解析UDP 数据包,将测试数据进行处理并生成测试报告。

3.4 信号加载模块

通过上位机控制DAC 输出模拟量到电机驱动器,控制电机的转速或转矩,结合PID 控制算法,实现转速转矩的闭环控制。

3.5 数据采集模块

主要采集转速转矩传感器的信号,通过信号解析成实时转速转矩的反馈量,实现PID 闭环控制。

3.6 波形可视化

上位机采用Qt 编写电机测试界面,对指令的输出和信号的输入进行可视化显示,便于用户操作测试流程。

4 实验结果分析

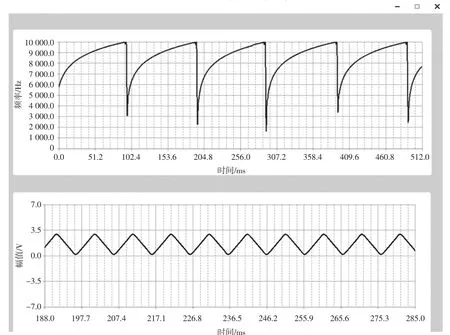

本文对设计的电机测试系统进行了实验验证,结果表明,系统能够满足实时性要求,测试数据的传输和处理速度较快。不仅能够加载方波、正弦、三角波等波形,如图6 所示,也能够系统实现对电机转矩转速信号的测试和分析,生成符合要求的测试报告。完整的上位机图像显示如图7 所示,主要是转矩转速信号的实时采集和显示。

图6 方波加载信号输出

图7 转矩转速波形输入测量与实时显示

5 结论

本文设计的基于UDP 协议的电机测试系统具有成本低、数据传输速度快等优点。同时,设计了基于双通道AD9767 的DAC、基于AD9767-4 的ADC 以及测频3 个数据采集模块,能实时完成与上位机的交互,完成实时精确的数据发送与接收。实验结果表明,该系统能够满足实时性要求,同时提高了测试效率和数据传输速度。该系统在电机测试和分析中具有广泛的应用前景。