利用SigXplorer 进行高速信号仿真研究

2023-09-17聂俊英

聂俊英

(西安睿控创合电子科技有限公司,陕西 西安 710071)

1 研究背景

随着高速信号在单板设计中的应用越来越广泛,高速数字信号快速上升引起的模拟效应对单板设计的影响也越来越大,由此产生了一系列信号完整性、传输线效应、阻抗匹配、时序冗余、电源完整性等问题。而在已有的PCB(Printed Circuit Board,印制电路板)上发现和分析这些问题是一件非常困难的事情,即使找到了问题,对于一个已完成的PCB 要解决这些问题也要花费大量的时间和费用。如果在设计初期和设计过程中就考虑这些方面的影响,修改同样的问题所花费的时间和费用就少得多,甚至能避免产生这样的问题。利用Cadence 公司强大的EDA 仿真软件SigXplorer 就是一种有效的方法,可在PCB 设计前期和后期对高速信号进行仿真和分析,并根据仿真结果生成约束条件导入到PCB 设计工具中,作为PCB 布线的约束。

2 利用SigXplorer 进行仿真的方法

要利用SigXplorer 进行仿真,必须要有所要仿真器件的 IBIS ( Input/Output Buffer Information Specification,一种基于V/I曲线的对I/O BUFFER 快速准确建模的方法)模型。由于IBIS 模型是行为级模型,一般都可以通过公开的渠道获得器件的IBIS 模型。启动SigXplorer 后,通过菜单Analyze→library 打开库浏览器,在浏览器中可以将IBIS 模型转换为SigXplorer所认识的DML(Data Manipulation Language,数据操纵语言)来进行分析。将DML 格式文件装入库管理列表中后就可以进行仿真了。本文主要介绍3 种类型仿真,即信号完整性仿真(Signal Integrality Simulating)、时序仿真(Timing Simulating)和拓扑结构仿真(Topology Simulating)。仿真的对象可以在PCB 中自动提取,也可以手工建立。

2.1 信号完整性仿真

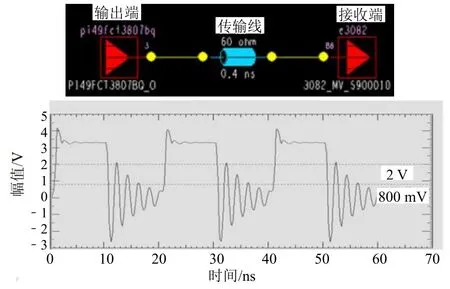

目前,高速电路设计领域,随着IC(Internal Circulation,集成电路)输出开关速度的提高,不管信号周期如何,几乎所有设计都遇到了信号完整性问题。信号完整性问题主要指信号的过冲和阻尼振荡现象。SigXplorer 设计工具可以仿真实际物理设计中的各种参数,对系统中的信号完整性问题进行定量、定性的分析。根据传输线理论,如果一个信号在传输线末端的阻抗没有被匹配端接,那么将会在不连续端被反射,信号的一部分将会反射回源端[1]。当反射信号到达源端时,如果源端阻抗不等于传输线阻抗另一个反射也将产生。因此,如果传输线的两端都不连续的话,信号将会在驱动和接收之间来回反射,导致接收端波形产生过冲和振荡。如果过冲太大,将会损坏芯片的内部结构,使它失效。一般来说,上、下过冲不要超过0.8 V;最后还要注意振荡,一般不要超过3 个明显的振荡波形。图1 为未加任何处理情况下的仿真模型以及仿真得到的接收端波形,从图中可以看到,过冲超过了0.8 V,且振荡现象明显。

图1 未加串联匹配电阻仿真得到的波形

利用以下3个方法可以减轻反射带来的负面影响:①降低系统频率以便在另一个信号加到传输线上之前传输线的反射到达稳态,这个对于高速系统通常是不可能的;②缩短PCB 走线以便反射在短时间达到稳态,但是这样做会增加PCB 板层,成本提高很多,不切实际;③在传输线的两端用等于线的特征阻抗的电阻端接以减少甚至排除反射[2]。其中串行端接是最常用的一种端接方式,通过在尽量靠近源端的位置串行插入一个电阻R(典型值为10~75 Ω)到传输线中实现。在上个例子中,在驱动器端端接一个50 Ω电阻并且仿真得到的波形如图2 所示,从图中可以看到,加了串行端接电阻后过冲明显减小,并且振荡现象得到很大缓解,波形很平滑,符合设计的要求。一般来说,端接电阻越大,吸收反射的效果越好,但是也不能加的太大,一般在30~70 Ω之间,否则会因为电阻太大,驱动器驱动能力不足导致接收端波形出现回沟现象。对于高频率时钟信号,尽量不要出现1 个驱动源同时驱动2 个以上负载的情况。如果确实需要接2 个以上负载,最好使用时钟驱动器。对时钟信号的仿真,除了满足一般信号的信号完整性要求外,还要求信号具有良好的单调性(上升沿和下降沿)。这是为了防止时钟信号在逻辑电平门限附近多次穿越。

图2 加串联匹配电阻后仿真得到的波形

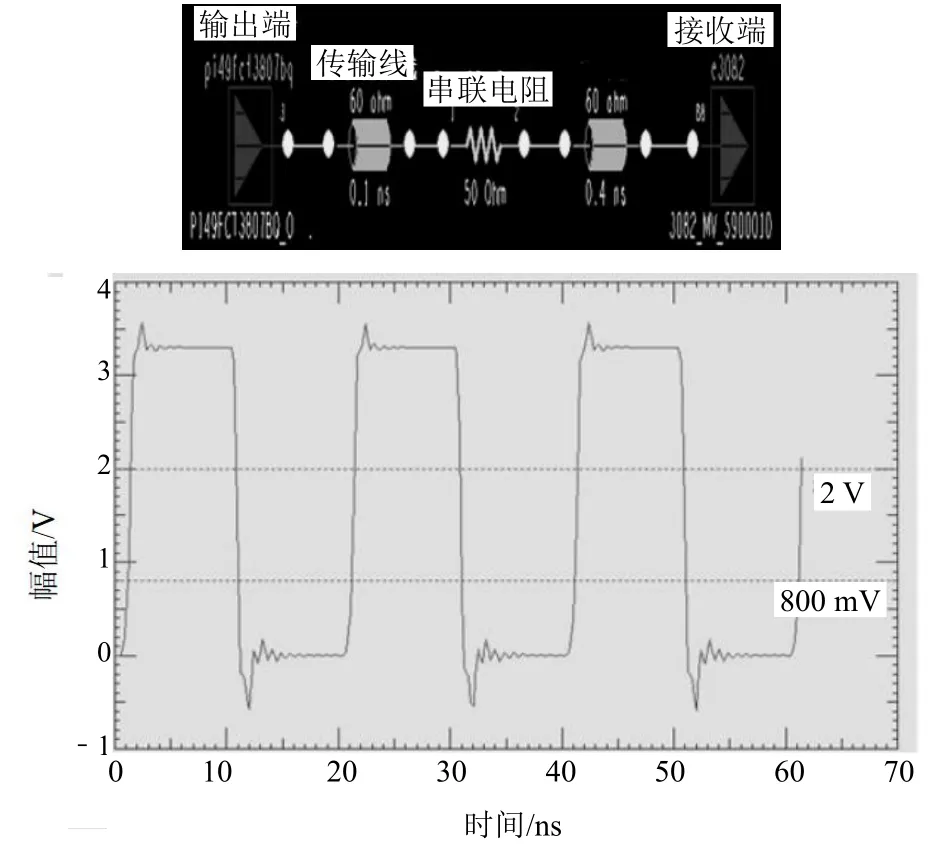

2.2 时序仿真

根据芯片间信号传递方式的不同,信号类型可分为同步和异步。同步信号是通过时钟来同步数据传输,有严格的时序关系,时序仿真主要针对的就是同步信号。对于异步信号,没有时钟作为基准,而且工作频率较低,时序容易满足,一般不需要时序仿真,主要关注信号的质量,如单调性、过冲等。时序仿真的目的是通过电路原理、器件手册来获得一个最恶劣条件下的时序最大可用空间,并通过Cadence 仿真软件计算出在满足这个条件下的元器件布局布线约束。根据时钟传递方式不同,同步信号可以分为外同步、源同步,2 种同步的差别在于时钟和数据的相对关系,如图3、图4 所示。外同步是指数据在2 个芯片间传输时,时钟由另一块芯片提供的信号类型。同步时钟不是由发送数据或接收数据的芯片提供,一般有独立的时钟驱动器。外同步方式时序分析的要点是用发送数据时钟的下一个时钟来接收数据。这种结构应用的场合比较多,比如处理器外接以太网PHY(物理层)的情况。

图3 外同步方式

图4 源同步方式

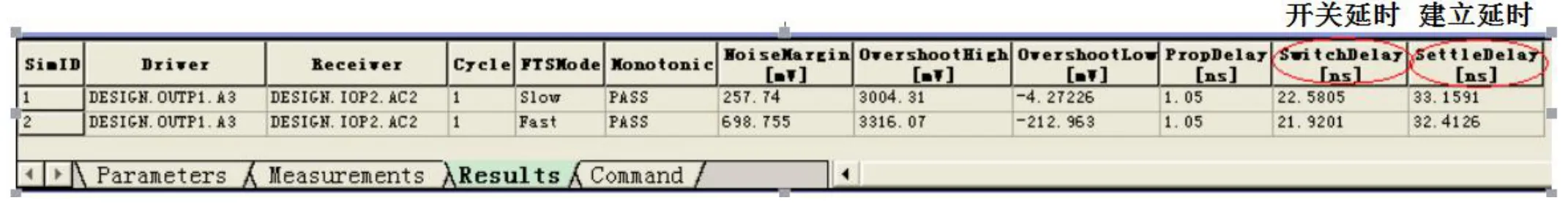

在slow 和fast 这2 种状态下,仿真结果应该满足以下条件:slow 状态应满足TSettleDelay(建立延时值)<Tflt-max(最大飞行时间),fast 状态应满足TSwitchDelay(开关延时值)>Tflt-min(最小飞行时间)。TSettleDelay和TSwitchDelay是通过SigXplorer 仿真软件得到的,如图5 所示,也可以在波形图中自己手动测量。

图5 建立延时(SettleDelay)和开关延时(SwitchDelay)

最大飞行时间Tflt-max和最小飞行时间Tflt-min是通过时序计算公式得到的。计算公式如下:

式中:Tco-max为输出信号端输出时钟到数据有效的最大时间的数值;Tsu为建立时间的数值;Tjitter为时钟抖动(cycle to cycle的抖动)的数值;Tskew为时钟偏移的数值,这是指时钟驱动器不同输出端output to output skew;Tmargin-fast和Tmargin-slow为fast和slow这2种状态下的时序设计余量的数值,一般可取300 ps;Tcycle为时钟周期的数值;Tco-min为输出信号端输出时钟到数据有效的最小时间的数值;Thd为保持时间的数值。

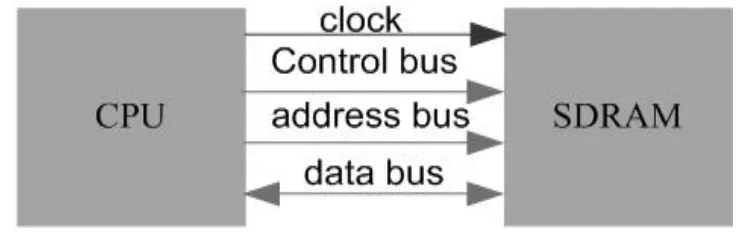

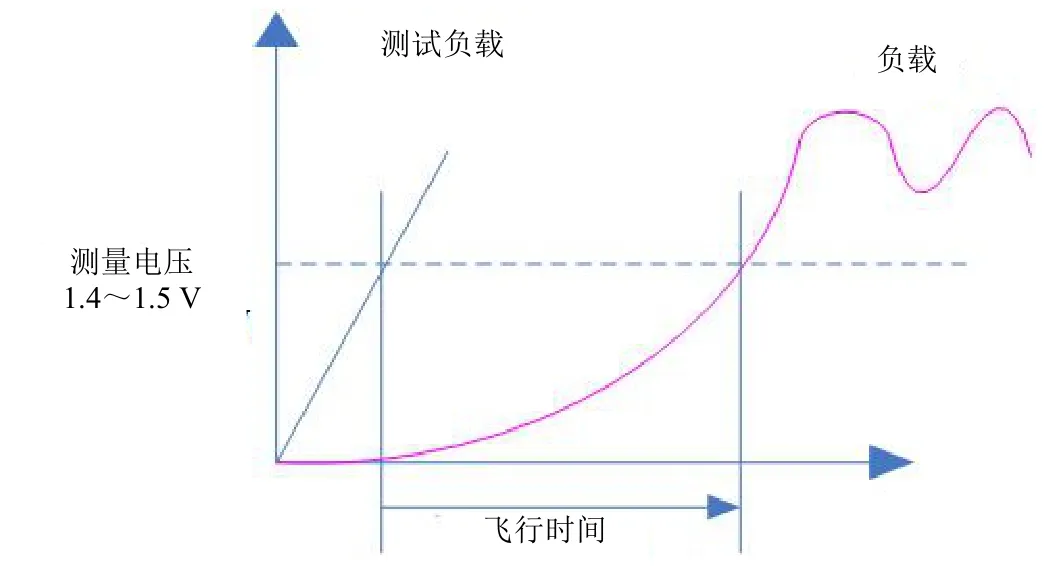

以上参数可以通过查驱动源、接收器、时钟驱动器的数据手册找到。所有的参数都得到后,就可以计算出最大飞行时间Tflt-max和最小飞行时间Tflt-min了。通过判断上面列出的Tmargin-fast和Tmargin-slow2 个条件就可以知道时序是否能满足。对于速度很高的网络或复杂拓扑,有时会难以同时满足slow、fast 条件,此时应保证满足slow 状态,fast 状态可适当放宽。此外,当时序不满足时,也可以通过调整PCB 走线来改变建立延时和开关延时。源同步方式是在送数据信号的同时提供时钟信号或锁存信号,比较常见的CPU(Central Processing Unit/Processor,中央处理器)外接SDRAM(Synchronous Dynamic Random-Access Memory,同步动态随机存储器)就是源同步方式。由于源同步方式中时钟始终在数据中间,这时就没有Tco的概念,而是使用输出的setup 和hold 参数来表示时钟和数据的相位关系。由于芯片输出时已经保证了setup 和hold time,那么设计时主要是要保证时钟到达接收端后,也满足接收芯片的setup 和hold 时间要求,发送和接收的2 个采样窗口能够匹配(最好在中间),那么时序就满足了。首先要通过仿真分别得到时钟和数据的飞行时间(从驱动源到接收端总的延时时间),飞行时间的含义和测量方法如图6 所示。

图6 飞行时间的含义和测量方法

时钟和数据线的飞行时间分别表示为Tflt-clk(时钟线飞行时间)和Tflt-data(数据线飞行时间),首先定义一下方向:若Tflt-clk>Tflt-data,则Tclk-data-skew(时钟线和数据线之间的时间偏差)=Tflt-clk-Tflt-data,为正。

时序计算公式如下:

式中:Tsu-out为输出的建立时间的数值;Tsu-in为输入的建立时间的数值;Thd-out为输出的保持时间的数值;Thd-in为输入的保持时间的数值。

即Tclk-data-skew=[(Thd-out-Thd-in)-(Tsu-out-Tsu-in)]/2。

通过调节时钟和数据之间的偏移量Tclk-data-skew,可以将采样窗口正好落在数据中间。

2.3 拓扑结构仿真

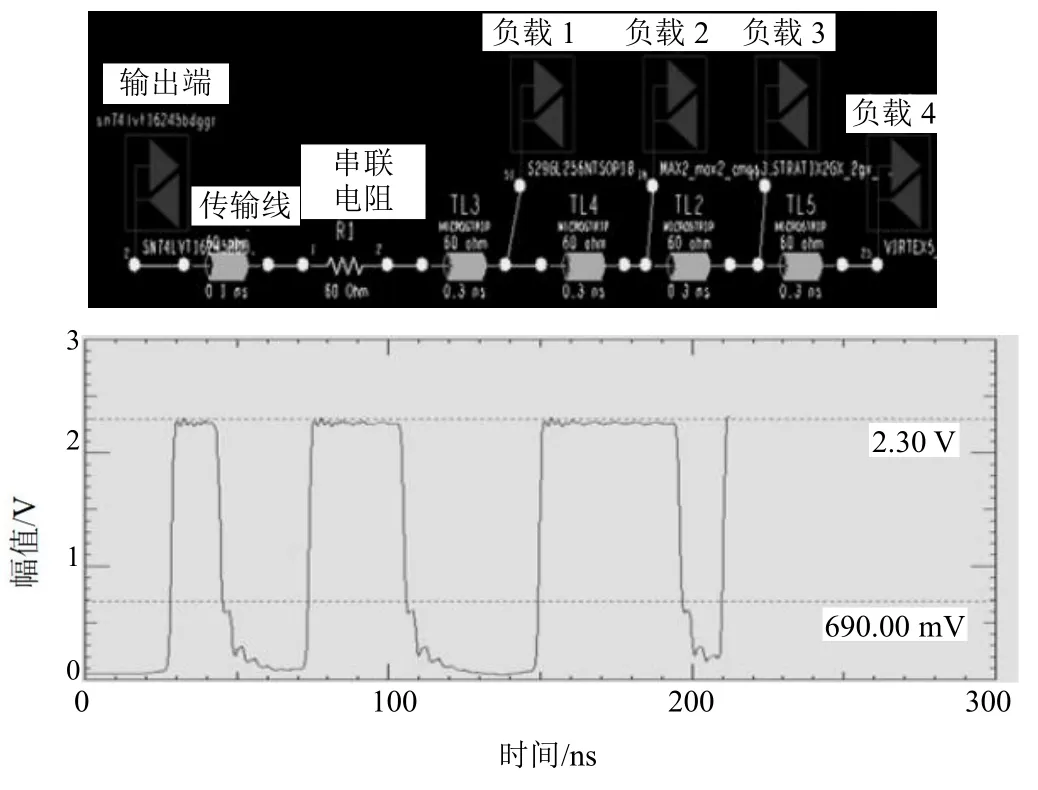

当一个驱动源驱动多路负载时必须选用合适的拓扑结构以达到最佳的传输效果。常见的点到多点的拓扑结构有树状拓扑结构、菊花链拓扑结构、星型拓扑结构[3]。树状拓扑适合接收器比较多而分散的场合,但每次分支的数量尽量小于3,否则阻抗匹配不好做。给每条分支都加源端串连电阻,阻值大小根据仿真结果选定。这种结构的好处是分支等长的限制可适当放松。树状拓扑需要驱动源的驱动能力比较强,带的负载少。菊花链拓扑结构需要布局时负载间隔均衡放置,比如CPU 和外部SDRAM 之间的总线可以采用这种方式。在源端加串连匹配电阻可以显著改善接收端的波形。星型拓扑也要求负载均匀放置、传输线等长、适合驱动器居中、负载均匀分布在外围圆周上的布局。在源端加一个串连匹配电阻。数据线或者地址线常常有一个驱动带多个负载的情况,由于数据或者地址线一般都很多,不可能为一根线加三四个电阻,一般情况是在源端加一个匹配电阻,所以一般采用菊花链或者星型拓扑结构。图7 为66 M 频率的数据线一驱四采用菊花链拓扑的例子,仿真得到的波形过冲很小,有轻微振荡现象,总的来说符合设计要求。

图7 菊花链拓扑结构下仿真波形

3 结束语

运用SigXplorer 设计工具进行系统级前仿真可以验证设计方案的可实现性,根据设计对SI(信号完整性)与时序的要求来选择关键元器件,优化系统时钟网络及系统各部分的延迟、选择合理的拓扑结构,调整PCB 的元器件布局、确定重要网络的端接方案。力争在设计阶段解决潜在的问题,减少单板改板的次数,从而降低成本,缩短研发周期。