面向设计加固的航天集成电路辐射效应评估方法研究与实践

2023-08-31郑宏超赵元富

郑宏超 王 亮 李 哲 郭 刚 赵元富

1(北京微电子技术研究所 北京 100076)

2(中国航天科技集团有限公司抗辐射集成电路技术实验室 北京 100076)

3(中国原子能科学研究院核物理所 北京 102413)

航天器电子系统上的集成电路在空间环境中产生单粒子、总剂量和位移损伤等辐射效应,随着半导体工艺进步,器件特征尺寸减小,单粒子效应已经逐渐成为影响航天器电子系统的最主要辐射效应。低轨卫星因单粒子效应导致工作异常的比重达到68.9%[1],2012 年,美国洛斯阿拉莫斯实验室对某卫星的现场可编程门阵列(Field Programmable Gate Array,FPGA)进行在轨观测,平均每天发生14.4 次单粒子事件,严重影响了卫星的正常工作和飞行安全[2]。

单粒子效应是由于单个质子或重离子穿过集成电路,以直接电离、核反应或弹性碰撞产生的二次粒子的方式,在径迹上产生电荷沉积,引发电路工作异常[3]。根据效应结果可以分为两类:一类是使得数字逻辑状态或者模拟信号发生变化的“功能性”错误,例如单粒子翻转(Single Event Upset,SEU)、单粒子瞬态(Single Event Transient,SET)、单粒子功能中断等;一类是在寄生晶体管形成的瞬时导电通道导致闩锁或烧毁的“电学类”错误,例如单粒子闩锁、单粒子烧毁、单粒子栅穿等。

目前,集成电路针对单粒子效应的加固方法主要有屏蔽加固、工艺加固和设计加固三种方式。屏蔽加固通过包覆材料来吸收和阻挡辐射,可以降低电子和质子辐射,但不适用于重离子单粒子加固[4];工艺加固通过专用工艺或在标准工艺线上进行调整,可以不损失常态性能下实现加固但成本较高[5-6];设计加固是在标准商用工艺线上,通过版图级、电路级和系统级等不同设计层级进行加固[7],通过时间和空间冗余等方式降低单粒子效应的发生概率,在有效提高单粒子加固能力的同时成本较低,缺点是需要带来芯片面积和功耗的额外开销。与美国主要依靠工艺加固实现航天集成电路设计不同,国内的抗辐射工艺水平与国外存在着较大代差,无法满足日益复杂的航天任务需求,但国内商用工艺线与国外抗辐射工艺线代差较小,因此,北京微电子技术研究所团队(以下简称“团队”)在国内率先提出了采用设计加固的技术路线,基于商用工艺来实现航天集成电路自主可控,建立了标准单元库和端口库,以及锁相环、存储器(Static Random Access Memory,SRAM)、高速接口等IP,构建了超深亚微米和纳米级抗辐射加固集成电路研制平台[8]。制定设计加固方案的前提,是掌握辐射效应尤其是单粒子效应的规律和损伤机理,而基于单粒子地面模拟装置的重离子试验及评估方法,是实现设计加固的关键保障。

国内集成电路单粒子性能评估一般在北京串列加速器核物理国家实验室HI-13终端或兰州重离子加速器国家实验室TR5 终端上开展辐射试验,以获取目标电路的单粒子错误截面和线性能量传输(Linear Energy Transfer,LET)阈值,并根据空间轨道、环境模型和敏感体模型预估单粒子在轨错误率。已有的单粒子试验行业标准只规定了一般流程步骤,并未根据电路类型给出具体的测试方法,随着工艺进步,高速信号、内嵌大容量存储、片上系统等复杂电路需要探索新的试验方法和测试技术,通过试验手段为抗辐射加固技术提供基础信息。

本文通过总结团队十余年的技术攻关历程,列举了在抗辐射设计上提出的单粒子加固技术,阐述了基于国内加速器开展的航天集成电路辐射效应评估方法和测试技术研究成果,并给出了研究结论。

1 集成电路单粒子加固设计技术实例

集成电路抗单粒子加固设计在版图级可采用阱区保护环、版图分离布局等版图结构提高单粒子锁定加固能力,降低单粒子多位翻转(Multiple Bit Upset,MBU)和单粒子多单元翻转(Multiple Cell Upset,MCU)发生概率;在电路级可采用时空冗余(如DICE(Dual Interlocked CELL))等加固结构提高SET 和SEU 加固能力;在系统级加固包括纠检错编码、三模冗余等。随着纳米工艺进步,通过单粒子试验发现,上述传统加固方法难以有效加固SET、MBU、MCU,为此,团队针对翻转敏感的存储类单元(如触发器和存储器)提出了改进型优化设计。

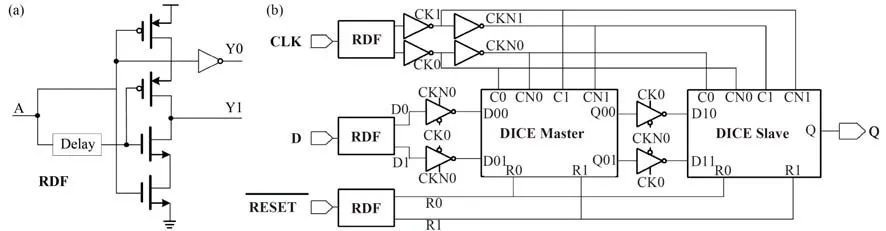

1.1 单粒子加固设计实例1—触发器设计加固

超大规模集成电路中组合逻辑电路比重大,最容易受单粒子效应影响产生SET,并且传递到时序单元(如触发器)使得电路功能异常。冗余延迟滤波(Redundant Delay Filter,RDF)是一种常见滤除外来SET 的结构,如图1(a)所示,但辐射试验结果表明,在纳米工艺尺寸减小、电路规模增大、工作频率增加等条件下,仍存在较大的SET被捕获概率。

图1 RDFD结构触发器Fig.1 RDFD-DFF structure

团队设计了一种基于RDF和双DICE相结合的抗SEU和SET触发器电路新结构RDFD(Redundant Delay Filter DICE)[9],如图1(b)所示。采用DICE结构提高抗SEU阈值,利用RDF使得前端引入的SET在双独立输出下不同步,无法改写双模冗余的DICE锁存器,从而大幅减少触发器捕获SET概率。

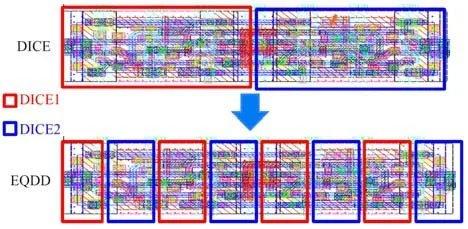

1.2 单粒子加固设计实例2——存储器设计加固

存储器是超大规模集成电路中存储指令或执行运算的关键单元,DICE结构是电路级常用的存储器抗SEU 加固方法,其弱点是存在SEU 敏感节点对。随着工艺进步,单粒子电荷共享作用范围有可能同时覆盖敏感节点对,或者在离子倾斜入射时覆盖,因此在单元版图设计时应该对敏感节点对合理布局。

团队提出了双DICE 交叉(Error Quenching Double DICE,EQDD)存储单元版图加固技术[10],利用同一个DICE 单元的非敏感节点之间电荷共享湮灭效应(Error Quenching)来减小SET 影响范围,再通过相邻两个DICE单元进行交叉版图设计,如图2所示,将同一个DICE 内的两个敏感节点间距拉大,在不增加整体存储器版图面积的情况下,有效降低了DICE 敏感节点对发生SEU 的概率,抗MBU、MCU的能力均得到提高。

图2 EQDD存储单元版图Fig.2 EQDD method layout

2 单粒子效应评估方法

团队在抗辐射加固设计平台上先后研制了多核处理器(Central Processing Unit,CPU)、千万门级专用集成电路(Application Specific Integrated Circuit,ASIC)、吉赫兹高速高精度模数转换器(Analog Digital Converter,ADC)、高速总线(BUS)等前沿领域航天集成电路,对先进工艺集成电路、高速电路、复杂芯片的评估是获取辐射效应规律和有效评估产品抗辐射能力的关键。为此,经过多年攻关和探索,团队提出了一些新工艺、新结构、新效应的单粒子评估试验方法。

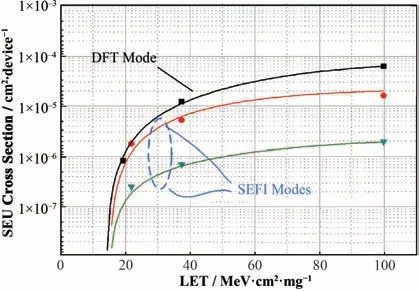

2.1 复杂大规模电路单粒子软错误评估方法

CPU、ASIC等复杂大规模电路拥有多种工作模式和测试向量,如果通过穷举遍历所有模式进行辐射试验评估,每款电路所需单粒子机时在100 h 以上,不仅无法实现且试验效率低下,需要找到一种可以表征电路单粒子最劣工作模式进行试验评估。

团队在2008 年首次利用可测性设计(Design For Test,DFT)进行复杂大规模电路单粒子软错误性能评估,假定任一存储单元发生的SEU必将导致电路发生功能中断,通过这一保守估计的方式获取复杂电路的单粒子软错误性能指标。常用的内建可测性设计一般包括触发器扫描链和存储器功能自测(Memory Built In Self Test,MBIST)两种模式,某型ASIC 的可测性和不同功能模式下的单粒子错误威布尔曲线如图3 所示,图中DFT 模式下单粒子错误截面更加保守,可以表征复杂电路最劣工作模式下单粒子软错误。

图3 可测性和功能模式下单粒子威布尔曲线Fig.3 DFT and function mode SEE Weibull curve

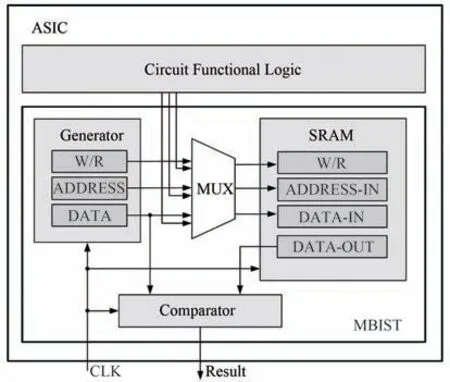

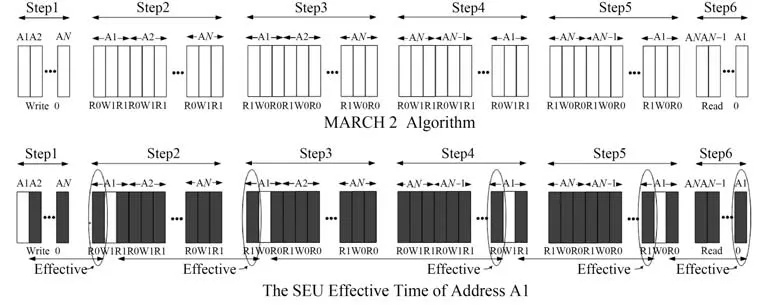

MBIST 法利用多路选择器(Multiplexer,MUX)将ASIC 由功能模式转为DFT 模式,可以检测内部所有SRAM 发生的SEU。 通过激励发生器(Generator)模拟SRAM 的写、读过程,通过比较器(Comparator)判断是否发生软错误,如图4所示。由于写入数据将覆盖发生的SEU 造成错误丢失,因此,团队提出了一种有效辐照注量计算方法,如图5所示[11],对于SRAM 每个地址,在每两次写操作之间,第一次写操作与最后一次读操作之间的时间长度为SEU有效辐照时间,通过统计所有SRAM地址的有效辐照时间之和,其占总辐照时间的比重(η),将辐照总注量(φT)乘以η即得到SRAM有效辐照总注量(φE),还需要对目标电路增加额外辐照注量(φT-φE),才能实现对SEU 的校准,解决了MBIST 法在SEU测试的准确性问题。

图4 MBIST可测性设计结构Fig.4 MBIST structure

图5 MBIST算法单粒子有效辐照时间示意Fig.5 SEE effective irradiation time based on the MBIST algorithm

2.2 高速信号单粒子评估方法

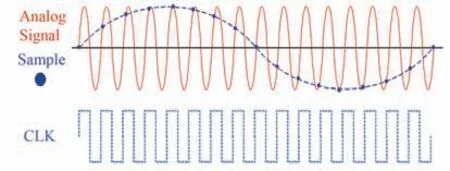

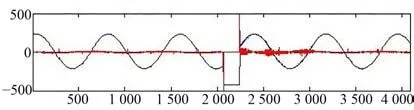

新一代通信卫星在轨获取的海量数据信息需要实时处理,吉赫兹ADC、总线控制器的高速信号需要进行单粒子试验评估,主要分为并行和串行两类信号。高速并行信号通常采用静态或者低速动态模式下进行,无法覆盖高速满量程电压的输出码型,团队在2012 年提出了一种基于折叠内插式的高速信号单粒子翻转分析技术[12],通过提供一定频率差的高频输入信号和时钟信号,输出获得低频信号满量程采样矩阵,如图6 所示,同时利用双FIFO 高速缓存实现了SEU 连续处理,捕获的SEU 图形如图7所示。

图6 基于频率差的满量程测试方法Fig.6 Full scale test method based on the beat frequency

图7 捕获的高速信号SEUFig.7 SEU captured in high-speed signals

高速串行信号常用于总线数据传输中,容易受到SEFI 和SEU 影响,在接收端将产生多种类型误码。单粒子误码率是高速串行信号的一项重要指标,传统统计方法是直接对比码型,容易产生误判影响准确性,团队在2018年提出了一种分类统计中断和翻转单粒子误码率的算法[13],如式(1)所示,其中FER 和UER 分别为单粒子中断和翻转的在轨错误率,TRST为系统复位时间对应码数。

FER根据不可恢复的单粒子功能中断数进行计算,UER涵盖了单位码错(S1)、多位码错(S2)、自恢复错误(S3)三类翻转,SEU 误码数计算如式(2)所示,其中Tbrust为自恢复时间对应码数。

2.3 倒装焊封装电路单粒子评估方法

随着航天电路主频和端口数量的增加,具有高密度、高性能、高可靠的特点的倒装焊封装也广泛应用于CPU、FPGA、ASIC等先进电路。倒装焊电路的衬底厚度普遍大于数百微米,中低能加速器产生的重离子射程一般无法穿透衬底进行试验,国外采用高能加速器产生10 GeV 以上超高能量重离子的方法来将增加射程并降低离子LET值,从而穿透倒装焊电路。国内高能加速器机时紧张无法满足大批量电路试验,团队经过多年探索提出了一种基于中低能加速器的倒装焊电路单粒子试验流程方法。

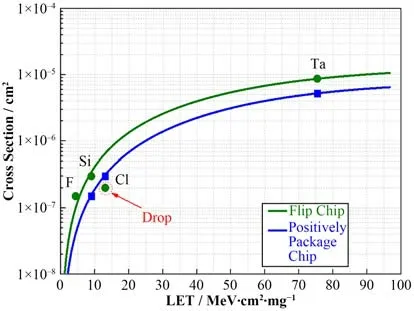

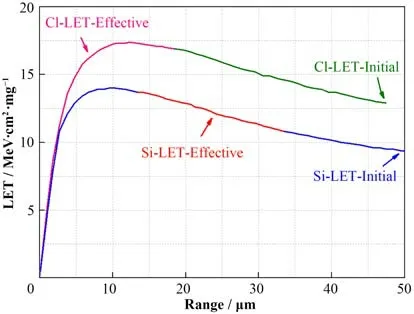

倒装焊电路在单粒子试验前需要进行衬底减薄,控制衬底厚度,然后计算离子到达芯片有源区的有效LET值,确保穿透有源区的全过程处于布拉格峰右侧,以保证试验准确性。图8 为两款相同工艺不同封装形式的ASIC 电路SEU 截面图,图中氯离子(Cl)辐照倒装焊电路后SEU 截面比硅离子(Si)小,原因是Cl离子入射后的有效LET值跨越了布拉格峰左侧,而Si 离子的有效LET 值仍在右侧比Cl大,如图9所示。

图8 Cl离子入射倒装焊电路SEU截面突降Fig.8 SEU drop in a flip-chip circuit by a Cl ion

图9 Cl和Si离子入射倒装焊电路的有效LETFig.9 Effective LET of Cl and Si in a flip-chip circuit

2.4 质子单粒子评估方法

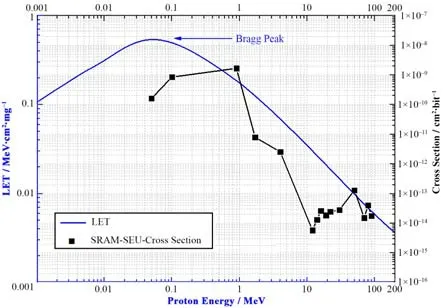

质子在Si 中直接电离的最大LET 值约为0.538 MeV·cm2·mg-1[14],难以对加固集成电路产生影响,但质子与靶材料发生核反应,产生次级重离子LET 值 可 达14 MeV·cm2·mg-1(与 硅),甚 至37 MeV·cm2·mg-1(与钨),考虑到纳米集成电路单粒子软错误LET阈值普遍较低,因此质子单粒子效应的影响不可忽略。在中国原子能科学研究院中能质子单粒子试验终端建成以前,国内质子试验机时紧张,且能量不易调节,质子单粒子效应机理缺乏试验数据支撑和验证,也未形成试验方法标准,需要开展前期试验评估技术研究。2016年,团队在国内首次试验验证了纳米SRAM 可发生低能质子直接电离导致的SEU,发现非加固SRAM SEU截面形成了一个与布拉格峰类似的曲线,如图10 所示,经过与重离子试验对比分析,加固SRAM的质子SEU主要来源于核反应产生的次级重离子,如图11所示。

图10 非加固SRAM质子SEU截面Fig.10 Proton SEU CS of non-radiation-hardened SRAM

3 单粒子效应测试分析技术

为了提高单粒子试验效率和数据分析能力,团队还基于加速器开发了高效的试验系统装置,提出了新的试验数据分析方法。

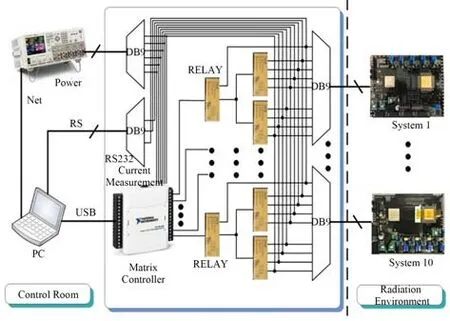

3.1 矩阵式自动测量控制系统

为了满足批量化单粒子试验高效测试需求,团队针对HI-13 开发了一套矩阵式自动测量控制系统[15],如图12所示。系统的核心是矩阵控制器和继电器矩阵网络,通过上位机程序可以实现不同测试系统的秒级切换,自动完成复位、测试、保存指令,并且实现供电系统和通讯链路的标准化,可以一次性控制最多30 套测试系统进行单粒子试验,在HI-13现场安装如图13 所示。在真空罐内同时装入了CPU、AISC、ADC、SRAM、BUS 等单粒子试验系统,通过平移台将每支电路依次对准辐照炮口,配合控制系统可以快速实现对不同电路的单粒子试验测试。

图12 矩阵式自动测量控制系统Fig.12 Auto-measurement-control matrix system

3.2 时域分析方法

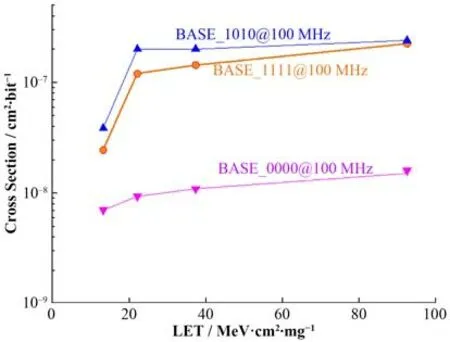

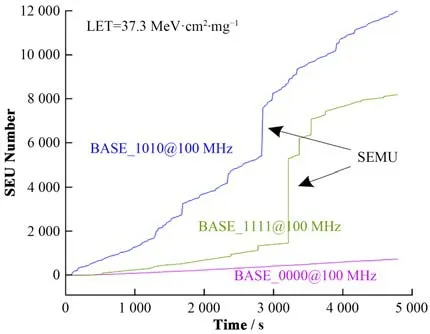

传统的单粒子试验数据处理方法是将SEU 截面绘制成威布尔曲线后进行分析,图14所示为一款工作在100 MHz 触发器电路,分别在“恒0”“恒1”“01 交替”三种码型下测得的单粒子威布尔曲线[9]。团队发现,不同模式下SEU数据异常,结果相差1个数量级,仅凭曲线无法区分SEU在时域上的分布特性,难以定位错误来源,团队提出了一种可以区分SEU 的时域分析方法,如图15 所示,在每个LET 值离子下,可以绘制SEU 错误数随试验时间变化曲线,图中“恒1”“01 交替”两种码型出现了明显的单次事件多位翻转(Single Event Multi Upset,SEMU)现象,表明单粒子事件发生在时钟树等全局信号模块,为设计师改进加固设计提供指导意见。

图14 触发器在不同码型下SEU截面Fig.14 SEU cross-section of DFF at different vectors

图15 SEU时域分析图Fig.15 SEU time-domain analysis diagram

4 结语

团队自2005 年首次在串列加速器开展单粒子试验,18 年来累计使用单粒子机时超过1 100 h,完成试验电路数量超500 款,为抗辐射加固设计技术研究提供了大量宝贵的试验数据支撑,提出了多项评估方法和测试分析技术,走出了一条有中国特色的集成电路设计加固技术路线,构建了完整的航天集成电路产品谱系,形成了为航天工程提供体系化芯片解决方案的能力,其中关键核心电路在轨多年运行正常,解决了困扰航天型号的单粒子故障难题,为空间飞行器的长期在轨稳定运行发挥了重要作用。

致谢感谢北京串列加速器核物理国家实验室、兰州重离子加速器国家实验室。

作者贡献声明郑宏超、王亮负责方法和调研;郑宏超、李哲负责系统和试验;郭刚、赵元富负责概念和指导。