双重图形拆分技术应用及国产化研究

2023-07-28付静

付 静

(上海国微芯集成电路有限公司,上海)

引言

长期以来,半导体技术一直遵循摩尔定律,即每18 个月,集成电路芯片晶体管密度翻倍,即:半导体工艺技术节点的关键尺寸(Critical Dimension),将以每18 个月,缩小至上一节点的70%左右。比如主流半导体制造商(包括Intel、三星和格罗方德等)的工艺节点,经历了180 nm、130 nm、90 nm、65 nm、45/40 nm、32/28 nm、20/22 nm 到14 nm 这一系列的高速发展过程[1]。随着工艺关键尺寸缩小,工艺挑战越来越大。主流的193 nm ArF 浸润式光刻机已无法直接曝光生产14 nm 工艺中的芯片最小图形尺寸。半导体制造商引入了自对准双重图形化技术(SADP,Self-Aligned Double Patterning)和双重图形拆分技术(DPT)来解决该问题;其中DPT 需要EDA 软件和工艺的完美结合,帮助14 nm 工艺制程顺利实现。

1 项目背景

近年来,因国际形势变化,美国、欧洲和日本等国逐渐加大对中国先进集成电路产业的限制,我国先进半导体技术路线也向双重或多重图形拆分技术偏移,以最大化利用深紫外(DUV)光刻机潜力。半导体核心技术的国产化,是破局国外技术禁运的关键。半导体制造设备及材料、EDA 是半导体产业链上游的三大方向;而DPT 是制造端EDA 的一个细分方向,也是14 nm 等先进工艺必备一环。因此,DPT 软件国产化至关重要。

2 双重图形拆分技术应用及国产化

14 nm 节点的关键版图层使用当前较为先进的深紫外(DUV)193 nm ArF 浸润式光刻机曝光。基于瑞利判据公式,其分辨率理论极限值在33.6 nm 的半周期(Half Pitch)[3]。实际应用中会略大,特征的全周期(Pitch)分辨率在72 nm 以上。

其中,k1为系统参数,λ 为光源波长,NA 为数值孔径[3]。

Intel 的14 nm 节点利用DUV 光刻机,可提供鳍层(Fin)全周期42 nm、关键金属层(Metal)52 nm 分辨率的工艺支持[4]。这首先归功于SADP 和DPT 的应用。工艺中利用SADP 技术,即侧墙生成工艺来辅助生成规则图形,比如鳍层(Fin);对于关键金属层,则利用DPT 技术在软件层面将单层金属版图拆分成两层,通过两次光刻工艺来实现更高分辨率。

DPT 软件有两大应用场景:

(1)用于14 nm 及更先进节点芯片设计的物理验证,负责检查该芯片设计是否满足双重图形拆分硬性要求,图1 展示了一个奇数环,它表示该处无法满足硬性规则进行拆分。

图1 奇数环Odd Loop

(2)芯片制造企业对版图层进行拆分,既要对违反光刻极限的图形拆分,也需对工艺不友好区域拆分。

2.1 双重图形拆分(DPT)软件架构与功能开发

2.1.1 严格规则拆分检查和违例反标

严格的拆分规则是芯片制造商(Foundry)定义的设计规则(DRC),通常认为满足一定条件(例如间距<50 nm)区域,必须可被拆分到两张版图;否则,这是一个奇数环违例[2]。对于需进行双重图形拆分的芯片设计,在芯片物理设计的放置(Place)和绕线(Route)阶段,会考虑双重图形拆分的严格规则;但还无法完全避免奇数环违例发生,这就需要在芯片物理验证阶段,引入双重图形拆分软件中的严格规则拆分检查和违例反标功能。该功能将违例区域反标回芯片原始设计。图2 为一个奇数环违例,芯片设计工程师可通过绕线(Route)合理修正来规避。

图2 双重图形拆分违例及修正

2.1.2 严格规则拆分和工艺友好规则拆分

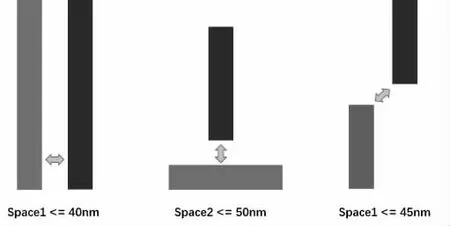

芯片制造商(Foundry)最为看重双重图形拆分软件的拆分功能。在14 nm 等工艺中,foundry 会将需使用双重光刻工艺(常见为LELE)的版图层,按一定规则拆分成两张光掩膜。此规则包含严格规则和后续工艺友好规则,这些规则主要与图形间距、形状有关。DPT 软件进行拆分时,首先必须确保满足严格规则条件的区域可被拆分。例如,常见的严格规则会包括以下三种[2],见图3。满足以下条件的图形,必须被拆分到两张不同图层。

图3 基于严格规则的拆分

除了严格规则,foundry 有一整套基于自身工艺特点的工艺友好拆分规则。这些规则通常比严格规则宽松,但需要DPT 软件能够尽可能多的去实现工艺友好规则拆分。图4 是针对通孔层(Via)的两组拆分结果,虽然均满足最严格的规则,但左边一组实现了应拆尽拆原则,对后续工艺更为友好。

图4 两组不同的拆分结果

2.2 双重图形拆分(DPT)软件实际应用与验证

完成双重图形拆分后,版图层将用EDA 软件进行光学临近效应修正(OPC),然后版图信息会被制造到两张光掩膜(Mask)。相关工程师会通过OPC 软件进行光刻工艺仿真,通过结果统计分析,评估双重图形拆分结果。DPT 软件能够尽可能高的覆盖并实现工艺友好规则的拆分,后续光刻工艺仿真检查到的不理想坏点(hotspot)则越少,最终良率越高。

芯片制造企业会通过DPT 软件拆分技术,来修正不理想的坏点。将坏点几何环境特征写入拆分规则,可在更早步骤中,较为彻底的避免该类问题,在实际中也获得了验证。例如,对于通孔层(Via)某些冗余Via 带来的拆分不理想区域,芯片制造商通常会考虑对局部冗余Via 做一定变化,并写入拆分规则,来解决该问题[5]。

3 难点问题与技术措施

3.1 拆分算法中引入工艺友好软规则

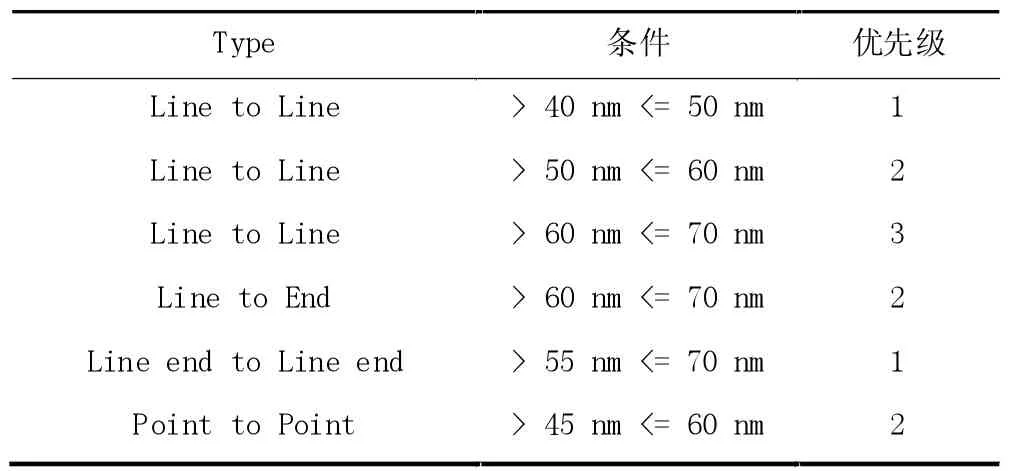

例如,严格拆分规则为边(Line)与边(Line)间距<=40 nm、边(Line)与线端(Line end)间距<=50 nm、线端与线端(有投影重合)间距<=55 nm、点与点间距<=45 nm;工艺友好软规则见表1;其中优先级1 表示拆分优先度最高,优先级3 表示拆分优先度较低。

表1 工艺友好规则示例

软规则拆分需要在严格拆分规则基础上再做计算求解。拆分软件应先确保严格拆分完成后,再根据优先级进行软规则拆分。软规则拆分时,需引入虚拟奇数环用于后续调整。虚拟奇数环是建立在软规则基础上的虚拟拆分违例,这类虚拟拆分违例在满足预设激发条件时,可对严格规则拆分结果重新着色,保证软规则拆分覆盖率。

3.2 内存和性能问题

超大规模求解图形着色问题的计算将会对硬件资源造成极大冲击,运算量极为巨大。在14 nm 节点的芯片设计中,一个版图层包含多边形数量超过十亿,更先进节点的大尺寸芯片,数量甚至为百亿级。DPT 软件拆分求解时,内存使用峰值超过2T,运行时间会超过上百小时。

解决内存消耗和计算量问题,将从两个方面出发:

(1)拆分算法优化。由于软规则带来了更多拆分限制,算法工程师需针对该问题进行更多的优化尝试。

(2)DPT 软件充分利用分布式运算模式。传统求解方法是将数据放在内存中利用多线程求解,但单台服务器内存及计算资源有限。通过对计算任务合理切分(Partition)及分发,利用分布式服务器加速计算,为目前主流EDA 软件发展趋势之一。

4 技术创新分析

DPT 软件开发过程中面临的诸多瓶颈,需要技术创新加以解决;而按照传统技术方向,需长时间的开发周期和技术积累,例如西门子EDA(Mentor Graphics)在层次化(Hierarchy)方向技术积累长达20年。

通常DPT 软件在做拆分求解时,难以充分利用分布式服务器,原因是拆分的求解需考虑全局数据才能给出最优解,局部拆分结果并不完全准确。然而,利用局部结果并引入新算法拆分校正,可迅速生成合理的拆分求解。该算法对于降低内存和运算时间有显著帮助。

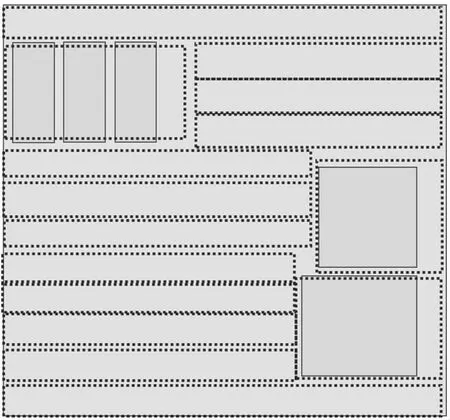

局部数据切分(Partition)方式也直接影响了DPT软件性能。结合芯片设计特点,采取模块抽取及一维切分方式,可大幅降低后续模块计算压力。此切分方式示例见图5。

图5 模块抽取及一维切分

结束语

基于工业界的实际应用,DPT 技术架构和功能经过了严谨论证、详细布局与高质量验证,最终产品可解决先进半导体工艺对双重图形拆分需求,同时也打破了国外在该细分领域对国内的限制。DPT 对于MPT技术开发的算法、内存管理方面也有许多启示。