复合电应力对芯片使用可靠性的影响分析

2023-06-29刘一杉周亮黄炜

刘一杉,周亮,黄炜

(中国电子科技集团公司 第二十四研究所,重庆 400060)

引言

随着集成电路芯片设计、工艺的快速发展,集成电路的晶体管特征尺寸不断缩小,实际芯片生产工艺中与理想情况存在差异,以及实际工作环境中器件工作条件与理想情况存在差异,使得集成电路芯片的抗电应力冲击能力越来越弱。许多抗电应力冲击能力较低的产品,在制造生产、运输贮存、实际应用过程中因静电而导致的失效越来越多,不仅提高了成本,更降低了产品可靠性[1]。

目前关于单应力环境下器件使用可靠性的研究居多,但集成电路芯片的使用的环境越来越多样化和恶劣,在多重复合电应力同时存在时,器件的长期使用可靠性进一步降低,极大的限制了集成电路芯片的使用寿命,而关于多重复合应力下器件的使用可靠性的相关研究极少,尤其缺少针对具体集成电路芯片产品的在多重复合应力下的实际故障案例,为集成电路可靠性的评价,典型故障模式的判断带来困难。

本文选取大规模集成电路波控专用芯片的故障为典型案例,对其多重复合电应力下的故障模式进行分析,分析产品经历单电应力与多重复合电应力下芯片可靠性的影响。

1 失效案例

从集成电路芯片失效机理进行概括,其电应力损伤,可分为电压及电流两类。电压失效如静电击穿栅氧化层;电流失效如过流导致的电阻烧坏,PN 结的损伤,金属/多晶硅互连线烧坏等[2]。

主要受金属线(铝线)以及多晶硅宽度、结面积大小、接触孔尺寸、以及芯片中电流走势的分布等,电应力冲击所产生的局部焦耳热也可能烧坏金属/多晶硅的连线或电阻。互连线的电流携带能力,可以表征为与其截面积相关的函数。除截面积外,同时也与热栅、聚集电流、台阶覆盖等因数相关。因此,在芯片氧化层台阶处,一旦受到脉冲大电流冲击,其铝层横截面积不足以承受,则有更大的几率发生熔融、开路,致使器件功能失效[3]。

通常根据产品的具体故障现象,可初步推测出其故障原因,但目前关于多重复合应力的分析数据极少,实际案例更少,极大的增加了该类故障案例分析难度。

本次选取某款专用芯片产品故障案例开展复合电应力对芯片可靠性的影响分析,该款芯片主要用于数据转换,其功能框图如图1 所示,数据分别在LCK 和BG 上升沿存储在一级锁存器和二级锁存器中,结合TRR1 和TRR2 输入信号进行二选一等组合逻辑操作,得到并行输出控制信号U12~U1、W12~W1、V4~V1。在LD 和CLK 信号的控制下,电路通过ZTO 单元将二选一结果进行并串转换输出。此外,电路内部还集成有欠压保护单元,负责对负电源电压进行检测,在欠压状态时输出指示信号,将TR1 和TR2 输出置为固定低电平。

图1 专用芯片功能框图

该款专用芯片器件规模大,在组件上使用过程中表现出正电源电流异常为15 mA,正常约为7 mA;ZTO 高电平异常为0.4 V,正常约为3.3 V;ZTO 端口对地阻抗异常为4.6 Ω,正常约为25 MΩ故障现象。

1.1 故障定位

1.1.1 内部目检

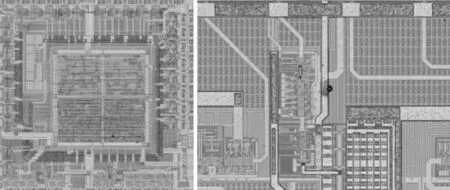

采用光学显微镜对该只故障件进行内部目检,发现其内部某SO 单元GND 铝线处存在异常烧毁痕迹,如图2 所示。

图2 故障件内部目检形貌

由图1 器件功能框图可知,器件的SO 单元与ZTO 单元为两个独立的单元,本次内部目检结果即SO 单元内部器件处存在烧毁与故障件前序端口阻抗测试结果即ZTO 端口对地阻抗异常为4.6 Ω不一致,为导致该故障现象的原因分析带来了阻碍。

1.1.2 OBIRCH 定位

考虑故障件ZTO 端口对地阻抗异常为4.6 Ω,与前序内部目检结果不一致,因此采用OBIRCH(Optical Beam Induced Resistance Change)方法定位故障点,即激光热效应激励电阻变化技术。

使用OBIRCH 技术,在出现故障的专用芯片两端施加恒定直流电压V,监测此时的电流I。随后将波长 1 340 nm 的激光束打在需要排查的芯片表面,逐区域依次加热。激光照射的部分会出现温度升高,故障处的电阻R 会随之变化,在V 恒定的条件下,,相应的I 同步变化。如此就能通过对电流变化的监测,达到定位集成电路中漏电流点以及半导体材料异常点,通常即是缺陷所在[4]。

检测结果显示故障件ZTO 与地间NMOS管处存在异常,如图3 所示。

图3 故障件OBIRCH 定位结果

1.1.3 故障定位结果

故障芯片存在两个故障点,分别为SO 单元GND铝线烧毁,ZTO对地输出NMOS管损伤。

1.2 原因分析及试验验证

本次故障件两处故障形貌无直接关联,如图4 所示,且SO 单元GND 铝线烧毁部位处于铝线中段,烧毁部位前后无特殊设计,例如过孔、台阶、铝线交叠等情况,如图2 所示,与常规单一电应力对器件的影响不一致,给本次故障原因的分析带来了较大困难。

图4 两处故障点关联性

前期针对该类故障现象,进行了多类型验证试验,包括不同幅度、脉宽、施加形式的电应力作用,并对试验后样品进行长期可靠性评价,但均未模拟出图2 所示故障形貌,表明单一应力作用下的故障模式与本次故障件并非相同。

考虑器件应用过程中存在多重应力叠加的过程,选取样品开展多重应力下可靠性评估。

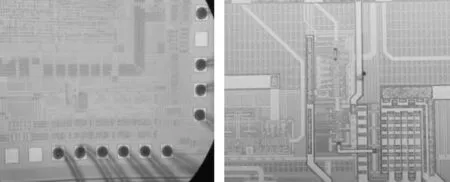

经过对多只样品开展HBM、MM、CDM不同模式ESD;不同幅度、脉宽、施加形式EOS 试验后,在进行MM 静电试验后叠加进行上电多次小幅度EOS 测试试验后复现处类似故障现象,如图5所示。

图5 复合电力试验后样品形貌

其中集成电路芯片遭受的ESD 应力可能来源于前期贴装等过程,由于ESD 损伤程度较弱,对器件功能可能不会存在致命性影响,但经历后期叠加上电多次测试,原本损伤的部位长期可靠性存在问题,导致其出现明显的烧毁痕迹,芯片表征出最终的功能性异常。

在静电应力和过电应力作用下,芯片内部器件存在一定的损伤,电应力施加后在相关铝线上产生过流,同时先进的金属系统要求更小的金属线宽,较大的电流密度可使金属连线移动升至穿过接触,过量的热量还可通过硅融化或破裂使得器件发生物理损坏,将影响产品功能及可靠性。

2 结论

集成电路芯片在使用过程中可能会遭受多种复合应力,例如温度应力、电应力、机械应力、温度循环应力、湿度应力等,实际的使用环境复杂多变,通常并非单一应力的影响,因此在进行集成电路故障分析或长期使用可靠性评价时,需结合器件特点及使用环境,开展多重复合应力下影响的分析。

针对多重复合应力下集成电路芯片长期使用可靠性的研究及现象分析对其正确合理的使用具有重要支撑作用。