集成电路设计与EDA技术课程专业能力培养实践

2023-06-22杨怡雯曾梓萱赵岩李长庚

杨怡雯 曾梓萱 赵岩 李长庚

摘 要:Verilog HDL作为描述数字电路的通用语言,在大规模设计中一般采用层次化和结构化的设计方法。为了在获得较优的电路面积结果的同时提高综合后输出网表的可读性,使用Python和正则表达式对Verilog代码进行层次化展平处理,用模块内的设计代码替换实例化语句。打平层次结构后,设计代码变为没有层次的、不带参数、不带可选择配置的扁平链式结构,提高了代码的可维护性。此实践项目难度适中,有助于学生深入理解Verilog HDL的语法结构和EDA软件的工作原理,提高了学生的设计实践能力。

关键词:正则表达式;Python;代码扁平化;课程教学

中图分类号:TP39;G434 文献标识码:A 文章编号:2096-4706(2023)02-0171-04

Integrated Circuit Design and EDA Technology Course Professional Ability Training Practice

—RTL Design Hierarchical Flattening Processing

YANG Yiwen, ZENG Zixuan, ZHAO Yan, LI Changgeng

(School of Physics and Electronics, Central South University, Changsha 410083, China)

Abstract: As a general language for describing digital circuits, Verilog HDL generally adopts hierarchical and structured design methods in large-scale designs. In order to obtain better circuit area results while improving the readability of the synthesized output netlist, Python and regular expressions are used to hierarchically flatten the Verilog code, replacing instantiated statements with in-module design code. After flattening the hierarchical structure, the design code became a flat chain structure without hierarchy, parameters, optional configuration, which improves the maintainability of the code. The difficulty of this practice project is moderate, which helps students to deep understand the grammatical structure of Verilog HDL and the working principle of EDA software, and improves students' design practice ability.

Keywords: regular expression; Python; code flattening; course teaching

0 引 言

電子设计自动化(Electronic Design Automation, EDA)是现代电子系统设计有效的工具[1]。随着设计规模越来越大,集成电路尤其是大规模数字集成电路的设计过程不仅包含逻辑和电路设计,其所采用的半定制电路设计方法也高度依赖EDA设计工具和设计流程来保证设计的正确性。EDA技术与集成电路相辅相成,先进的EDA技术可以设计大规模的集成电路,而大规模的集成电路则又支持更先进的EDA技术开发,两者在数字化和智能化的现代电子系统开发中起着支撑作用[2]。EDA技术应用充分体现了数字电子设计中自顶向下的演绎过程[3],充分理解软件工具的行为,有助于提高学生的设计实践能力。在专用集成电路设计课程的教学中,作者组织学有余力的同学参与科研项目,使用Python完成了EDA工具中读入RTL代码时的一个预处理功能——层次化设计的展平处理。

对于较大规模的设计,一般采用层次化和结构化的设计方法。这种设计方法可以很好地维持设计边界和层次,符合人的思维方式并利于复用代码。但是EDA逻辑综合工具在把RTL描述转换为门级网表的时候,会以每一个模块的边界作为默认的逻辑优化边界,模块划分过小或者层次过多的时候,不能获得最优的电路面积结果。若在综合命令中加入“-flat”选项,综合工具会将所选择的层次结构打平后再进行优化,在获得较优的面积结果的同时,输出网表的可读性较差,会给调试工作带来不便。

硬件描述语言(HDL)是一种用形式化方法来描述数字电路和设计数字逻辑系统的语言[4]。由于绝大多数的数字集成电路设计以及FPGA设计都以VerilogHDL的代码为载体,本文针对Verilog HDL语法,在层次化结构的展平处理中,主要完成以下内容:用模块内的设计代码替换实例化语句,主要是模块内代码信号的唯一化和输入输出的替换操作;对于带有parameter的参数化设计,将实例化时的参数变成没有参数的设计;对于带有generate的可配置化设计,实例化时从可配置的代码中选择代码进行提取;对于带有define和ifdef的宏定义参数,判断决定代码保留。经层次结构打平后,代码使用扁平的链式结构。

1 处理对象及工具

“模块”是Verilog的基本设计单元,在一个模块中引用另一个模块,对其端口进行关联,叫作模块的例化。在一个顶层设计中实例化子模块电路,类似于编程中在主函数调用子函数。模块的例化建立了描述的层次,一个复杂的电路往往通过模块嵌套形成了复杂的层次结构。而去层次化则类似于编程中将用调用函数实现的代码转换为不用函数,而是直接在主程序中实现各个函数的内部代码。经过去层次化后,设计代码变为打平的、没有层次的、不带参数、不带可选择配置的代码。在Python中,re模块就是一个用于处理正则表达式的模块[5]。鉴于Python强大的文本处理能力,本文采用Python和正则表达式对Verilog HDL代码的文本进行处理。

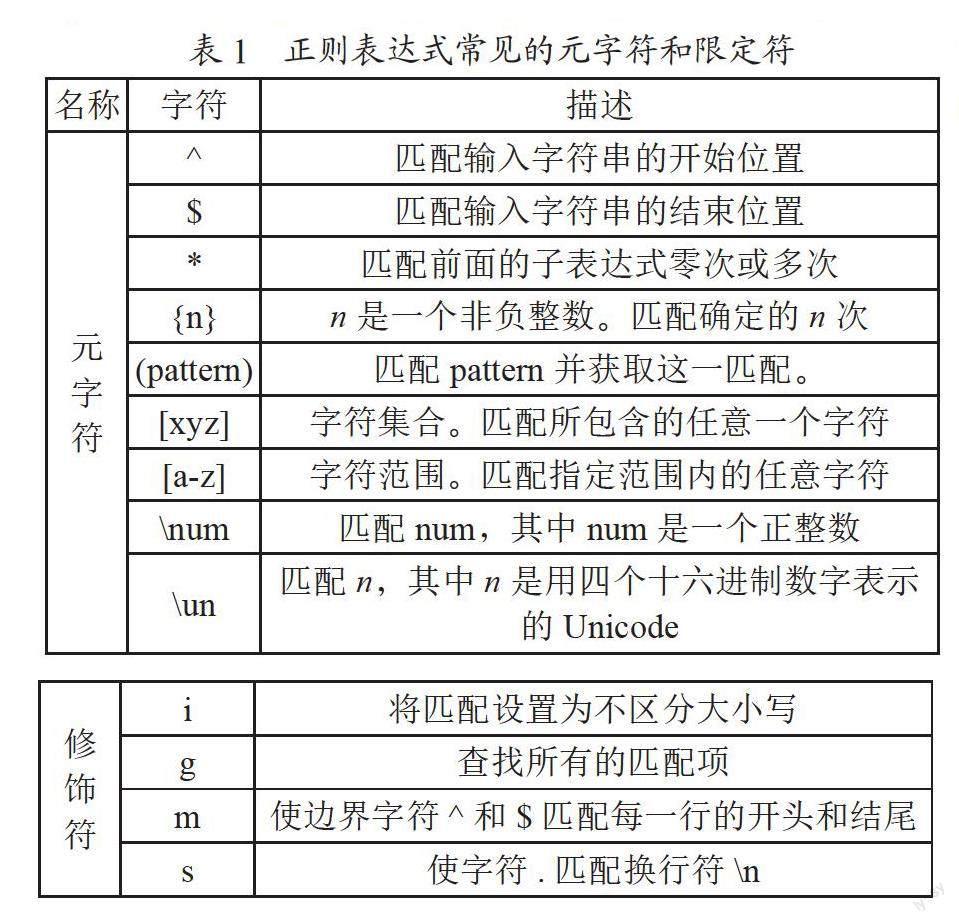

正则表达式被提出时,主要用于描述正则集代数。它是提供计算机操作和检验所要抽取的字符串数据的一种强大的工具,是一串由特定意义的字符组成的字符串,提供了一种从字符集合中搜寻特定字符串的规则。正则表达式可以运用于多种操作系统中,目前很多计算机语言都支持正则表达式匹配,如C++、PHP、Java等。

正则表达式最基本的3种功能包括匹配、替换和提取。匹配功能用于判断文本里面是否有符合要求的字符,将不同的字符按照匹配内容的不同进行分组,如在此项目实践中将宏定义的标识符和内容根据“`”符号区分。替换功能用于在文档中使用匹配模式来标识特定文字,然后进行删除或进行替换,如删除注释、端口名和参数声明名称的替换、generate语句中带有$符号的标识符和begin/end语句的替换。提取功能用于从字符串中提取子字符串,如获取需要的变量名称、模块名称、判断语句、模块内容等。Verilog继承了C语言的多种操作符和结构,其本身就是一系列字符串组成的文本,在信息抽取的过程中完全适应正则表达式的特点。

正则表达式由普通字符和特殊字符组成,在正则表达式中,可以用方括号括起若干个字符来表示一个元字符(特殊字符)。同时正则表达式支持限定符的概念。限定符指定输入中必须存在字符、组或字符类的多少实例才能找到匹配项,这些限定符可以指定正则表达式的一个给定组间需要出现多少词才能满足匹配,因而可以适应一些不确定情况[6]。正则表达式常见的元字符和限定符如表1所示。

2 处理和实现过程

2.1 方法总述

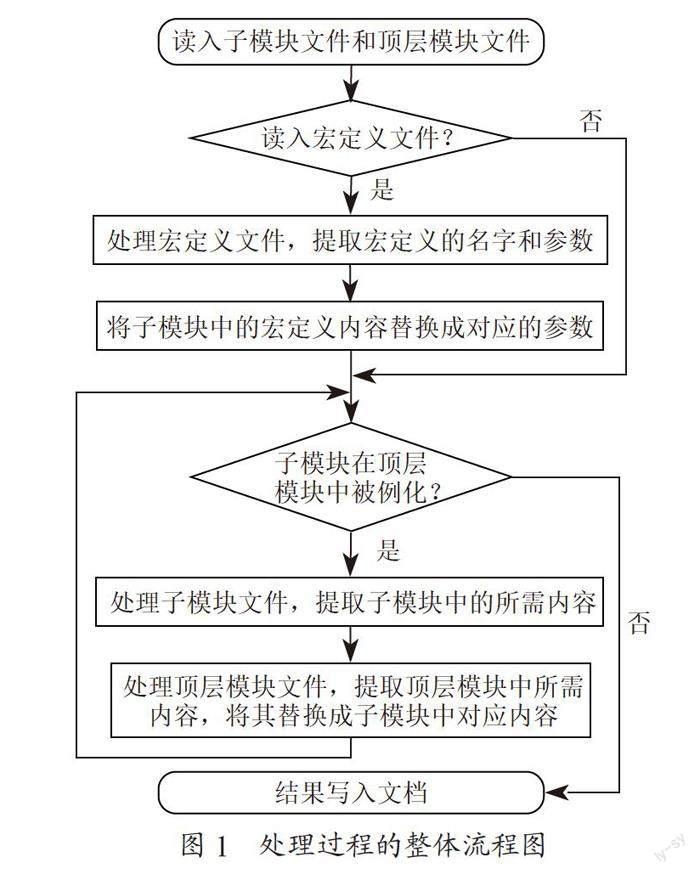

首先读入顶层模块文件和子模块文件。如有宏定义文件,则对宏定义文件先进行处理,提取宏定义的名字和参数,在子模块中进行名字和参数的替换。对于每一个读入的子模块文件,若该子模块在顶层模块中被例化,则对子模块文件进行处理,提取所需内容,并在顶层模块找到例化该模块的部分,提取对应内容进行替换。整体流程如图1所示。

2.2 处理宏定义文件

对于需要方便改动的常量和参数,可以使用宏定义的方式来引用。使用宏可以在不修改源代码的情况下修改设计,在IP核生成和流程测试中很有用,不仅可以保证代码具有良好的可配置性,还能提高代码的规范性和可读性。由于Verilog中宏定义往往采用一个单独的文件,提取文件中宏定义的名字和参数,替换掉文本内容中的宏定义的变量,进行宏展开。例如,宏定义文件中通过语句“`define `RST_NR 0”来定义参数“RST_NR”的值为0,依次提取参数名称为“RST_NR”,参数的值为0。再将子模块中的参数名称替换成参数的值,例如将语句“parameter nr=`RST_NR”替换成“parameter nr=0”。

2.3 处理子模块文件

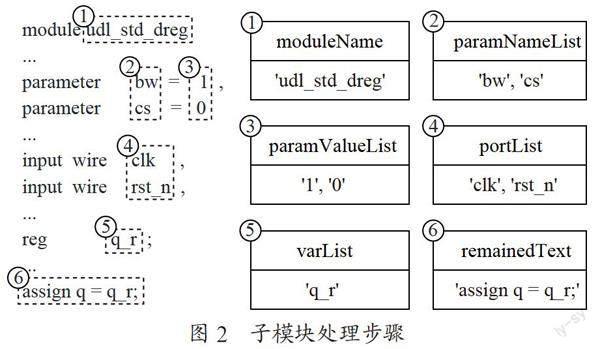

对子模块的文本进行处理。为了便于处理,去掉文本中的单行注释和多行注释。此外,要对文本进行内容的提取,如图2所示,具体步骤为:将要处理的①模块名称单独提取出来,方便再顶层模块中找到对应的内容;对带参数的模块进行例化时,为方便进行参数的修改,应提取②参数名称和③参数的值;信号端口通常采用的是名称关联的关联方式,④端口名称是需要提取出来的;模块内会声明一些新的变量,为了防止重复调用相同模块导致变量名称重复的问题,也要提取⑤变量名称进行后续处理;整个模块内容去除参数声明、端口列表和端口声明,只保留⑥数据流语句和行为语句。每一个标号内容都对应图2标号的示例。

当例化多个相同的模块时,一个个模块的手动例化会比较烦琐。用generate语句进行多个模块的重复例化,可大大简化程序的编写过程。generate语句也可允许在细化期间对语句进行条件选择,根据传递参数的不同值对执行的代码进行选择。处理该部分内容需要先将整个generate语句部分提取出来,即以“generate”开始至以“endgenerate”结束的部分。该部分的处理难点在于存在多个条件语句和过程结构语句嵌套和并列的情况,造成处理时难以将每个语句begin标志和end标志对应的问题。该问题会让提取对应参数所选择的正确语句变得困难。因此,本文引入利用栈的数据结构和计数器的处理方法,具体流程图如图3所示。

为了更加直观的描述该方法,举例如表2所示。

该方法将对应的begin和end一一配对,解决了难以选取正确的文本內容的问题。依次提取判断语句的情况,因Python与Verilog中表示“且或非”的方法不同,因此需将判断语句转换为Python语法中的语句,如表3所示。

通过以上代码进行替换后将再进行判断,提取为真语句后的标识符,截取该标识符之间的内容,即为所需,对于表2中的示例,若“st==1”为假,则截取“q_r<={bw{1'b0}};”。最后需将标识符还原成begin和end语句。对于嵌套和并列的generate语句,也可采用上述标识符的方法来区分不同的“generate”和“endgenerate”。

2.4 处理顶层模块文件

对顶层模块进行文本处理。出于同样理由的考虑,去掉文本中的单行注释和多行注释。每读入一遍子模块,就对顶层模块处理一遍,如图4所示,具体步骤为:根据读入的子模块的①模块名称,对顶层文件中该模块的内容进行截取,即⑦模块内容,所有的替换处理都是针对该子模块中⑥数据流语句和行为语句的内容;对于带参数例化的模块,考虑到参数例化存在只重置部分参数的情况,将需要新写入的⑧新参数名称和⑨新参数值提取出来,根据⑧新参数名称进行对照,用⑨新参数值替换掉②参数名称,未作替换的参数采用原来③参数的值替换掉②参数名称;模块例化通常使用按名字进行例化的方式,因为这种方式不考虑顺序,不容易出错,提取出例化模块的端口名称,即⑩例化端口名称,对应④端口名称将其一一替换成⑩例化端口名称,而在实际的项目中,往往会看到未连接的端口,这些未连接到例化模块中的端口按高阻态处理,防止在替换过程中报错,对应的实例名按照空字符存进对应的位置,如④端口名称“rst_n”所对应的⑩例化端口名称空字符“”;对于模块内变量的声明,为防止多次调用同一子模块而出现的声明名称重复的问题,在每次调用子模块时都为该名称添加包含调用次数字符的后缀,以对模块内的变量进行唯一化处理,例如当顶层模块第一次调用子模块时,子模块中的⑤变量名称需要被替换成加了后缀的?新变量名称;在所有的名称和值替换完成之后,处理完毕的⑥数据流语句和行为语句替换掉顶层模块中的⑦模块内容,完成该子模块的去层次化处理。每一个标号内容都对应图4标号的示例。

图4 顶层模块处理步骤

3 结 论

EDA软件属于当下的“卡脖子”技术之一,如何在本科阶段培养学生对集成电路设计以及EDA软件设计的兴趣,也是当前教育教学改革的热点话题。本文通过RTL设计的层次化展平处理,在难度适中的项目中涉及数字集成电路的结构化设计方法、HDL语法、数据结构、正则表达式、Python语言等内容,让学生在实践中深入掌握并灵活运用课堂上所学到的知识,并对EDA软件的工作原理建立了初步的理解和认识,从而提高学生的设计能力,增加学生的自主学习空间与学习自由度,培养学生的探究能力、创新能力,为日后的工作和科研打下良好的基础;是对提高集成电路设计以及EDA技术课程教学效果、提高学生专业实践能力的有益探索。

参考文献:

[1] 孙进辉.EDA技术在数字电子实验设计中的合理应用分析 [J].实验室研究与探索,2018,37(2):199-202.

[2] 丁家峰,李新梅,尹林子,等.EDA技术中自顶向下方法的教学与实践 [J].电气电子教学学报,2020,42(6):91-95.

[3] 丁家峰,李新梅,孙克辉,等.“EDA技術与应用”课程教学改革与创新 [J].电气电子教学学报,2017,39(6):47-49+59.

[4] 罗杰,康华光.两种硬件描述语言VHDL/Verilog的发展及其应用 [J].电气电子教学学报,2002(4):1-5.

[5] 马彤鑫.基于Python的正则表达式获取字符串信息 [C]//第三十四届中国(天津)2020'IT、网络、信息技术、电子、仪器仪表创新学术会议论文集.中国天津:天津市电子学会、天津市仪器仪表学会,2020:299-300.

[6] 张静,张妍.正则表达式及其在信息抽取中的应用 [J].电脑知识与技术,2009,5(15):3867-3868.

作者简介:杨怡雯(2001—),女,汉族,陕西西安人,本科在读,研究方向:电子信息。

收稿日期:2022-09-06

基金项目:湖南省教学改革省级课题(HNJG-2021-0302);中南大学教学改革校级课题(2021jy063)