于有源屏蔽层的高精度电阻检测电路设计

2023-06-21姜晓文王秋玮孔令威赵毅强

叶 茂,姜晓文,李 尧,王秋玮,孔令威,赵毅强

于有源屏蔽层的高精度电阻检测电路设计

叶 茂1, 2,姜晓文1, 2,李 尧1, 2,王秋玮1, 2,孔令威1, 2,赵毅强1, 2

(1. 天津大学微电子学院,天津 300072;2. 天津市成像与感知微电子技术重点实验室,天津 300072)

以聚焦离子束攻击和微探针攻击为主的侵入式物理攻击对芯片信息安全造成了严重威胁,有源屏蔽层作为安全芯片抵御侵入式物理攻击的第1道防线,由金属屏蔽层和完整性检测电路组成.金属屏蔽层用于遮盖安全芯片的关键模块及连接关系,完整性检测电路用于检测金属屏蔽层是否遭受攻击,二者相互配合来达到保护芯片内部敏感信息的目的.针对数字检测电路无法对重布线攻击进行检测的问题,基于GSMC 130nm 1.5V 4P7M工艺设计了用于检测大面积金属屏蔽层固有电阻变化的电阻检测电路.该电路采用全差分处理架构提高了电阻检测精度,消除了温度漂移误差,同时实现了较低的功耗.基于特定的金属屏蔽层布线方案设计了电阻-电压转换电路,将金属屏蔽层固有电阻变化量转换为电压变化量,并设计了Delta-Sigma调制器和数字处理电路等,对电压变化量进行采样、量化、编码与比较.该电路实现了对包括重布线攻击在内的各类正面侵入式物理攻击的有效检测,提升了有源屏蔽层的防护能力.后仿真结果表明,该电路能对5mm×5mm的大面积金属屏蔽层进行电阻检测,能准确识别75kΩ的金属屏蔽层电阻上发生的低至4Ω的微小变化,并产生高电平报警信号对芯片关键信息进行销毁;电路工作在 -40~105℃温度范围内,检测周期为12ms,检测周期内电路功耗为24.48μW,整体版图面积为370μm×135μm.

侵入式物理攻击;有源屏蔽层;电阻检测;高精度

随着物理攻击技术的发展,针对芯片内部数据的获取手段日益增多,严重威胁着芯片信息安全.侵入式物理攻击可以直接接触或修改电路走线,盗取关键信息,是现有物理攻击中最直接、最有效的手段,安全芯片使用有源屏蔽层作为抵御侵入式物理攻击的关键防线[1].完整性检测电路作为有源屏蔽层的核心,国内外许多学者对其展开了研究.Cioranesco 等[2]提出在金属屏蔽层中通入比特流,将输出比特流与输入比特流进行比较,从而达到检测目的;Jin等[3]提出将随机码流通入金属屏蔽层中,通过比对输入输出码流的一致性和完整性来判断金属屏蔽层是否被攻击.这些检测方法采用数字检测电路完成了对断路攻击的检测,具有工艺兼容性好、占用面积小等优点,但功耗较大,且无法对重布线攻击进行检测[4]. Ling等[5]提出一种基于顶层金属屏蔽层的走线延时检测电路,该电路首先将一个方波信号分两路分别通过顶层金属屏蔽层和RC延时单元,然后将两路输出信号异或产生窄脉冲,通过检测脉冲宽度去判断金属屏蔽层是否遭到FIB攻击破坏.该检测电路可以对重布线攻击进行检测,但由于走线延时是寄生电容和寄生电阻共同作用的结果,而寄生电容成分复杂,其变化量难以预估,因此该电路不易实现高精度.

针对数字检测电路和走线延时检测电路存在的问题,本文结合高复杂度随机哈密顿路径拓扑结构[6],设计了一种面向大面积金属屏蔽层的高精度、低温漂、低功耗的电阻检测电路,通过检测金属屏蔽层走线的寄生电阻变化实现对重布线攻击的有效检测与报警.

1 电阻检测电路整体架构和原理

金属屏蔽层的寄生电阻在无外界因素影响的情况下是固定值,当受到攻击后,其寄生电阻变为另一个固定值,因此电阻检测电路只需在上电后,每隔一定时间检测一次金属屏蔽层的寄生电阻是否发生变化即可.电阻值无法直接测量,需要转化为电压值或电流值,才能实现测量与比较,本文将金属屏蔽层的寄生电阻变化转换为电压变化进行检测.

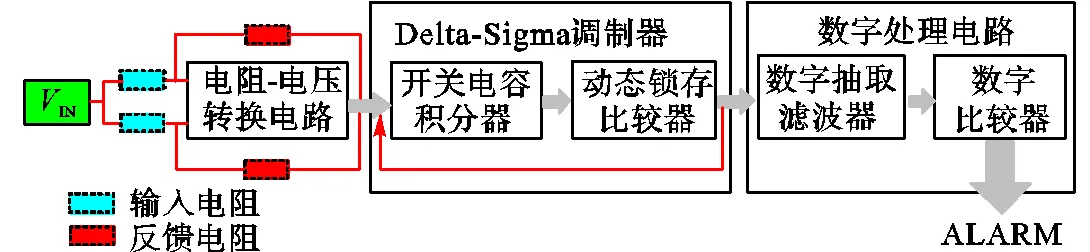

为了对大面积金属屏蔽层的寄生电阻进行高精度检测,本文基于Delta-Sigma ADC进行电阻检测电路设计,其结构如图1所示,主要由电阻-电压转换电路、Delta-Sigma调制器和数字处理电路组成.从图1可以看出,电阻-电压转换电路是单路输入、双路输出,其输入电阻和反馈电阻均为金属屏蔽层走线等效电阻,实现了将金属屏蔽层寄生电阻变化转换为两路输出电压的变化.两路输出电压经过由开关电容积分器和动态锁存比较器等组成的Delta-Sigma调制器进行采样、量化,得到表征两路输出电压大小的比特流.该比特流经过由数字抽取滤波器和数字比较器等组成的数字处理电路进行编码、比较,最终得到ALARM报警信号.将金属屏蔽层未受到攻击时芯片第1次上电得到的数字抽取滤波器输出码值作为参考值,当受到攻击导致金属屏蔽层的寄生电阻发生变化时,数字抽取滤波器输出码值会随之变化,数字比较器将当前输出码值与参考值进行比对,当两者不相等时,可以认为金属屏蔽层受到攻击,电路产生高电平报警信号,控制芯片进行关键数据销毁.

图1 电阻检测电路结构框图

Fig.1 Block diagram of the resistance detection circuit

2 基于有源屏蔽层的电阻检测电路实现

2.1 电阻-电压转换电路

本文采用两路比例运算放大器实现了电阻-电压转换电路,基于特定的金属屏蔽层布线方案,完成了电路输入电阻和反馈电阻的设计,有效降低了电路复杂度和功耗,提高了大面积金属屏蔽层的电阻检测精度,同时消除了温度漂移对电路的影响.

2.1.1 金属屏蔽层布线方案和攻击分析

金属屏蔽层作为有源屏蔽层的重要组成部分,需要具有高复杂度、高覆盖率[7]、高生成速度和高攻击成本.高复杂度增加了攻击者识别金属屏蔽层的难度,高覆盖率保证金属屏蔽层尽可能覆盖芯片所有需要保护的模块和走线,高生成速度保证设计人员能快速生成大面积金属屏蔽层,高攻击成本能让攻击者放弃攻击.随机哈密顿路径因其高复杂度成为金属屏蔽层的最优布线选择,一般可以进行单通道或者多通道布线,金属屏蔽层复杂度和覆盖率会随着通道数增加而降低,攻击成本和生成速度会随着通道数增加而增加.因此,对于大面积金属屏蔽层,需要选择合适的布线通道数.

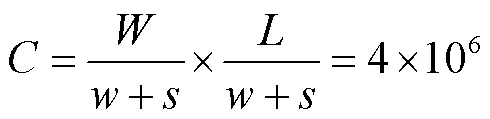

本文以能识别2μm×8μm的单比特寄存器上方的金属屏蔽层受到攻击后所造成的最小电阻变化进行相关设计,为了尽可能在实现高性能金属屏蔽层的同时,减小电阻-电压转换电路的设计难度,根据所用工艺的规则文件规定的顶层金属最小线宽和线间距,设计的金属屏蔽层走线线宽为2μm,线间距为0.5μm,对宽为5mm,长为5mm的安全芯片进行防护,所得到的格点数量为

随机哈密顿路径通过遍历所有的格点生成金属屏蔽层单通道或者多通道布线,因此所有通道总长度不变,只是根据通道数量进行了等分.

本文根据电阻-电压转换电路的基本设计思想,综合考虑金属屏蔽层的复杂度、覆盖性、攻击成本和生成速度,提出如下布线方案:将整个5mm×5mm的待防护区域进行二等分,两个区域分别生成四通道金属屏蔽层走线,对应电阻-电压转换电路中所需的电阻,将每个区域中任一通道作为电阻-电压转换电路的输入电阻,另外3条通道串联在一起作为反馈电阻,其布线示意如图2所示.

图2中区域1将红色走线作为一路比例运算放大器的输入电阻,将绿色走线首尾串联作为该路的反馈电阻,区域2将黄色走线作为另一路比例运算放大器的输入电阻,将蓝色走线首尾串联作为该路的反馈电阻.该工艺顶层金属的方块电阻值1=0.04Ω,金属线厚度约为1μm,因此每条通道的电阻值约为

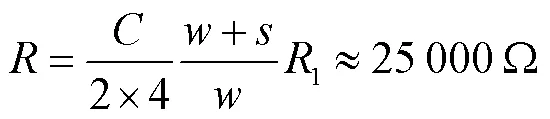

针对上述布线方案,本文对重布线攻击进行研究,推断出攻击者对单比特寄存器上方的金属屏蔽层进行攻击时,首先对整体金属屏蔽层进行识别,确定攻击区域,然后对攻击区域内金属屏蔽层的通道数和走线结构进行分析,从而确定最优攻击方案.根据分析,如果单比特寄存器上方的走线结构位于图2所示的攻击区域,则重布线攻击引起的电阻变化最小,攻击示意如图3所示.

图3 重布线攻击示意

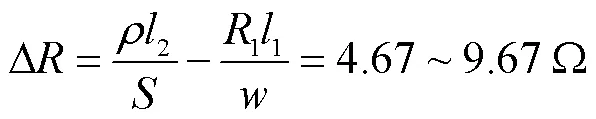

图3中绿色虚线是被攻击者切除的原金属走线,长度1为16.5μm,黄色线为沉积的新金属,长度2为0.5μm.重布线攻击沉积的新金属一般为铂(Pt)的金属有机化合物,其电阻率要远大于铂的电阻率,一般为10~20Ω·μm[8],假设沉积的新金属横截面积为1μm2,则引起的最小电阻变化为

考虑留有一定余度,最终将4Ω作为检测的最小电阻变化.

2.1.2 电路设计

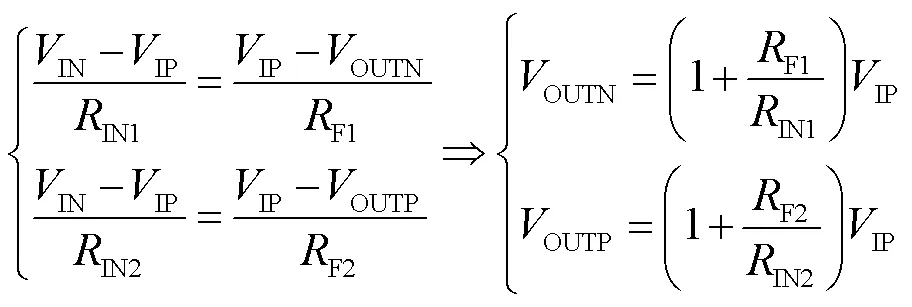

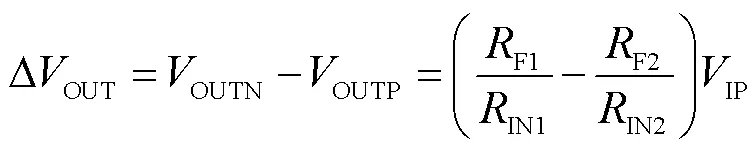

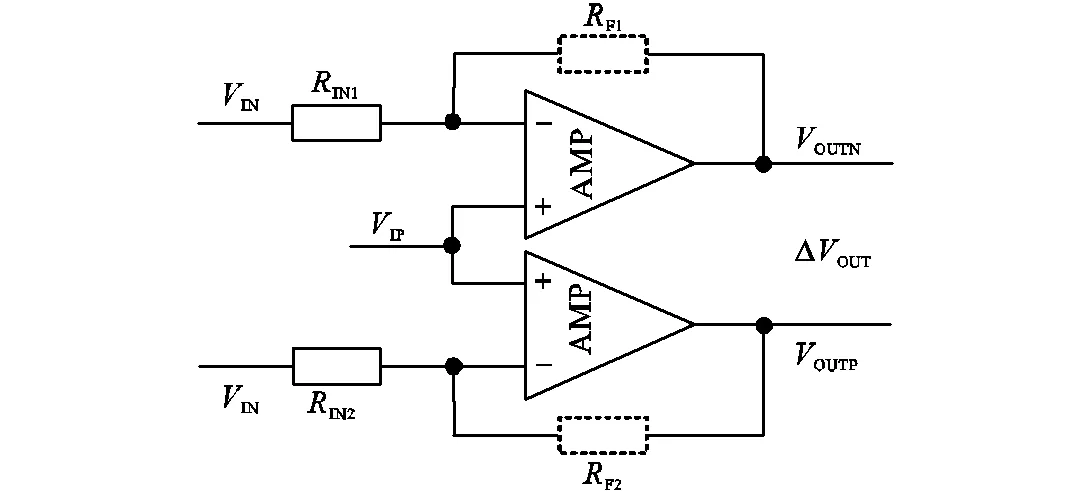

传统的电阻-电压转换电路一般采用电阻分压或者给定一个恒流源和电阻并联得到电压值.本文设计的电阻-电压转换电路基于第2.1.1节提出的金属屏蔽层布线方案,由两路比例运算放大器组成,如图4所示.图中IN接SS,IP接由带隙基准源产生的基准电压,放大器为高增益、宽输出摆幅的两级折叠式共源共栅放大器,输入电阻IN1,IN2为一条布线通道等效的电阻,反馈电阻F1、F2为3条布线通道串联等效的电阻.根据比例运算放大器的“虚断”和“虚短”特性可以得知,放大器的两输入端电压相等,且电流全部流经反馈电阻,因此输出电压OUTN和OUTP分别为

从而得到两输出电压差ΔOUT为

图4 电阻-电压转换电路

金属屏蔽层受温度和工艺偏差的影响,会使电阻-电压转换电路的输出电压发生较大偏移.为了防止输出电压超出放大器输出摆幅,设定27℃、理想工艺下输出电压为电源电压1.5V的一半,根据式(4)得到放大器正相输入端电压IP为187.5mV.

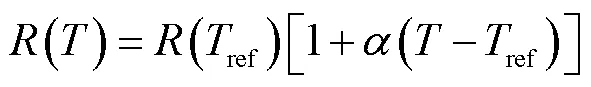

对于温度的影响,主要考虑温度对金属屏蔽层寄生电阻的影响,假设顶层金属的一阶温度系数为,则其电阻值与温度的关系应表示为

式中:为当前温度;ref为参考温度27℃;()为当前温度下的电阻值;(ref)为参考温度下的电阻值.由于相邻布线通道温度变化一致,因此,如果图2中区域1温度变化Δ1,区域2温度变化Δ2,则ΔOUT仍不变,即

因此该结构消除了温度漂移对电路的影响.

工艺偏差虽然对金属屏蔽层和整个电阻检测电路产生的不可控变化会大大超出金属屏蔽层受到攻击所引起的变化,但在芯片生产出来后其工艺偏差就不再改变,因此考虑将芯片未受到攻击时第1次上电得到的ΔOUT量化编码结果储存在芯片的存储器中,作为后续数字比较器的参考值.本文对电路进行蒙特卡罗仿真1000个点后得到,工艺偏差导致电阻-电压转换电路输出电压的3变化范围为±150mV, 因此Delta-Sigma调制器的输入动态范围至少为±150mV.

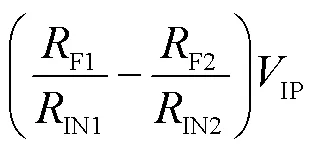

由于受到攻击后只会造成其中某一条通道寄生电阻值发生变化,因此,假设在理想情况下,IN1=IN2=IN,F1=F2=3IN,ΔOUT=0,根据式(5),如果IN2或者F2受到重布线攻击发生4Ω微小变化,会造成的输出电压差可能为

因此,为实现对攻击行为的有效检测,设计的ADC应满足LSB≤0.03mV.

2.2 Delta-Sigma调制器

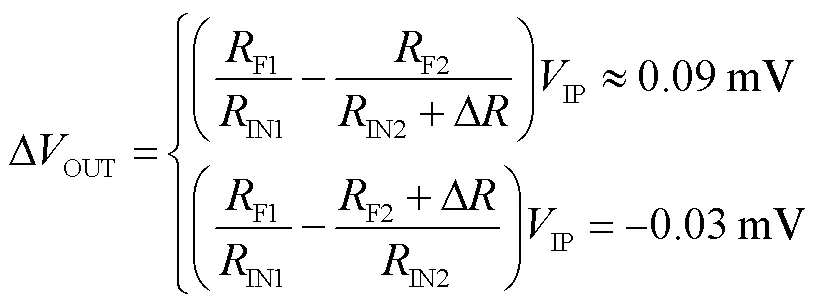

Delta-Sigma ADC因具有高精度、低噪声、低功耗,被广泛应用于工业测量领域,其核心电路为Delta-Sigma调制器.Delta-Sigma调制器利用过采样技术和噪声整形技术降低了信号带宽内的噪声,提高了信噪比,从而实现较高的ADC精度[9].Delta-Sigma调制器有连续时间和离散时间两种,由于离散时间Delta-Sigma调制器对时钟抖动和工艺误差的敏感性更低[10],因此本文设计了一款14bit二阶单环单比特离散时间Delta-Sigma调制器对前级输出直流电压进行采样、量化,其结构如图5所示.该调制器由积分器、加法器、量化器和反馈DAC构成.

图5 Delta-Sigma调制器结构

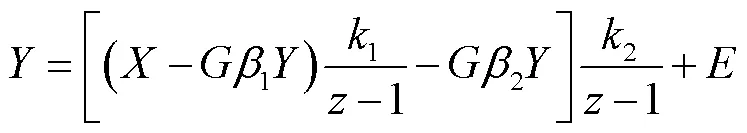

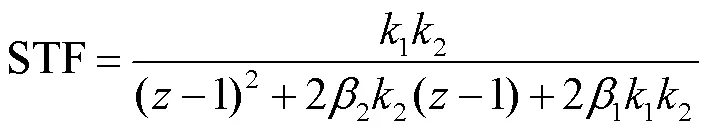

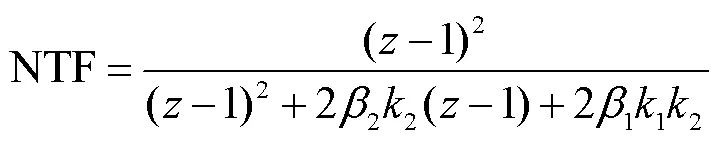

根据调制器结构图和线性分析方法,可以得到图5所示调制器的域传递函数为

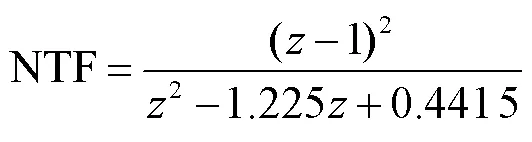

式中:、、分别为输入信号、输出信号和量化噪声;1和2为调制器积分增益系数;1和2为反馈系数,为反馈DAC的增益,根据建模中的共模电平和反馈DAC的参考电平可以得到=2.从而得到系统在域的信号传递函数STF和噪声传递函数NTF分别为

本文对该调制器结构进行传递函数系数设计,通过式(10)可以看到该调制器结构的STF呈低通特性,满足要求,因此主要对NTF进行系数设计,使其呈高通特性,从而将量化噪声调制到高频[11].在MATLAB Simulink仿真平台,利用配置好的建模工具包SDToolbox中的synthesizeNTF函数得到过采样率为512的二阶Delta-Sigma调制器的NTF为

对比式(11)和(12),可以计算得到一组比较合适的NTF系数:1=0.3,2=0.5,1=0.5,2=0.75.在此系数基础上,利用Simulink对调制器结构进行带非理想因素[12]的建模仿真,主要考虑的非理想因素有时钟抖动,/噪声和积分运放的有限增益,设置采样频率为64kHz,过采样率为512,输入信号是频率为17.578Hz,幅值为±180mV的正弦波,仿真得到该调制器的有效位数为15.01bit,满足要求.

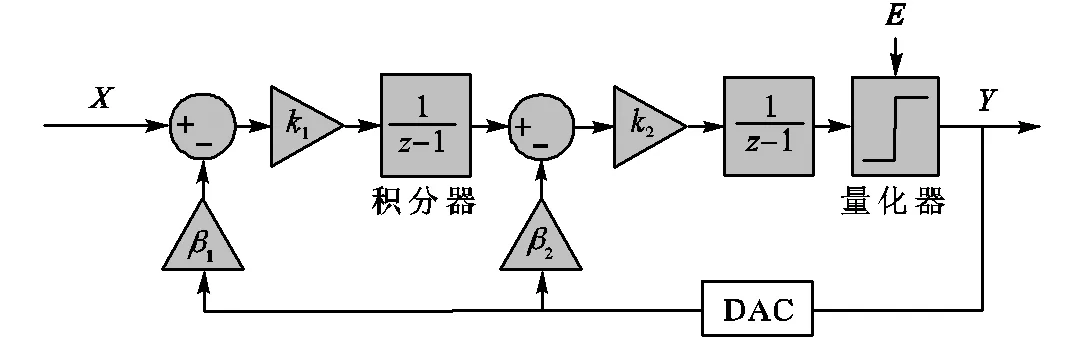

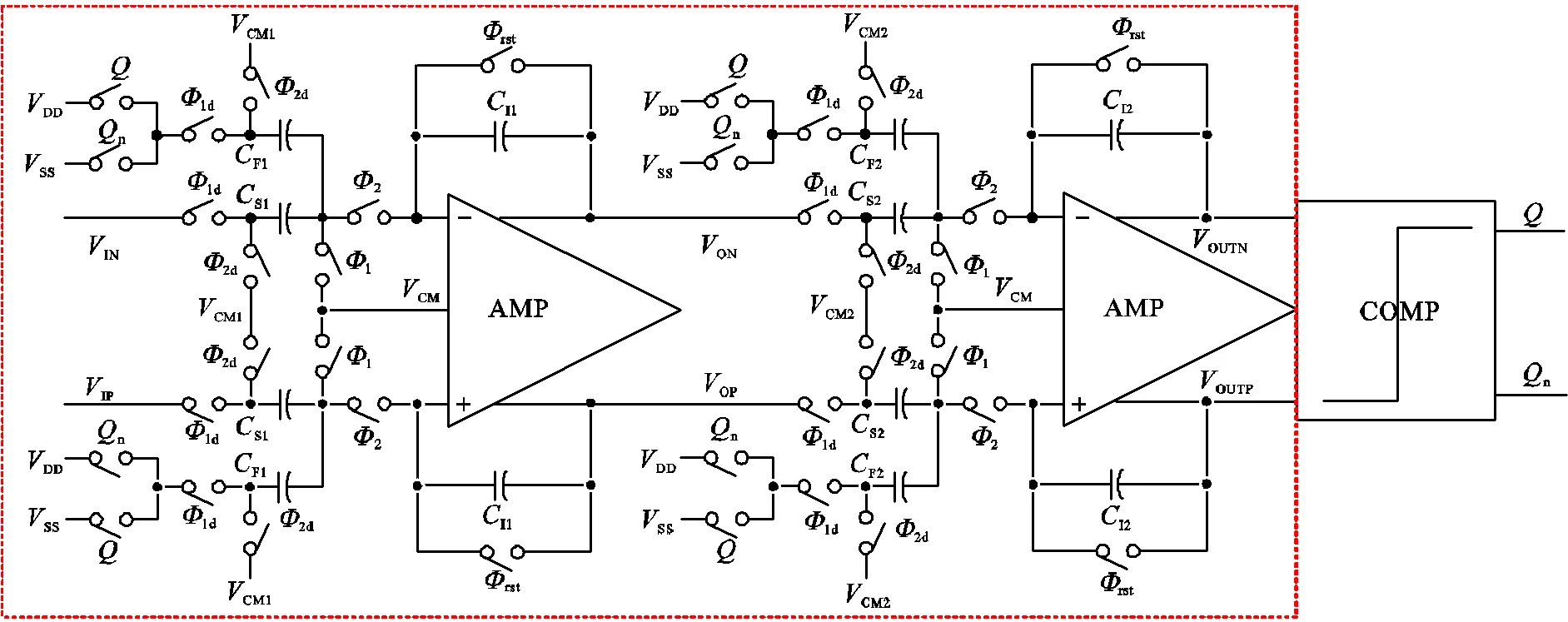

根据Simulink建模及仿真结果,本文进行了Delta-Sigma调制器电路设计,如图6所示,该电路主要由二阶积分器、单比特量化器和单比特反馈DAC构成.

积分器采用开关电容积分器进行实现,开关电容积分器的积分时间由电容大小决定,积分增益系数由电容比值决定.在集成电路工艺中,电容可以制作很精确,且电容比值更容易控制,因此开关电容积分器通常具有很好的线性度和温度特性.本文采用二阶全差分开关电容积分器对输入信号进行采样、积分,全差分结构能够消除谐波失真,降低直流失调,如图6虚线框所示,由于图中第1级开关电容积分器的反馈系数为0.3,因此该调制器的实际量化范围为0.3DD.

图6 Delta-Sigma调制器整体电路结构

开关电容积分器的核心是放大器,由于调制器采样频率低,因此可进行低功耗设计,本文选用全差分折叠式共源共栅结构进行放大器设计,同时采用开关电容共模反馈电路稳定放大器的输出共模电压,在实现低功耗的同时保证宽输出摆幅.

开关电容积分器对时钟信号的相位非常敏感,为了防止不同开关同时闭合导致电荷泄漏,开关电容积分器由两相不交叠时钟来控制其采样和积分过程.两相不交叠时钟的工作过程是输入时钟经过反相器变成相位相反的时钟,然后两路时钟分别经过由多个反相器和与非门构成的锁存延时单元得到相位不交叠的时钟.图6中开关控制信号1和2是具有相反相位的不交叠时钟,1d和2d分别是1和2的下降沿延迟时钟,rst是额外的信号,在完成一次模数转换后,对开关电容积分器进行复位.

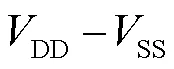

图7 动态锁存比较器电路

2.3 数字处理电路

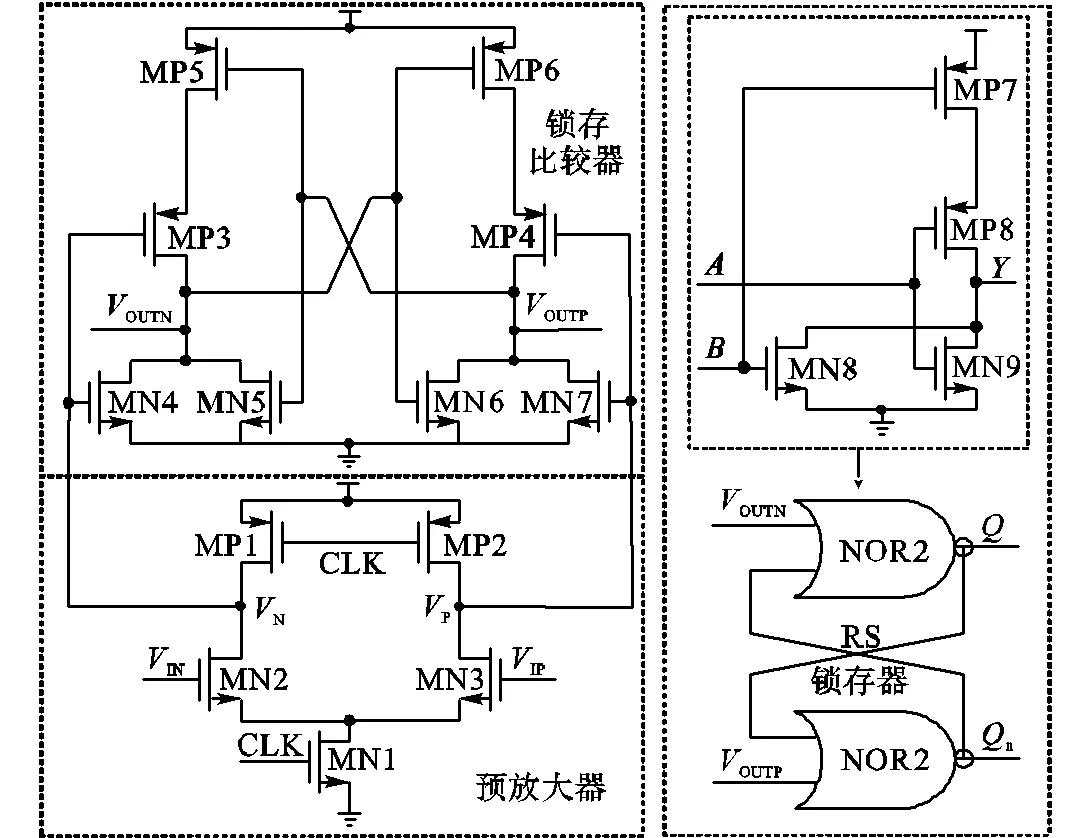

数字处理电路对Delta-Sigma调制器的量化结果进行编码、比较,最终得到报警信号,其原理框图如图8所示,由分频器、数字抽取滤波器、数字比较器和阈值判断模块组成.

图8 数字处理电路

分频器将输入时钟信号CLK进行分频,得到不同占空比的信号RST和EN,用于对数字抽取滤波器和数字比较器进行控制,同时RST也用于在一次模数转换后作为控制时钟对Delta-Sigma 调制器中的开关电容积分器进行复位.

数字抽取滤波器对Delta-Sigma调制器的量化结果进行低通滤波和降采样,由8位计数器和15位累加器组成,计数器由动态D触发器构成,累加器由加法器和寄存器组成[14].计数器输出的8bit数据作为加法器一端输入的低8位,高7位保持全0,加法器输出的15bit数据经过寄存器输入到加法器的另一端,实现对计数器输出数据的不断累加,最后得到15位的数字量输入到数字比较器中与第1次上电得到的参考值进行比较,如果两者相差大于等于1,则OUT输出高电平异常信号.同时为了防止由于外界因素干扰导致电路出现误报警的情况,设计了阈值判断模块,设置冗余安全阈值为2,在检测周期内,只有当OUT输出高电平异常信号的次数超过冗余安全阈值,才会产生高电平报警信号ALARM.

3 电路前仿真与版图后仿真

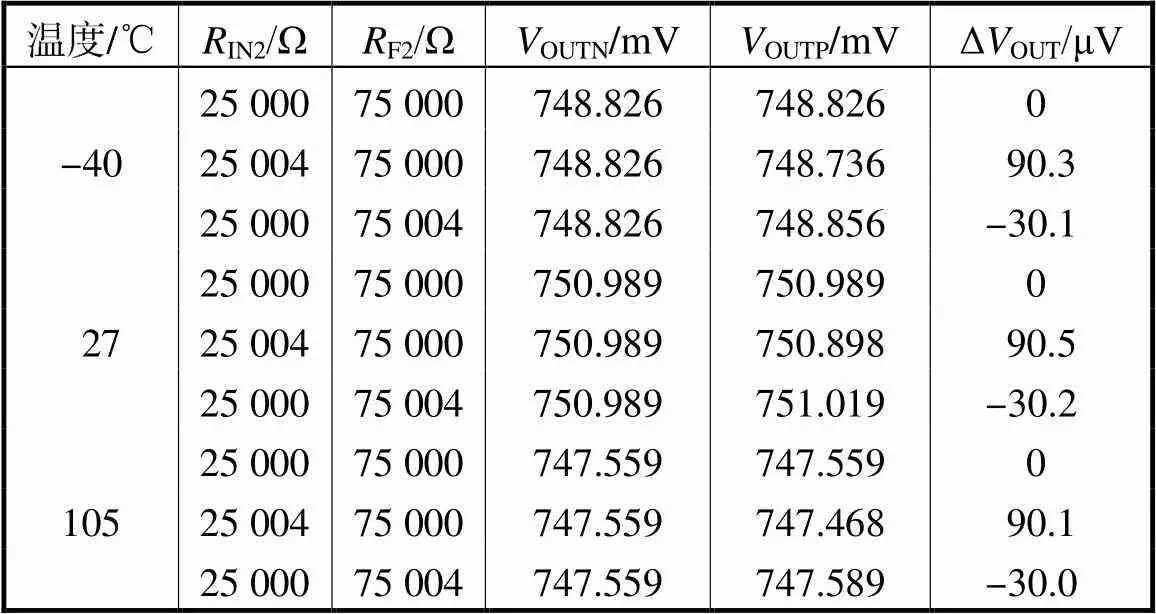

对电路进行前仿真,电阻-电压转换电路需要将微小的电阻变化转换成Delta-Sigma调制器能分辨的最小电压值,根据金属屏蔽层寄生电阻值,设置IN1为25kΩ,F1为75kΩ不变,在-40℃、27℃、105℃ 3个温度下仿真IN2和F2未受到攻击以及分别受到重布线攻击导致4Ω微小变化时,电路输出电压的变化,仿真结果如表1所示.从表中可以看出,该电路有很好的抗温度特性,在不同温度下,IN2和F2未受到攻击时,两路输出电压的差值均在μV以下,不会造成误报警,而在不同温度下IN2和F2分别受到重布线攻击时所产生的最小电压差值为30μV,符合之前的分析.

表1 电阻-电压转换电路输出结果

Tab.1 Output results of resistance-voltage conversion circuit

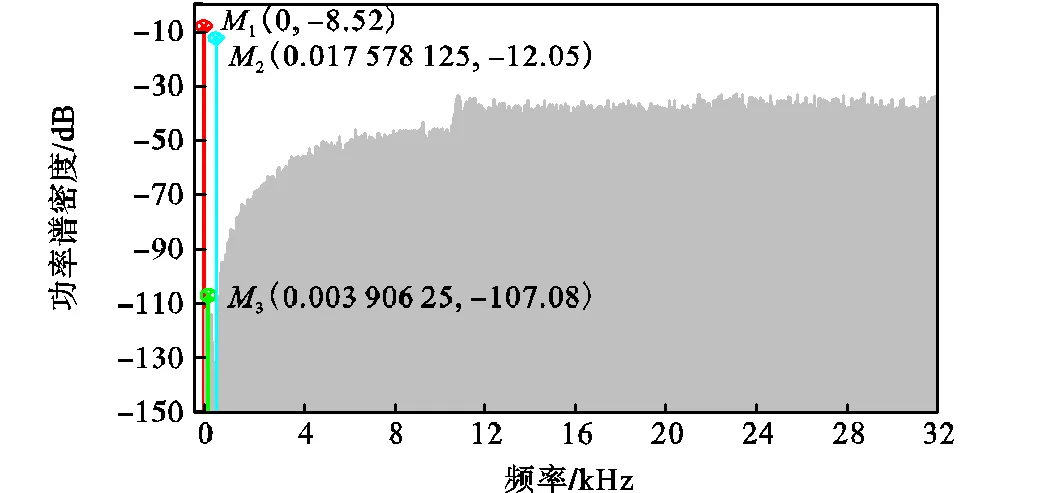

在电源电压为1.5V,采样频率为64kHz,过采样率为512,输入是幅值为±180mV、频率为17.578Hz的正弦波信号的仿真条件下,对Delta-Sigma调制器进行Transient Noise前仿真,对仿真结果进行FFT分析,计算得到调制器有效位数为14.8bit,信噪比为90.9dB,其功率谱密度如图9所示,仿真得到该调制器功耗仅为9.4μW.

图9 Delta-Sigma调制器功率谱密度

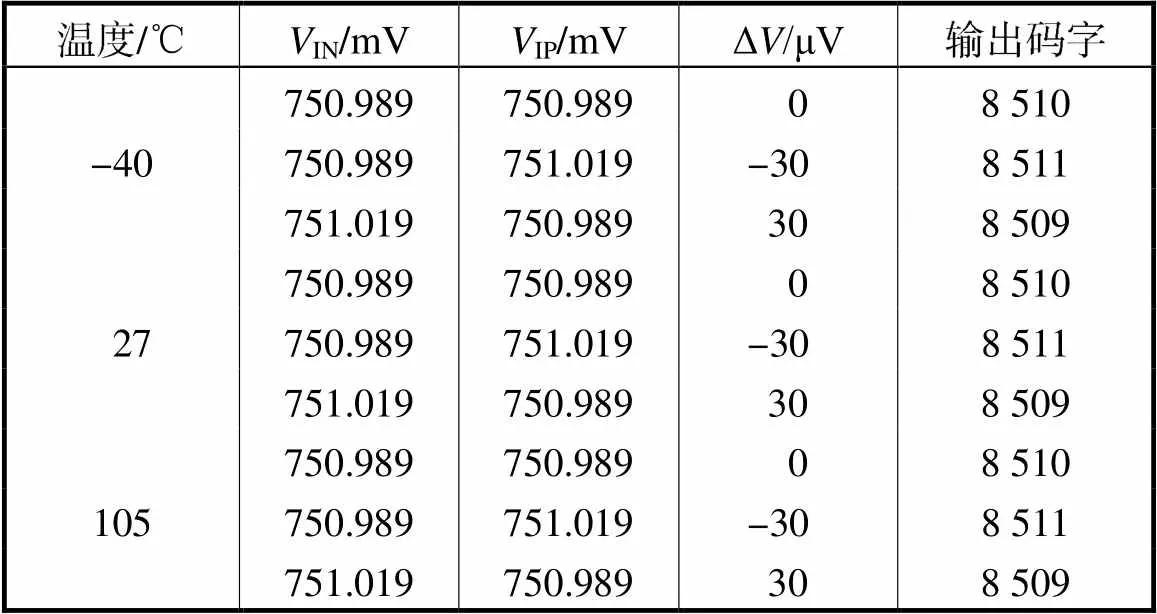

对由调制器和数字抽取滤波器组成的二阶Delta-Sigma ADC进行仿真,在-40℃、27℃、105℃ 3个温度下仿真两输入电压差不变时以及电压差变化30μV时,数字抽取滤波器输出码字的变化,如表2所示.从表中可以看出,当两输入电压差不变时,输出码字不会随着温度发生变化而变化,当两输入电压差变化30μV时,输出码字在不同温度下也不变,但与两输入电压差不变时得到的码字相差1.

表2 数字抽取滤波器输出结果

Tab.2 Output results of the digital decimation filter

对整体电路进行前仿真发现,金属屏蔽层在不受到攻击时,检测电路不会因为温度发生变化而误报警,但在其受到攻击导致任一通道变化4Ω甚至更大时,在不同温度下都会报警.整体电路在1.5V电源电压下功耗为24.48μW.

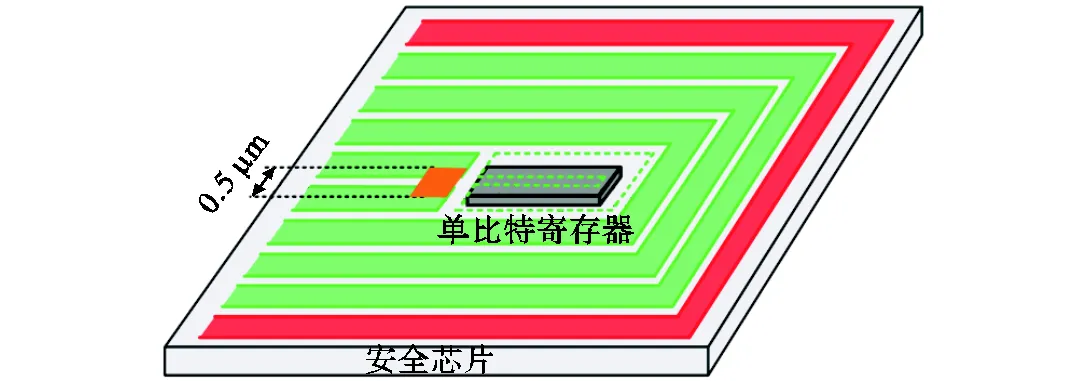

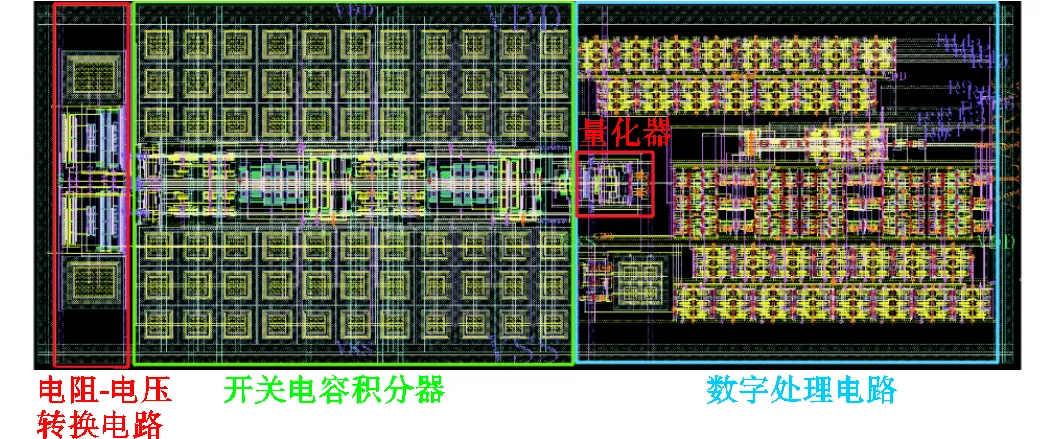

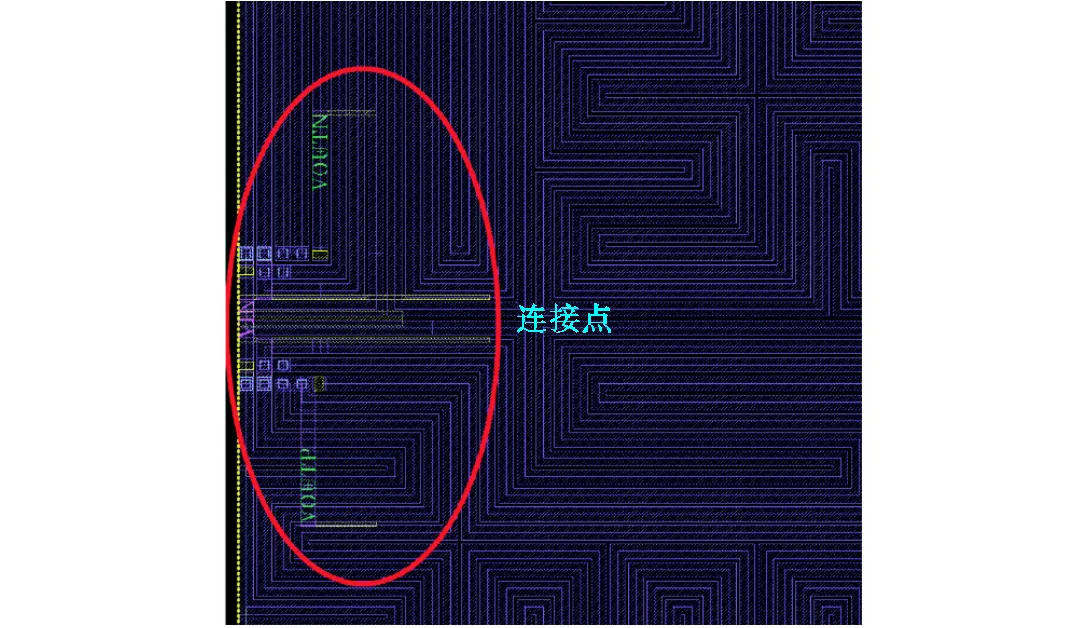

根据所设计的电路结构,基于GSMC 130nm 1.5V 4P7M工艺对版图进行设计,图10是电阻检测电路版图,其面积为370μm×135μm,图11是金属屏蔽层与电阻检测电路连接点处的局部布线版图,金属屏蔽层总面积为5mm×5mm.

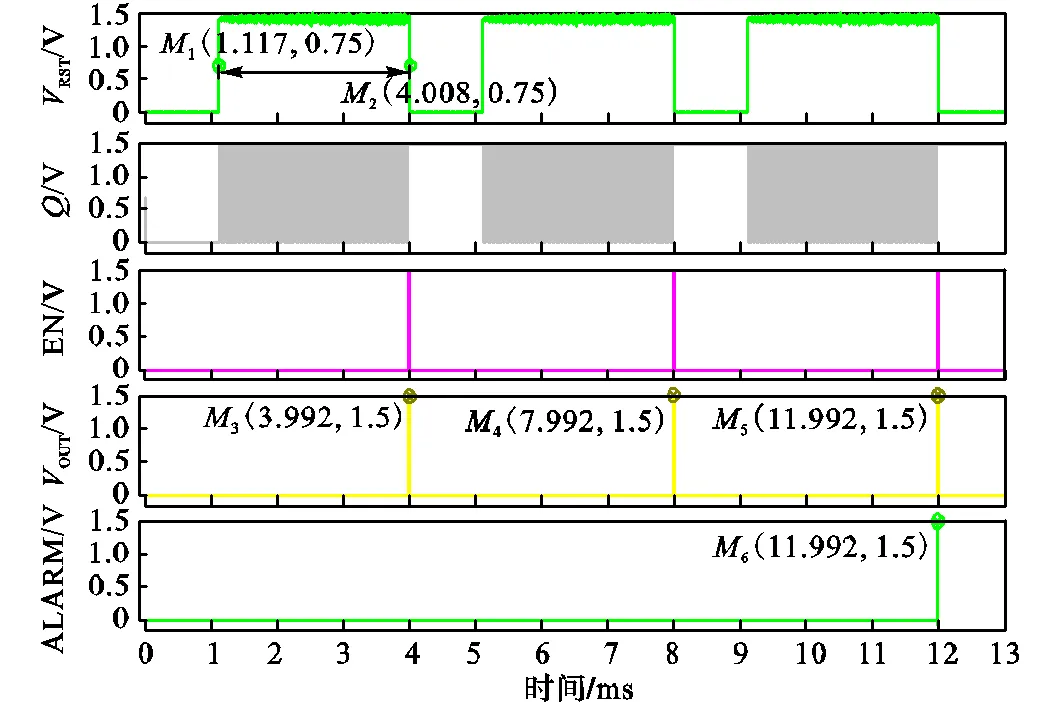

提取版图寄生参数并进行后仿真,得到的后仿真结果时序图如图12所示,从图中可以看出,检测周期为12ms,在检测周期内能对金属屏蔽层进行3次电阻检测,并在金属屏蔽层受到重布线攻击导致4Ω变化时,报警信号ALARM拉高.

图10 电阻检测电路版图

图11 金属屏蔽层局部布线版图

图12 后仿真结果

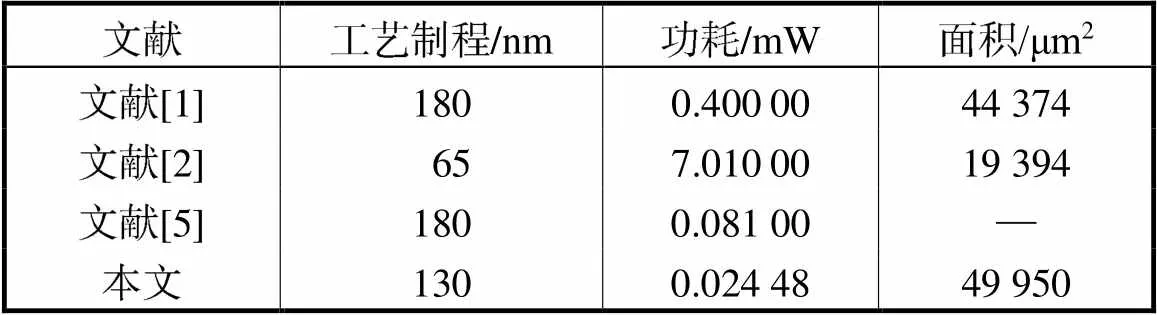

表3给出了本文与国内外完整性检测电路相关研究的参数对比.表中文献[1]和文献[2]研究的是数字检测电路,文献[5]研究的是走线延时检测电路,三者与本文提出的电阻检测电路具有不同的检测机理和电路结构,因此只能对功耗和面积参数进行对比.从表中可以看出,本文设计的电阻检测电路在功耗和面积上的控制较为均衡,与其他完整性检测电路相比,虽然版图面积较大,但功耗较低.

表3 功耗和面积对比

Tab.3 Comparison of power consumption and area

4 结 语

本文所设计的高精度电阻检测电路主要用于大面积有源屏蔽层,搭配基于随机哈密顿路径的高性能金属屏蔽层,可用来有效抵抗侵入式物理攻击.与数字检测电路相比,能用来抵抗重布线攻击,具有更高的安全性.检测电路能对5mm×5mm的大面积金属屏蔽层进行电阻检测,最小能实现75kΩ电阻上发生4Ω变化量的精确检测,采用全差分结构使检测电路不受温度漂移影响,整个检测过程在12ms内完成,检测周期内功耗低至24.48μW.

[1] 甄 帅,原义栋,辛睿山,等. Galois环振的随机重构主动屏蔽层电路[J]. 哈尔滨工业大学学报,2021,53(6):148-154.

Zhen Shuai,Yuan Yidong,Xin Ruishan,et al. Randomly reconfigurable active shield circuit based on Galois ring oscillator[J]. Journal of Harbin Institute of Technology,2021,53(6):148-154(in Chinese).

[2] Cioranesco J M,Danger J L,Graba T,et al. Cryptographically secure shields[C]//2014 IEEE International Symposium on Hardware-Oriented Security and Trust(HOST). Arlington,USA,2014:25-31.

[3] Jin R,Yuan Y,Xin R,et al. Active shield design for security chip in smart grid[C]//Frontiers in Cyber Security. Singapore,2018:273-281.

[4] 辛睿山. 抗物理攻击安全存储关键技术研究[D]. 天津:天津大学微电子学院,2019.

Xin Ruishan. Research on Key Technologies of Secure Storage against Physical Attacks[D]. Tianjin:School of Microelectronics,Tianjin University,2019(in Chinese).

[5] Ling M,Wu L,Li X,et al. Design of monitor and protect circuits against FIB attack on chip security[C]//2012 Eighth International Conference on Computational Intelligence and Security. Guangzhou,China,2012:530-533.

[6] Xin R,Yuan Y,He J,et al. High-efficient generation algorithm for large random active shield[J]. Science China Information Sciences,2019,62(3):1-3.

[7] Wang K,Gu Y,Zhou T,et al. Multi-pair active shielding for security IC protection[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2018,38(12):2321-2329.

[8] 王 敏,刘 莹,邵 瑾,等. 基于 FIB 技术攻击芯片主动屏蔽层[J]. 电子技术应用,2017,43(7):28-31.

Wang Min,Liu Ying,Shao Jin,et al. Attack chip’s active shield based on FIB technology[J]. Application of Electronic Technique,2017,43(7):28-31(in Chinese).

[9] Schreier R,Temes G C. Understanding Delta-Sigma Data Converters[M]. Piscataway:IEEE Press,2005.

[10] 王冠然. 低速高精度Sigma-Delta调制器的研究与设计[D]. 大连:大连理工大学微电子学院,2021.

Wang Guanran. Research and Design of Low Speed and High Precision Sigma-Delta Modulator[D]. Dalian:School of Microelectronics,Dalian University of Technology,2021(in Chinese).

[11] 张 涛,何 鹏,刘 劲. 低电压低功耗音频Σ-Δ ADC调制器设计[J]. 湖南大学学报(自然科学版),2021,48(8):125-132.

Zhang Tao,He Peng,Liu Jin. Design of low voltage low power audio Σ-Δ ADC modulator[J]. Journal of Hunan University(Natural Sciences),2021,48(8):125-132(in Chinese).

[12] Zare-Hoseini H,Kale I,Shoaei O. Modeling of switch-capacitor delta-sigma modulators in SIMULINK[J]. IEEE Transactions on Instrumentation and Measure-ment,2005,54(4):1646-1654.

[13] Jeon H J,Kim Y B. A novel low-power,low-offset,and high-speed CMOS dynamic latched comparator[J]. Analog Integrated Circuits and Signal Processing,2012,70(3):337-346.

[14] 李 烨. 荧光检测生物芯片的列级Sigma-delta ADC设计[D]. 南京:东南大学微电子学院,2018.

Li Ye. Design of Column-Level Sigma-Delta ADC for Fluorescence Detection Biochips[D]. Nanjing:School of Microelectronics,Southeast University,2018(in Chinese).

Design of a High-Precision Resistance Detection Circuit Based on the Active Shield

Ye Mao1, 2,Jiang Xiaowen1, 2,Li Yao1, 2,Wang Qiuwei1, 2,Kong Lingwei1, 2,Zhao Yiqiang1, 2

(1. School of Microelectronics,Tianjin University,Tianjin 300072,China;2. Tianjin Key Laboratory of Imaging and Sensing Microelectronic Technology,Tianjin 300072,China)

Intrusive physical attacks,mainly the focused ion beam and microprobe attacks,pose a serious threat to chip information security. The active shield as the first line of defense for security chips against intrusive physical at-tacks consists of a metal shield and an integrity detection circuit. The metal shield covers the key modules and connec-tions of the security chip,the integrity detection circuit detects the attack on the metal shield,and the two synergisti-cally work to protect the sensitive information inside the chip. However,the digital detection circuit cannot detect a rewiring attack. To address this issue,a resistance detection circuit was designed based on the GMSC 130nm 1.5V 4P7M process for detecting the inherent resistance change of a large-area metal shield. The circuit adopted a fully differential processing architecture to improve the resistance detection accuracy and eliminate temperature drift errors with lower power consumption. Based on the specific metal shield wiring scheme,a resistance-voltage conversion circuit was designed to convert the inherent resistance variation of the metal shield into voltage variation,and a Delta-Sigma modulator and a digital processing circuit were designed to sample,quantify,encode,and compare the voltage variations. The circuit can effectively detect various frontal intrusive physical attacks,including rewiring attacks,and improve the active shield protection capability. The post-simulation results show that the circuit can perform resistance detection for a large-area metal shield of 5mm×5mm,accurately identifying even minimal changes as low as 4Ω occurring on a 75kΩ metal shield resistance and generating a high-level alarm signal to destroy critical information on the chip. The circuit works in the temperature range of -40—105℃,with a detection period of 12ms,a circuit power consumption of 24.48μW during the detection,and a layout area of 370μm×135μm.

intrusive physical attack;active shield;resistance detection;high precision

10.11784/tdxbz202204001

TN492

A

0493-2137(2023)08-0807-08

2022-04-01;

2022-05-20.

叶 茂(1987— ),男,博士,副教授,mao_ye@tju.edu.cn.Email:m_bigm@tju.edu.cn

赵毅强,yq_zhao@tju.edu.cn.

国家自然科学基金资助项目(61832018).

the National Natural Science Foundation of China(No. 61832018).

(责任编辑:孙立华)