一种基于CPU 总线通信的同步设计方法

2023-05-10上海航天电子技术研究所宁静邓一帆刘陶然吴维林陈云

上海航天电子技术研究所 宁静 邓一帆 刘陶然 吴维林 陈云

在宇航产品设计中,有时需要把多个FPGA 作为外设挂接在CPU 并行总线上。出于功能实现需求,FPGA和CPU 可能工作在不同的时钟域下,而不同时钟域下的信号传输需要进行跨时钟域处理来避免亚稳态问题。本文通过介绍常用的CPU 总线通信同步设计方法,提出了握手协议存在的安全隐患,如果仅对CPU 控制信号进行跨时钟域处理,可能导致FPGA 内部触发器的数据端产生毛刺,从而导致FPGA 误响应CPU 指令。经过仿真测试证明,在CPU 读写时序余量充裕的前提下,可以采用对多比特的地址线和数据线打一拍的操作来解决FPGA 内部触发器数据端的毛刺问题,为更可靠地进行总线通信提供了一种思路。

随着军工产品向着高集成度、高速和高可靠性方向发展[1],基于CPCI 结构的总线通信具有坚固、可靠、易于扩展、高速等优点[2],在航空航天等领域中得到了越来越广泛的应用。在实际应用中,随着FPGA 实现的功能越来越复杂,FPGA 与CPU 之间的通信,跨时钟域的情况经常不可避免。

针对CPU 总线通信出现的跨时钟域问题,常见的解决方法是通过握手协议,仅对单比特的控制信号进行同步处理,使得并行的多比特地址和数据信号满足建立时间和保持时间的要求。本文在此基础上,讨论了在CPU总线通信中,使用握手协议存在的安全隐患,并给出了可行的解决方法。

1 亚稳态

时钟域包含单时钟域和多时钟域。同一时钟域下的信号传输不需要进行同步处理,而跨时钟域下的信号传输,需要进行同步处理,否则会引入亚稳态问题,亚稳态问题解决不当会造成采样数据错误,功能失效。

造成亚稳态问题的根本原因在于FPGA 内部触发器无法满足建立时间和保持时间的时序要求。建立时间是指在时钟沿到来之前,触发器输入数据信号必须保持稳定的时间。保持时间是指在时钟沿之后,数据信号必须保持稳定的时间[3]。

当触发器输入端的信号跳变时刻与时钟沿很接近,无法满足建立时间或保持时间的余量要求,则触发器进入亚稳态状态,既无法预测该触发器的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

当信号在不同的时钟域之间进行传递时,由于无法确定输入信号跟接收时钟上升沿之间的时间关系[4],会出现亚稳态现象。

CPU 总线通信模型中,CPU 与FPGA 的信号交互如图1 所示。

图1 典型的CPU 总线通信模型Fig.1 A typical CPU-bus communication model

典型的CPU 写数据流程为:CPU 输出控制信号(片选信号、写使能信号、读使能信号)、地址信号、数据信号给FPGA。

典型的CPU 读数据流程为:CPU 输出控制信号(片选信号、写使能信号、读使能信号)、地址信号给FPGA,FPGA 返回相应的数据信号给CPU。

在CPCI 总线通信模型中,CPU 通过分段地址,可以同时控制多个FPGA。CPU 工作在clk_cpu 时钟域下,FPGA1 工作在clk1 时钟域下,FPGA2 工作在clk2 时钟域下。clk_cpu、clk1、clk2 三个时钟的工作频率可能相同也可能不同,相位固定也可能随时变化。由于现在宇航产品实现的功能越来越复杂,多数情况下,CPU 与FPGA工作在不同的时钟频率下,属于多时钟域设计。因此,控制信号、地址信号、数据信号在CPU 与FPGA 产品之间传输时,必须进行跨时钟域处理来避免亚稳态问题。

2 CPU 总线通信常见同步设计方法

跨时钟域数据总线的传输,数据的使能信号通过握手信号完成,握手信号是源电路声明它的请求信号,目的电路检测到该请求信号有效后,会有应答,请求信号有效的过程中数据是稳定的[5]。

CPU 总线通信中,FPGA 顶层输入的控制信号、地址和数据信号来自于CPU 所在的时钟域,与FPGA 内部的时钟域为异步时钟域,因此需要进行同步设计来避免亚稳态问题。

通过握手协议可以仅对请求信号和应答信号进行同步,使得并行数据有足够的时间满足建立时间和保持时间的时序要求[6]。握手协议常用于解决并行总线通信的同步问题。如图2 所示,写使能信号进行同步处理后,通过判沿操作,找到写使能下降沿的位置(虚线处),此时多比特的地址和数据信号,处于稳定状态,满足建立时间和保持时间的要求。通过握手协议,可以解决CPU和FPGA 工作在不同时钟域可能导致的亚稳态及采样数据错误等一系列问题。

图2 CPU 总线写时序Fig.2 Writing cycle for CPU-bus

3 握手协议存在的安全隐患

常见的CPU 总线通信同步设计中,仅对控制信号进行同步处理,可能导致综合及布局布线后,未进行同步处理的地址和数据信号,通过一系列组合逻辑后,直接参与到FPGA 内部触发器的使能端或数据端。由于传输路径的延迟不同,在组合逻辑的输出处出现竞争和冒险[7],导致在地址和数据的跳变处使得相关触发器的使能端或数据端出现毛刺。

下文以实际项目为例,说明常见的握手协议存在的安全隐患。

3.1 功能仿真结果

FPGA 内部触发器的约定地址为16'h70B9,数据总线不为0 时,触发器o_tx_Send[4]输出1。前仿真结果显示,FPGA 内部对写使能进行了同步处理,之后在写使能下降沿的位置(如图3 所示的竖线处)判定地址i_cpci_addr 并获取数据总线io_cpci_data 的内容,此种情况下地址和数据均处于稳定状态且余量充足。CPU 与FPGA 可以正常通信,指令响应正确。

图3 在写使能下降沿处判断地址及数据Fig.3 Access the address and data at the negedge of writing-enable

3.2 时序仿真结果

在功能仿真的基础上,对布局布线后的网表开展时序仿真工作,总线通信异常,具体如下:

CPU 在对其他触发器地址(16'h3a0a)进行写操作时,在地址线i_cpci_addr、数据线io_cpci_data 跳变处,触发器r_TxSend[4]的使能端(N_343)和数据端(N_256)产生了约4ns 的毛刺,使能端(N_343)和数据端(N_256)的毛刺出现在时钟上升沿附近,且被时钟上升沿采到,输出端(w_BusTxSend[4])值被改变(如图4 所示的竖线处)。

图4 无关地址跳变,触发器输出改变Fig.4 Not-related address changed,the output of flip-flop is changed

3.3 故障分析

进一步对故障的情况进行分析,在布局布线后的网表中对使能信号进行追溯,使能信号N_343 产生的逻辑如下:顶层输入的地址w_Addr_c_0[7:0]和数据Io_cpci_data_in_0 经过一系列的组合逻辑,直接到达r_TxSend[4]的使能端,由于顶层输入的地址和数据与FPGA 内部的采样时钟为异步关系,地址和数据在跳变时由组合逻辑竞争冒险产生的毛刺,如图5 所示,有一定的概率被时钟上升沿采到。

图5 使能端产生毛刺Fig.5 The burr at the enabe port of flip-flop

4 总线通信同步设计改进措施

在CPU 内总线读写时序余量充足的情况下,可以通过对多比特的地址线和数据线用FPGA 内部时钟打拍的操作,来解决经过组合逻辑后地址和数据跳变产生的毛刺不可控问题。

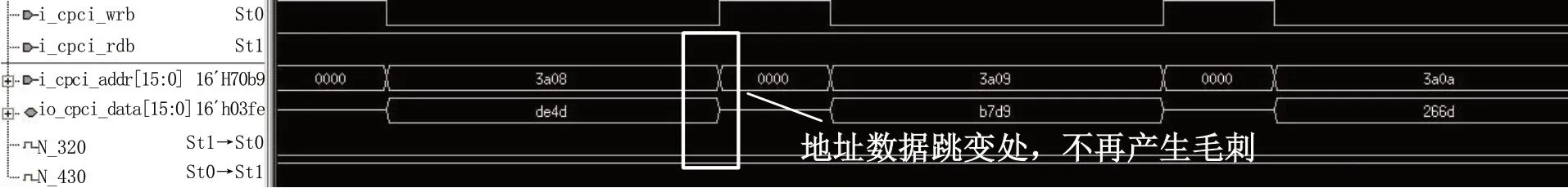

对并行的地址线和数据线打拍处理后,在此基础上,重新布局布线进行时序仿真,FPGA 内部触发器r_TxSend[4]的使能端(N_403)和数据端(N_320),在无效地址和无效数据跳变时,不再产生毛刺。时序仿真波形图如图6 所示。

图6 使能端不再产生毛刺Fig.6 No burr at the enabe port of flip-flop

5 结论

本文以CPU 总线通信中的写时序为例,提出了在CPU 时序余量充足的前提下,通过对多比特的地址和数据进行同步处理,以此来避免常见的握手协议存在的安全隐患。改进后的同步设计方法,使得CPU 总线通信更安全可靠。