基于BGA技术的多功能LC滤波器三维组装设计

2023-05-05常青松袁彪白锐魏少伟许景通

常青松 袁彪 白锐 魏少伟 许景通

(中国电子科技集团公司第十三研究所 河北省石家庄市 050051)

LC 滤波器是现代雷达接收机中应用最广泛的一种滤波器形式。与其他滤波器相比,它具有工作频率范围宽、Q 值高、相对频带宽、拓扑结构灵活、可调试、成本低等诸多优点。在低频段电路中非常适合设计宽带或窄带滤波器[1-2]。

由于LC 滤波器采用电感、电容等集总参数元件,再考虑工艺限制、可靠性、封装等要求,滤波器的电路结构体积较大。尤其在实现多功能的滤波器电路组件中,LC 滤波器的体积、集成度、小型化、工艺兼容性以及电路布局方等面都受到了影响和限制。

BGA 封装技术是一种先进的高性能封装技术。利用焊球或焊凸点作为引线,成阵列分布于封装或基板底部平面上。主要特点是电性能好、密度高、可靠性高、成品率高、适应范围广等特点[4]。随着多层基板堆叠技术及微组装工艺技术的进步,利用BGA技术实现的多层基板组装,是实现产品小型化的重要技术途径。

本文基于BGA技术设计了一种高集成小型化LC滤波器组装方法。利用BGA 基板三维堆叠,将LC 滤波器实现三维立体组装,同时集成放大、数控衰减等芯片电路功能。同时对三维组装过程中的工艺技术进行分析和研究,从而提供了一种有效的LC 滤波器三维组装架构方案。

1 多功能LC滤波器三维组装设计

1.1 三维立体LC滤波器设计

产品里包含三个LC 滤波器,窄带LC 滤波器中心频率为720 MHz,工作带宽±20 MHz,采用一个7 阶带通滤波器设计;宽带LC 滤波器中心频率为750 MHz,工作带宽±200 MHz,采用一个6 阶和一个5 阶带通滤波器设计。

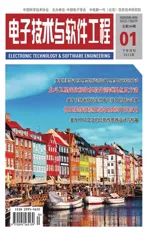

三维立体LC 滤波器主要由两个多层微波基板、BGA焊球和电容电感元件组成。电容元件采用贴片电容,焊接到下层基板;利用三维集成及BGA 工艺,使两个基板实现立体堆叠组装;基板采用盘中孔工艺,可实现通孔与焊球直接连接;电感元件最后焊接到上层基板上。上下基板通过焊球和基板内的通孔实现信号垂直传输和信号接地。同时,BGA 焊球还可起到基板间高度控制、信号地连接、屏蔽隔离等作用[5]。采用BGA技术实现的立体LC 滤波器电路结构如图1所示。

图1:立体LC 滤波器电路结构示意图

由图1 可以看出,电容元件全部装配在下层基板,与电感元件分离,可使电路布局更加合理紧凑。同时,电感元件装配在上层基板,避免与电容元件出现共用焊盘,提高了空间利用率,显著缩小了滤波器的电路面积。

1.2 多功能三维LC滤波器集成设计

三维集成技术不仅可以缩小LC 滤波器的结构尺寸,还可以集成其他功能电路和器件,进一步提高LC 滤波器的集成度,实现多功能和小型化的设计架构。

在电路设计中,微波器件以及体积较小的元器件,如芯片、贴装元件等装配到下层基板上,采用贴装或键合等方式与电路连接;无源、体积较大且需要调试的元器件,安装在上层基板上,通过BGA 焊球和基板通孔实现与下层电路的信号连接。BGA 焊球采用直径0.5 mm 的锡球,间距设计为焊球直径的1.6 倍或以上。电容元件采用0402 贴片电容,元件高度约0.508 mm,高于焊球高度,在设计下层基板电路时,把电容元件集中分区排布,在上层基板底层对应电容区域位置,进行开槽处理,给电容元件留出空间余量。

多功能LC滤波器三维集成电路设计结构如图2所示。

图2:三维集成电路结构示意图

由图2 可以看出,下层基板电路主要集成芯片和LC 滤波器电容元件。上层基板电路主要集成LC 滤波器电路中的电感元件,如磁环电感和绕线电感元件。采用三维立体LC 滤波器设计方法,可显著缩小LC 滤波器的电路尺寸。同时电容与电感元件的分离,可以使电容元件的布局更加紧凑,电感元件便于安装和后期性能调试。

2 BGA基板堆叠工艺技术

2.1 三维组装工艺流程

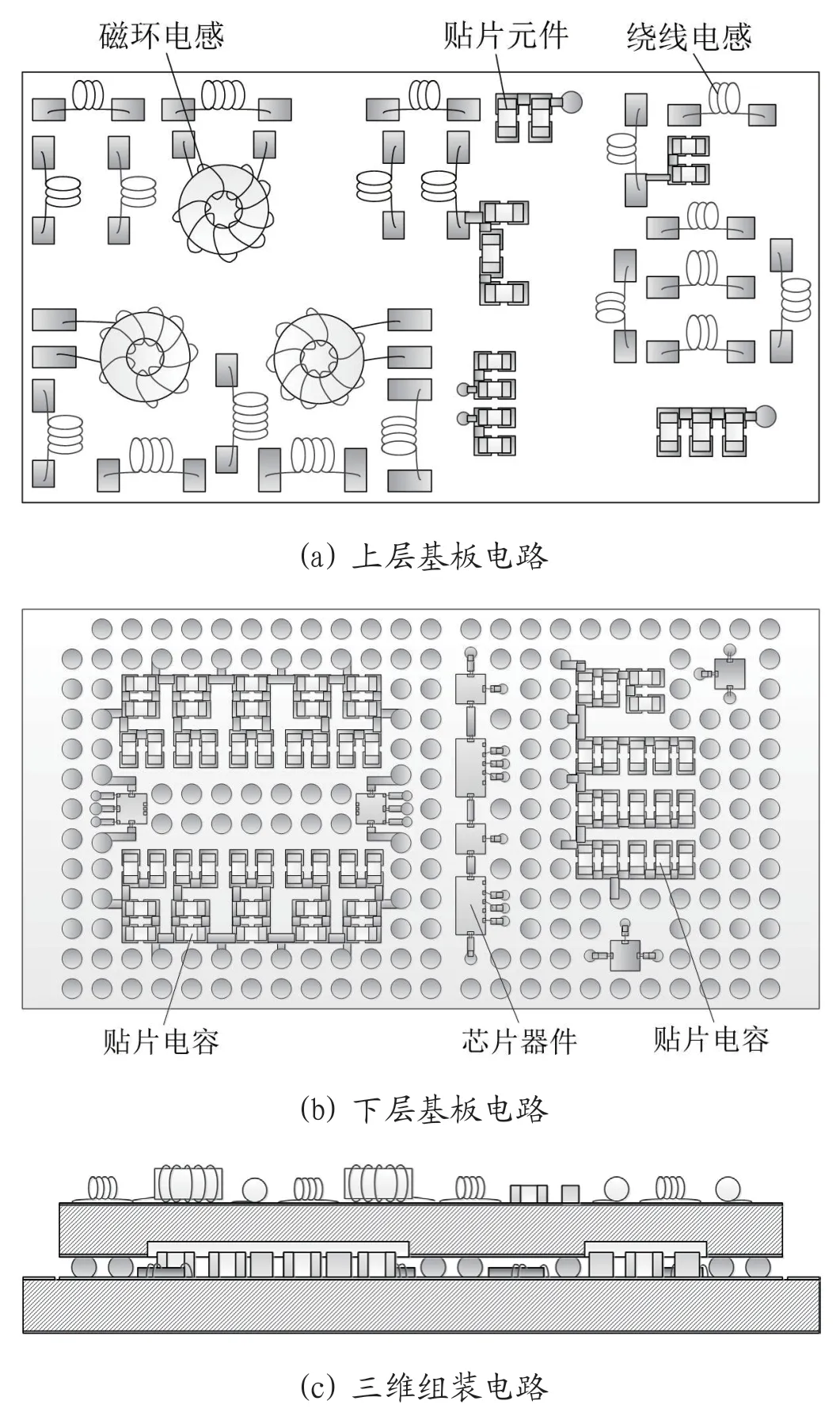

先完成下层基板上的元件器装配,电容元件采用回流焊工艺组装,芯片类器件采用胶粘方式固定在对应焊盘上,再进行键合连接和初步测试;对上层基板进行BGA 植球;采用倒装焊工艺使上层基板和下层基板堆叠固定;再焊接上层基板的元器件。最后把多层电路装配到对应封装中,键合连接到封装的引脚或端口,进行调试和测试。工艺流程图如图3 和图4所示。

图3:三维组装工艺流程图

图4:植球工艺流程示意图

2.1.1 下层基板元件的焊接和贴装

采用SAC305 锡膏焊接0402 片式元件至下层基板,点涂锡膏采用自动点膏机点涂的方式,生产效率高,一致性好。元件贴装采用自动贴片机进行贴装,回流焊采用SMT 氮气回流焊设备。

采用导电胶粘接芯片至下层基板,点涂导电胶采用自动点胶机点涂的方式,生产效率高,一致性好。贴装芯片采用自动贴片机进行贴装,固化采用链式炉进行固化,固化条件为150℃,3 小时。根据不同的芯片类型采用不同规格金丝进行芯片与芯片、芯片与基板进行互连。

2.1.2 上层基板元件焊接和植球

采用SAC305 焊料焊接片式元件至上层基板(正面),该工艺过程可与下层电路装配过程并行,上层电路采用SMT 工艺整板贴装的方式,生产效率高,质量一致性好。

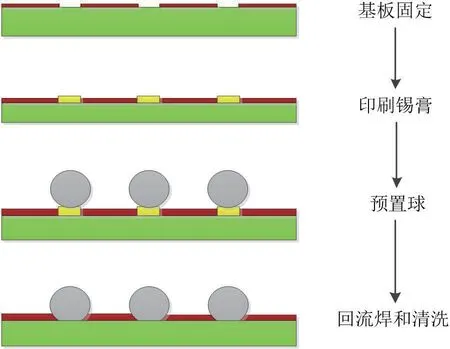

植球工艺为采用全自动植球机将助焊剂/焊膏采用钢网印刷的方式印刷至基板的焊盘处,再将锡球预置到焊盘上,锡球通过助焊剂/焊膏的粘性,固定在基板植球焊盘上,再过回流焊炉,将锡球焊接至焊盘上,通过清洗工艺清洗掉残留的助焊剂。如图5所示。

图5:基板植球后效果图

2.1.3 上下基板倒装焊堆叠

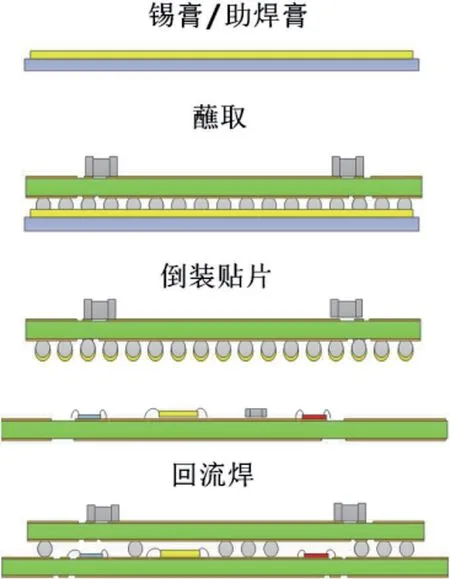

倒装焊堆叠分到倒装贴片和回流焊两步,倒装贴片采用转印锡膏或助焊膏的方式,将上层基板贴装至下层基板上,参考上下层基板的对位标识保证位置精度,回流焊采用SMT 氮气回流焊设备。如图6所示。

图6:倒装焊工艺流程示意图

2.2 关键工艺技术

2.2.1 BGA 焊盘定义方式

目前常用的焊盘定义方式有两种,金属定义焊盘(NSMD)和阻焊定义焊盘(SMD),金属定义焊盘通过蚀刻限定而成,因此该连接盘周围与阻焊膜有间隙,与绝大部分表面贴装连接盘类似。SMD 焊盘是由阻焊膜部分覆盖在金属焊盘上。这两种连接盘类型各有优缺点SMD 焊盘的主要缺点是焊点在阻焊膜和焊料交界处的脆弱性。实际试验表明阻焊定义焊盘的焊点疲劳寿命远小于金属定义焊盘。采用 SMD 连接盘的主要优点是可预防连接盘从印制板上剥离。连接盘剥离,也被称为焊盘坑裂,通常发生于角落焊球。因为角落焊球有较大的应变率而更容易失效,因此通常不会将边角处焊球用作关键功能。在角落焊球为非关键功能的情况下,这些焊球的相应位置可设计为SMD 连接盘。如图7所示,A 点为有应力集中的 SMD 焊点,B 点为没有应力集中的NSMD 点。

图7:BGA 焊点示意图

2.2.2 BGA 焊球的空洞率控制

为了建立起 BGA 空洞率的工艺控制,首先了解组装过程中哪些工艺参数会影响空洞的形成。组装后焊点中发现的空洞通常被称为制程空洞,也被称为大空洞。制程空洞通常由助焊剂和焊膏中的挥发成分演变而来。同时也有可能在封装基板植球的过程中产生空洞。组装后影响焊点空洞级别的参数包括:再流焊时间和温度曲线、焊膏配方、焊膏量、焊盘污染、多次回流等[6-7]。

空洞发生频率和大小的变化表明应该有工艺控制以及工艺和材料改进的需要。因此一定要采用空洞的控制基准线确定工艺调整的需求以控制空洞发生频率和大小。另外,需要建立空洞大小限值。确定空洞大小关系到焊球。超过焊球横截面直径25%的空洞大约为整个投影面积范围的6%。当焊球中的空洞数不止一个时,应该将空洞的尺寸相加以计算焊球中总空洞率。

3 LC滤波器测试结果

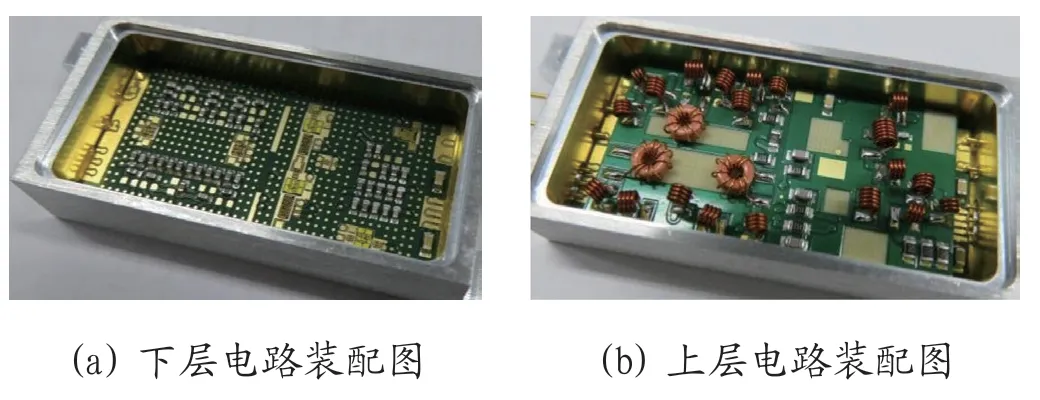

利用本方案的集成工艺,实现了高集成小型化的多功能LC滤波器电路,体积为40 mm×20 mm×9 mm,产品如图8所示。

图8:三维集成LC 滤波器实物图

由图8 可以看出,采用三维组装的LC 滤波器设计,可显著缩小LC 滤波器的电路尺寸,电容与电感元件的分离,可以使电容元件的布局更加紧凑,电感元件便于安装和调试。同时可集成多个器件,实现多功能电路。

经性能测试,产品性能测试结果也符合指标要求。因为采用了LC 滤波器三维组装设计方法,电感元件在上层电路,可对电感元件进行更换和电感值的精确调整,滤波器的抑制度会有明显改善。同时,由于各滤波器的电容元件由BGA 焊球实现空间隔离,电感元件位置也间距较大,各滤波器之间没有形成串扰而影响滤波性能。

4 结论

基于BGA技术设计的多功能LC滤波器三维组装设计,是实现LC 滤波器小型化和高集成话的重要技术方式。本文分析了三维立体LC 滤波器设计方法和BGA基板在三维组装过程中的工艺实施过程,并提出了切实可行的解决方案。经过工艺验证和性能测试,利用BGA 实现LC 滤波器三维组装设计是实现产品小型化和多功能的有效技术途径。