基于千兆网的时间确定性网络设计

2023-03-24曹庆年郑博孟开元穆伟

曹庆年 郑博 孟开元 穆伟

关键词:确定性网络;RGMII接口;千兆以太网;MAC帧;节点;高并发

1 引言

在航空航天、工业控制、自动驾驶、远程医疗等对网络实时性要求比较苛刻的通信领域,需要将端到端的时延控制在微妙级,可靠性控制在接近百分之百。而传统的网络采用事件触发的方式,端系统采用竞争访问的方式,使得网络的实时性和确定性较差[1]。确定性网络在现有网络基础设施上,借助SDN、节点控制与转发扩展等技术机制,提供确定性网络服务,与现有网络其他业务和设施兼容,可对5G场景下超低时延、超可靠连接场景提供有效的支撑[2]。

早前,维也纳技术大学便提出时间触发以太网(TTE) 技术,旨在改变传统以太网基于事件触发的传输模式。该技术是局域网首个时间确定性网络组网技术,主要通过调度业务的传输时刻,保障业务的时延[3]。文献[4]研究时间的分区技术,可以提高IMA体系网络的带宽利用率。文献[5]在OPNET网络仿真的基础上,采用网络演算理论,分析了TTE网络的性能。

本设计采用了多节点收发的功能,将全部节点分为1个时钟同步主端(MC) 节点和多个时钟同步从端(RN) 节点。在消息发送的时候,MC节点可以向其他节点提供系统标准时间,RN节点将本节点的时间同步至系统时间,实现多设备之间数据的可靠传输,更适合千兆以太网等高速传输场合。

2 总体设计方案

2.1 系统结构设计

该设计包括一路2.5G、4LANE的PCIe接口、一路RGMII接口的1000MHZ以太网MAC接口,在发送端支持至多可配置的64 条控制/状态消息和8 条流消息、接收端支持可配置的64条控制/状态消息和8条流消息。外围接口电路包括PCIe接口、以太网MAC接口;内部模块包括DMA模块、发送控制模块、接收控制模块、寄存器模块、通道配置寄存器组模块。PCIe空间包括BAR0、BAR1、BAR2三个空间,BAR0用于PCIe内部的寄存器,BAR1和BAR2基地址可配置,系统结构设计如图1所示。

主要功能特性:

(1) 支持一路2.5Gbps 4Lane的PCIe2.0主机接口;

(2) 具有一路RGMII 接口的千兆以太网MAC 接口,支持与RGMII接口的千兆以太网PHY芯片通信;

(3) 支持通过配置表实现数据收发管理,配置表存储在主机FLASH,上电后由主机写入芯片;

(4) 支持两种数据帧格式,包括64路控制/状态消息(数据包长度至多128字节)和8路流消息(数据包负载长度至多1416字节);

(5) 提供DMA寄存器,供主机填写存储流消息的主机地址、长度和启动三个参数,主机填写启动后电路自动将数据负载搬运至主机指定内存地址;

(6) 支持以太网数据包接收过滤功能,主机可设定过滤的消息ID,芯片将自动对接收到的以太网数据包按照消息ID进行过滤;

(7) 发送和接收的以太網数据包均支持单播、多播、广播。

2.2 数据包格式

2.2.1 MAC 封装

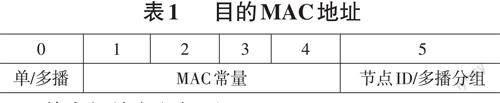

1) MAC地址的目的地址如表1所示。

其中相关定义如下:

(1) 单/多播:选择单播时填入0x00,多播时填入0x01;

(2) MAC常量填入当前节点的MAC常量;

(3) 节点ID/多播分组:选择单播时填入目的节点的ID,选择多播时填入目的节点的多播分组。

2) MAC地址的源地址如表2所示。

其中相关定义如下:

(1) 节点ID:填入本节点的节点ID;

(2) MAC常量填入当前节点的MAC常量。

2.2.2 STOF(传输起始包)帧格式

其中相关定义如下:

(1) 目的地址使用的地址是广播地址,为0XFFFFFFFFFFFF;

(2) 源地址为MC节点的MAC地址;

(3) 长度/类型字段填充长度为0X002E(ETH数据包最小包长度),实际有效数据长度为5个字节;

(4) 帧类型填充0x01,指示为STOF帧;

(5) 4个字节的节点状态指示当前网络中节点上线状态;

(6) 填充字段使用0x00。

2.2.3 SNM(系统网络管理包)帧格式

其中相关定义如下:

(1) 目的地址使用MC节点的MAC地址;

(2) 源地址使用RN节点的MAC地址;

(3) 长度/类型字段填充长度为0x002E(ETH数据包最小包长度),实际有效数据长度为2个字节;

(4) 帧类型填充0x02,指示为SNM帧;

(5) 节点ID填充RN分配的节点ID号;

(6) 填充字段使用0x00。

2.3 数据流程

2.3.1 数据包发送流程

数据包发送流程如下所示:

(1) 上层软件上线后配置设备ID寄存器、MAC地址常量定义寄存器、节点状态发送偏移寄存器、状态/控制消息发送通道偏移寄存器、流消息发送通道偏移寄存器、流消息发送通道数据存储地址寄存器;

(2) 上层软件配置设备工作模式寄存器为正常工作模式,系统上线;发送控制/状态消息参见第(3)步,发送流消息参见第(4)步;

(3) 上层软件配置状态/控制通道发送缓冲区,填入数据包PAYLOAD(负载),之后填写状态/控制消息发送通道缓冲占用标志寄存器,填入PAYLOAD存放位置,之后填写状态/控制消息发送通道配置寄存器,填入数据包关键参数,之后读取状态/控制消息发送通道配置寄存器VLD(有效)位,直到此位段位0;

(4) 上层软件在主机软件可读可写区域填入数据包PAYLOAD,之后填写流消息发送通道数据存储地址寄存器,填入PAYLOAD存放位置,之后填写流消息发送通道配置寄存器,填入数据包关键参数,之后流消息读取发送通道配置寄存器VLD位,直到此位段位0。

2.3.2 数据包接收流程

数据包发送流程如下所示:

(1) 上层软件上线后配置设备ID寄存器、MAC地址常量定义寄存器、节点状态发送偏移寄存器、状态/控制消息发送通道偏移寄存器、流消息发送通道偏移寄存器、流消息发送通道数据存储地址寄存器中断屏蔽寄存器;

(2) 上层软件配置设备工作模式寄存器为正常工作模式,系统上线;

(3) 上层软件等待中断,当收到中断时,首先配置中断使能寄存器为0,之后读接收消息信息FIFO状态寄存器;

(4) 读接收消息信息FIFO,判断当前接收包类型、消息号、长度等参数,若当前数据包类型为控制状态消息,参见第(5)步,否则,参见第(6)步;

(5) 根据消息号和长度读相应状态/控制通道接收缓冲区;

(6) 根据消息号和长度读流消息接收通道数据存储地址寄存器,根据读得的数据读主机内存相应地址;

(7) 写中断状态寄存器REV_MSG位段为1,清除中断。

2.4 硬件电路设计

该设计采用Zynq-7000 MZ7035FA开发板作为控制芯片,用户可以基于核心板设计功能底板,降低项目底板设计难度和生产成本,加速项目开发。具有多个高性能接口,4路PCIE2.0接口,3路千兆网口,4路DDR接口,可以充分满足该设计的需求。

2.4.1 RGMII 接口电路

RGMII 时钟频率为125MHZ,TXD/RXD(发送/接收)数据宽度为4位。该接口为了保持1000Mbps的传输速率不变,在时钟的上升沿和下降沿都采样数据。发送方向,时钟通过1 个DCM 和4 个BUFG 驱动相位为0、90、180、270 的4 种时钟。接收方向,线路时钟通过1 个DCM 和2 个BUFG 恢复相位为0°和180°的2 种时钟[6]。

RGMII以太网芯片集成在核心模块上,将发送控制模块发送的数据整理后转换时序送至千兆以太网MAC模块。如图2为RGMII接口电路时序。

2.4.2 PCIE 接口电路

PCIe2.0 是全双工串行总线,在物理层使用8B/10B 编码[7],PCIe2.0 x 1 的带宽= (5Gb/s x 2(双向通道)) / 10bit = 1GB/s。PCIe连接可以通过增加通道数扩展带宽,通道越多,速度越快,在该设计中最多使用4通道。各设备之间,数据传输都是以Packet形式进行的。数据从一组信号线上发送,在另一组信号上接收。设备的各个端口使用差动驱动器和接收器,采用差分对进行收发。在本文中,主機通过PCIe总线从接口访问内部的地址空间包括各个寄存器、发送缓冲区、接收缓冲区。事务层根据上层(软件层或者应用层)请求的类型、目的地址和其他相关属性,把这些请求打包,产生TLP。然后这些TLP往下,经历数据链路层、物理层,最终到达目标设备[8]。

PCIe接口电路的AC耦合电容要求靠近发送端放置,取值范围在75~200nf;差分线阻抗要求为:68~105R,一般按照100R±10%设计;差分数据信号线尽量做到等长,长度差控制在10mil 以内。如图3 为PCIE接口电路。

2.5 实验结果

为了验证具体的设计功能,需要搭建自动化仿真验证平台,从而进行功能仿真。在VNC 下使用Ca⁃dence NC Simvision15.1仿真验证工具[9],如图4为仿真验证结构。

(1) 注入激励用于驱动主机模型;

(2) 主机模型驱动PCIe主设备模型和ETH主设备模型;

(3) PCIe主设备模型用于向待测模块发送寄存器读写请求和MEM(存储器)读写请求;

(4) ETH主设备模型用于发送和接收以太网接口的数据包。

2.5.1 以太网发送数据包仿真

仿真步骤如下:

(1) 主机通过PCIe向以太网发送DATA发送STOF数据包,并对参数进行配置,DATA_LENGTH(数据长度)分别为32’h00000010,32’h00000014,32’h00000100,32’h00000200,32’h00000300,32’h00000400,32’h00000404,32’h00000588;

(2) 等待数据包接收完成,判断数据包的IP地址与写入的是否一致;判断数据包的UDP地址与写入的是否一致;

(3) 判断数据包的最高8位是否为8’h00,是则为单播,否则为多播。如图5,仿真后在波形图中读到的值与写入的值相同,符合要求。

在开发板上进行测试,数据缓冲区中的数据与发送的数据一致。将数据长度传入接收地址,在软件中进行抓包,接收地址中的数据与发送的数据一致,如图6所示为抓包数据。

3 结论

相比传统的事件触发的传输模式,本文介绍的多节点收发传输方式可以实时获取时钟主端节点和时钟从端节点的系统时间,极大地保证了系统的实时性、可靠性。由于FPGA硬件具有并行优势,在一个时钟周期内,可以完成更多的处理任务[10]。并且搭载的开发板IO 口数量多、可编程、开发灵活;具有丰富的IP核,可以缩短周期,提高稳定性。每个数据帧都有8B/10B 和CRC 循环校验来增加系统的抗干扰和检错能力。最后实现的基于千兆网的时间确定性网络设计提供实时数据传输,保证确定的通信服务质量,可以满足大多数的高速设备的数据传输。