一种微型化通用数据采集控制模块的设计与实现

2023-02-13郁文君李文学

郁文君 李文学 张 恒

(中科芯集成电路有限公司)

随着半导体技术的发展,芯片集成度越来越高,尺寸越来越小,电子设备的设计也随之具备了高性能、低功耗和便携的特点。

为了满足信息化时代工控系统对高精度数据采集系统的通用性、通信实时性、系统可靠性和微型化的需求,提出一种微型化通用数据采集控制模块的设计方案。 控制模块是整个系统的核心, 但目前国内市场上很少有成熟的设计方案,并且存在兼容性差、 选型困难及开发困难等问题;FPGA和ARM处理器广泛应用于工业控制、医疗设备、航空航天等领域,芯片拥有成熟的BGA封装形式,使得应用中可以将设备设计得更加小巧[1]。 控制模块集成了EMMC,用于信号数据存储,便于在断电后重启设备的情况下能够获取历史采样数据,实现信号的实时处理或离线处理模式, 此外控制模块还集成了丰富的总线接口,包括以太网和USB接口,用于实现数据的高速传输,CAN、RS232、RS422及RS485总线接口用于特定总线类型的数据传输。

1 硬件设计

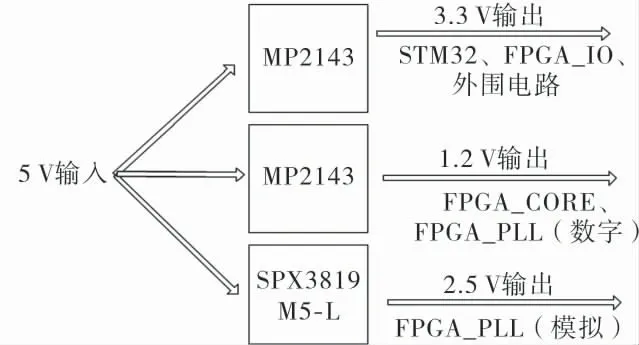

1.1 电源

控制模块支持外部5 V主电源输入。STM32及外围电路电源电压3.3 V, 由电源管理芯片MP2143提供,输入电压2.5~5.5 V,最大输出电流3 A。 FPGA内核电源电压VCCINT_1.2V以及锁相环数字电源电压VCCD_PLL_1.2V由电源管理芯片MP2143提供,中间通过磁珠隔离。 锁相环模拟电源电压VCCA_2.5V由SPX3819M5-L提供, 最大输出电流500 mA。端口电源电压3.3 V与STM32电源共用[2]。 电源模块架构如图1所示。

图1 电源模块架构

1.2 STM32处理器

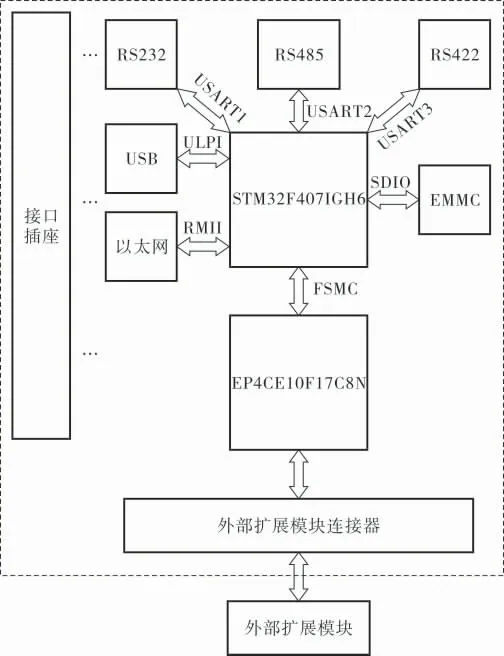

本系统采用STM32F407IGH6作为核心处理器,该处理器集成ARM CortexTM-M4 32位的RISC内核,最大工作频率168 MHz,使用通用接口GPIO、通用同步/异步串行接口USART、CAN总线控制器接口、USB高速外设接口、 以太网控制器接口、SDIO接口以及灵活的静态存储控制器接口FSMC。

STM32处理器接口外接器件型号及功能如下:

a. 通用GPIO,外接LED灯,用于控制模块各功能指示。

b. 通 用 同 步/异 步 串 行 接 口USART1、USART2、USART3,分别外接RS232、RS485和RS422收发器,RS232收发器型号为MAX3232EUE+T,RS485收发器型号为MAX3485EESA+T,RS422收发器型号为MAX1487EESA+T;RS232总线可用于多控制模块之间点对点的命令数据传输,特点是传输数据量少、 传输距离短以及传输速率较低。RS485总线可进行采样数据的传输, 由于采用平衡发送和差分接收接口标准, 可进行多节点通信,加之使用差分信号传输,具有极强的抗共模干扰能力,同时RS485总线收发器灵敏度很高,可以检测到低至200 mV的电压,故传输信号经过千米以上的衰减后都可以完好恢复。 但RS485总线是半双工工作方式,想要在数据接收的同时进行数据发送, 可以使用全双工工作方式的RS422总线,RS422总线特性与RS485相似[3,4]。

c. CAN 总线控制器接口外接CAN 收发器TJA1050,支持CAN2.0B协议,支持标准帧和扩展帧。 可用于特定CAN总线接口数据传输的应用场景。

d.USB高速外设接口ULPI外接USB PHY芯片USB3300, 使用STM32 USB高速模式, 系统配置Device端口, 用于USB接口的高速数据采集与传输的应用场景[5,6]。

e. 以太网控制器接口外接以太网控制器芯片W5500, 用于以太网接口高速数据采集与传输应用场景[7]。

f. SDIO 接 口 外 接EMMC 芯 片THGBMBG8D4KBAIR,容量32 GB,用于采样数据存储。

g. 灵活的静态存储控制器接口FSMC,与FPGA连接,通过FSMC接口实现STM32处理器和FPGA的数据交互功能,采用16位独立地址线和数据线[8,9]。

1.3 FPGA

系统采用CYCLONE IV系列EP4CE10F17C8N型FPGA,器件拥有10 K逻辑单元,器件最高主频400 MHz。

在FPGA模块中,用到两个功能:硬件IO,通过外部扩展模块连接器引出,用于外接数据采集模块或其他通信数据模块等;数据处理,控制外部数据采集模块进行数据采集并进行处理(包括数字滤波等),通过FSMC总线将处理后的数据传输给STM32处理器。

整个硬件设计部分结构如图2所示。

图2 硬件设计结构框架

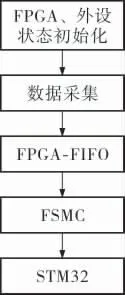

2 软件设计

整个系统软件部分设计流程分为STM32处理器部分和FPGA部分,STM32处理器部分软件设计流程如图3所示,FPGA部分软件设计流程如图4所示。

图3 STM32处理器软件设计流程

图4 FPGA软件设计流程

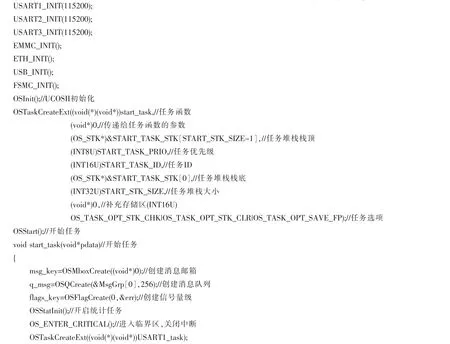

2.1 UCOSⅡ系统

在STM32使用裸机程序时, 使用一个while(1)配合一些中断来响应事件。但STM32中断资源有限,并且多用来响应外部事件。 另外,中断中使用的全局变量, 容易使系统产生硬件报错问题,造成不确定性。 而且中断处理时间不能过长,使得任务的吞吐量不能太大,而中断间的相互嵌套也容易使程序出现问题。 所以,在需要及时处理复杂或耗时任务时,这种逻辑程序的实现效果就比较差了。 而UCOSⅡ系统可以随时切换任务,每个任务的执行有固定时间,通过操作系统统一的TimeTick可以有效统一任务运行时间, 这样就不会出现一个任务长期占据CPU而其他任务得不到执行的情况,通过调用UCOSⅡ系统的API来控制每个任务的运行[10~12]。 多任务的优势是可把复杂的程序拆成几个任务,这样管理相对方便,容易修改和扩展。 通过UCOSⅡ系统的移植,分别建立多个任务,在不同任务中进行接口功能的测试。

STM32处理器的部分程序如下:

2.2 FatFs文件系统

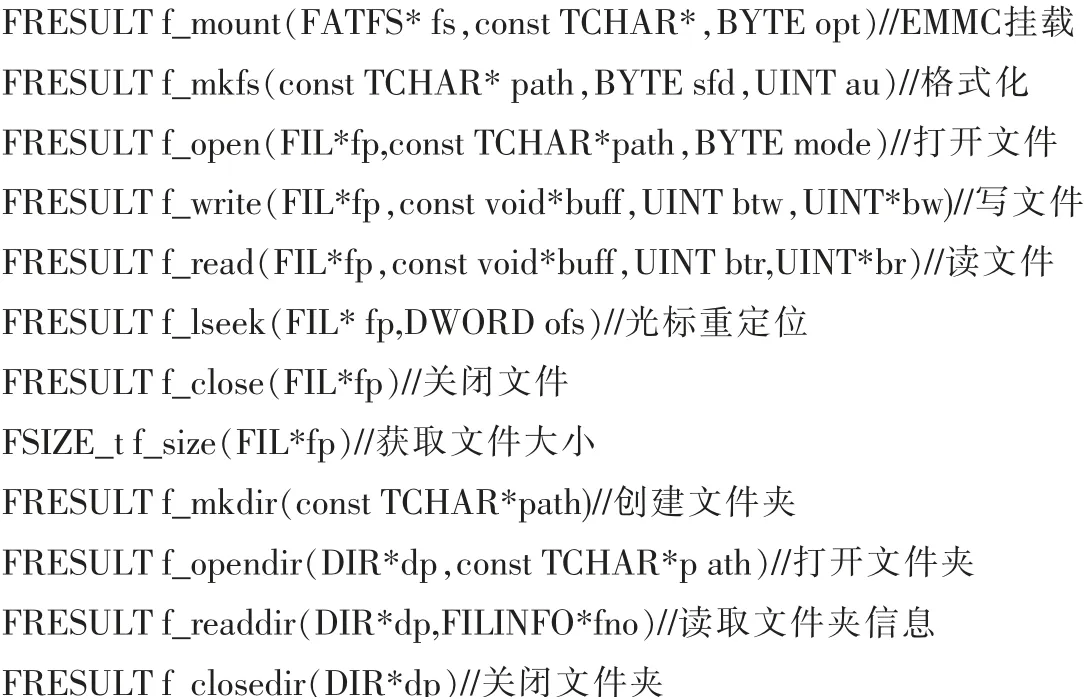

FatFs Module是一种完全免费开源的FAT文件系统模块,专门为小型嵌入式系统而设计,具有良好的硬件平台独立性。在EMMC驱动移植的基础上,加上FatFs文件系统,实现EMMC中文件的读写[13]。

FatFs文件系统可以更好地对每一次的采样数据进行分类保存,条理更加清晰。 当某次采样开始前,新建采样信息文件,包含数据类型、采样频率及物理意义等信息,在采样过程中进行数据存储,即使设备断电后,依然可以通过软件通信协议读取之前的采样数据。

FatFs文件系统相关API函数如下:

2.3 LwIP协议

LwIP实现的重点是在保持TCP协议主要功能的基础上减少对RAM的占用, 它只需十几KB的RAM和40 KB左右的ROM就可以运行, 这使LwIP协议栈适合在低端嵌入式系统使用。 LwIP支持ARP协议(以太网地址解析协议)、UDP协议(用户数据报协议)、TCP协议(传输控制协议)、DHCP协议及IP协议等[14]。

多数情况下使用UDP协议进行数据传输,UDP相比TCP传输速率快, 可进行无连接数据传输,传输安全性更高,此外UDP不仅可以和一对多连接对象间通信,还能和多对多连接对象间通信[15,16]。

如果在某些要求特别苛刻的应用场景下,也可以使用TCP协议进行数据传输,TCP协议中TCP的3次握手和4次断开机制,明显提高了数据通信的可靠性,使数据发送端和接收端在数据正式传输前就有了交互,确保数据传输过程的顺序以及数据正确性。

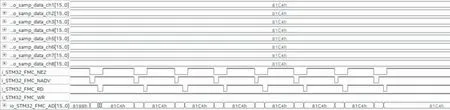

2.4 FPGA软件部分及数据传输设计

FPGA主要在于根据外部扩展模块所需的时序要求获取AD采样数据,利用FPGA自带的FIFO构造数据缓冲区,临时存储采样数据。 如果具体设计需要进行数字滤波, 可以通过FPGA内部FIR、IIR等数字滤波IP进行数据处理,并将最终得到的数据通过FSMC总线传输给STM32,处理器对数据打包发送。

通过FPGA构造8通道16位采样数据,STM32与FPGA通过FSMC总线进行数据交互的时序图如图5所示。

图5 FSMC总线数据交互时序图

下面给出部分STM32数据打包和以太网接口发送数据的代码:

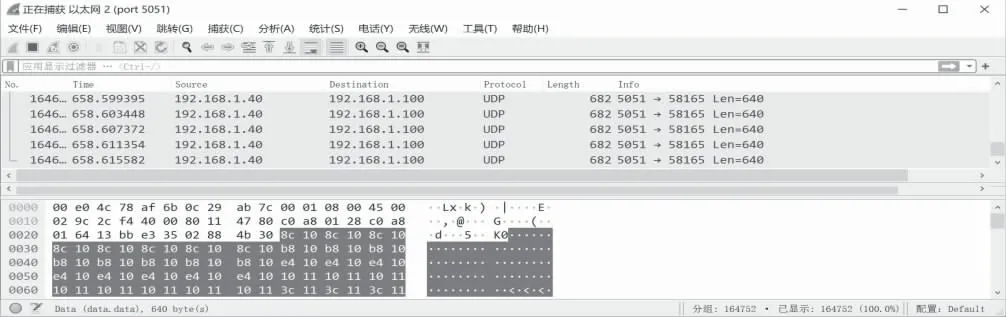

使用WireShark网络抓包工具监听网络数据传输过程, 确定当前设计数据是否传输稳定可靠。

以太网数据传输结果如图6所示。

图6 以太网数据传输结果

3 结束语

通过对笔者设计的微型化通用数据采集控制器模块设计验证, 该设计不仅能优化整体采集器尺寸大小,而且在使用了UCOSⅡ系统后使得采集器能同时处理多个任务,优化了整个采集系统,减少任务冲突。 整个控制模块集成大容量存储器,加之FatFs文件系统可以更好地对采集数据进行分类管理。 丰富的总线接口, 能够包含实际采集设备需要的大部分功能。此外STMicroelectronics公司提供了UCOSⅡ系统、FatFs文件系统和LwIP码源, 并提供了完整的移植方法, 结合官方STM32CubeMX初始化代码生成器可以协助设计者更灵活快捷地开发应用工程,提高了在数据采集应用设计上的通用性和移植性,提高了开发效率,降低了开发成本和开发周期。