基于FPGA与DSP架构的接收机设计

2023-02-10林选锋

刘 成,彭 思,林选锋

(电子信息控制重点实验室,四川成都 610036)

随着全球导航卫星系统的成熟,接收机可以不依靠于地面站而直接测量出低轨道(LEO)卫星的轨道信息,具有覆盖率高、实时性强、自主导航、低成本的特点[1-4],成为LEO 卫星轨道位置测量的主要手段之一。GPS 卫星运行在20 200 km 的高轨道上,可以为LEO 卫星提供连续、高精度的自主导航、姿态测定和时间同步等功能[6-9]。使用卫星导航系统的卫星自主定轨,既能减少LEO 卫星对地面站测控的依赖,也能大幅度降低测控成本[10]。

传统硬件接收机通常采用专用芯片(ASIC)对数字中频信号进行处理,主要过程包括捕获、跟踪以及数据解调等[2]。ASIC 处理的优点是功耗低、速度快和设计密度大,缺点是开发周期长、研发成本高和设计不灵活[11-12]。随着接收机技术的逐渐成熟,研发出各种各样包含多种功能的接收机[5]。因此,需要接收机可以灵活地适应不同的处理算法,基于ASIC 的接收机不具有灵活性[3]。为了解决接收机灵活性问题,可以采用软件无线电思想进行设计,即在硬件架构上采用通用、开放性的可编程平台,通过加载不同的算法程序实现不同的功能,将具有这种结构特点的接收机称为软件接收机[8,11]。

1 全球导航卫星系统测量原理

接收机的定位是利用到达时间(TOA)测距原理实现的[9]。TOA 测距原理需要获得卫星与接收机之间的距离,可通过传播时间乘以光速得出。如果获得了几个位置信息已知的卫星信号传递时间,接收机经过计算可求解出自身的位置信息[13]。

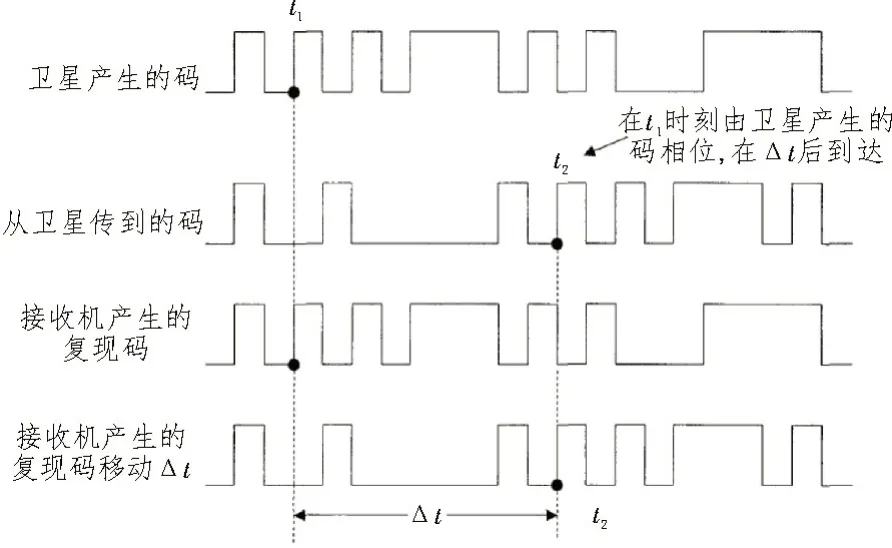

通过测量信号中的特定测距码,就可以求出接收机与卫星之间的距离[14-16]。如图1 所示,由卫星在t1时刻生成测距码相位,在t2时刻到达接收机,传播时间为Δt=t2-t1。在接收机中,在相同时间同时生成和它一样的信号,二者在时间轴上相互移动并进行相关运算,当发生最大相关时刻所移动的时间就是传播时间[14]。假如接收机时钟与卫星时钟绝对相同,说明这个相关过程将获得真正的传播时间。将这个真正的时间与传播速度相乘,就可以计算得到接收机与卫星的真正距离[15-20]。

图1 卫星码的发送时间确定

其中,测距码是由卫星按照特定规则生成的,在每个码的相同周期对应着某个特定时间。通过判断每个码的形状特征,就可求出时延τ。由于时延τ以及各种误差的影响,测量得到的距离(伪距)ρ'与卫星到接收机天线的真实距离ρ之间存在着偏差Δρ,可以表示为:

考虑到存在接收机钟差c·δtj、卫星钟差c·δtk、大气对流层延迟δp2以及电离层延迟δp1,则伪距观测量可表示为:

其中,j表示卫星编号,j=1,2,3,…;(xj,yj,zj)表示某颗卫星某时刻的位置坐标;(xp,yp,zp)表示测站点P点的位置坐标。通过对式(2)进行线性化,并按最小二乘平差求解该方程组,就可计算出定位点的位置坐标(XP,YP,ZP)。

2 实现方案

2.1 射频前端实现

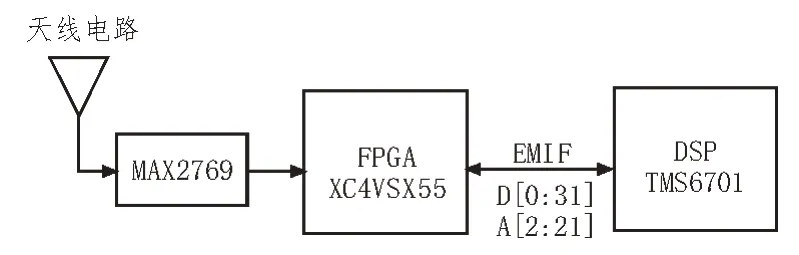

该文射频前端实现是应用于FPGA+DSP 硬件平台构架下的软件接收机,将接收到的射频模拟信号变成频率较低而且包含有信号的数字中频信号。该射频前端的实现方案如图2 所示。射频前端处理模块通过接收机天线接收所有的可见卫星所发射的信号;由前置滤波放大器处理之后,和本机振荡器产生的信号进行混频;通过下变频为中频(IF)信号后,经过ADC 完成模数转换。电路结构主要由MAX2769芯片外加外围电路实现,MAX2769 与后续基带处理FPGA存在接口关系,MAX2769 为FPGA 提供2 bit的信号采样参考时钟及数字中频信号,FPGA 则通过MAX2769 串口完成对其参数的配置。

图2 射频前端实现架构

基于MAX2769 的射频前端设计主要包括外围电路、前端参数设计以及芯片寄存器配置和功能实现。其中,系统采样率为31 MHz;低中频频率为4.092 MHz;中频信号输出量化为2 bit。

由于接收机接收到的干扰信号强度会比地面更强,所以为了避免天线所接收到信号中可能含有强干扰,被放大后会让电路达到饱和,因此,与天线相邻的首级器件应选择低噪声指数的前置带通滤波器,使得除了信号波段外的射频干扰和噪声前先被滤除。

多普勒频率是由于接收机与导航星径向连线上产生相对运动引起的,对于软件接收机来说,多普勒搜索范围约为50 kHz。在不考虑多普勒频移的情况下,卫星信号频谱是以1 575.42 MHz 为中心频率的sinc2函数,主峰频宽为2.046 MHz。考虑到接收机的多普勒高动态范围,防止C/A 码信号发生畸变,信号中心频率附近至少2.1 MHz 的C/A 码信号频谱必须完全通过各个滤波器,并且2.1 MHz 宽的滤波通带响应必须平稳。

2.2 FPGA设计

FPGA 主要完成基带信号处理,开发环境是ISE14.6,采用Verilog语言编程,仿真工具为ModelSim 10.1。接收机信号处理电路结构如图3 所示。FPGA与DSP 之间采用EMIF 接口交换数据。

图3 信号处理电路结构

2.2.1 捕获处理模块

为了大幅度降低捕获时间,可以考虑同时搜索全部的码相位,即通过连续平移本地产生的伪码相位,并与接收到的伪码进行相关运算,如果产生最大相关峰值时,说明伪码相位已经对齐。捕获处理的算法流程图如图4 所示。

图4 FFT快捕算法流程图

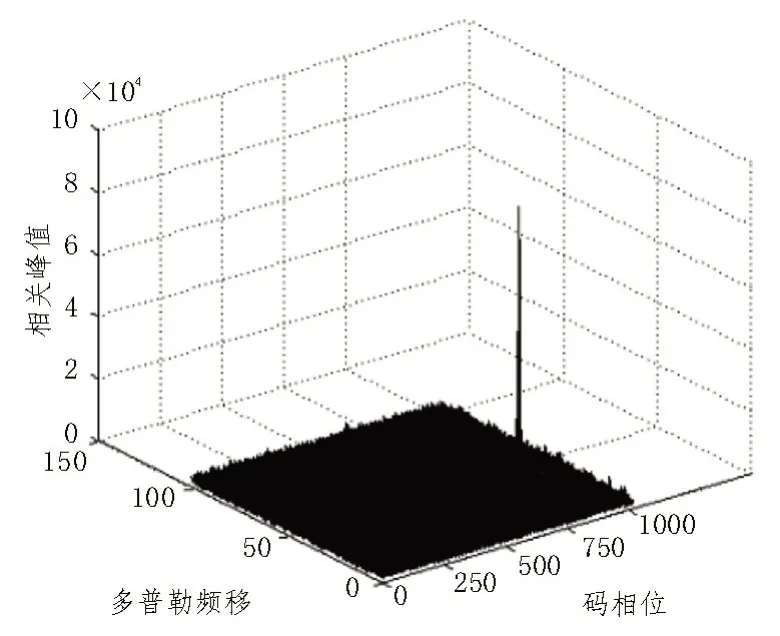

利用射频前端输出的数字中频信号在Matlab 中进行捕获仿真,捕获结果如图5 所示。多普勒频移搜索范围为50 kHz,步频为1 kHz。从图5 中能清楚地看到卫星捕获产生的相关峰值,说明捕获成功。

图5 Matlab捕获仿真结果

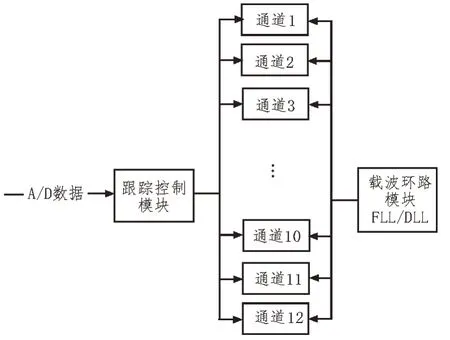

2.2.2 跟踪处理模块

跟踪模块设计12 个相互独立的通道,如图6 所示。每个通道独立输出一个卫星跟踪所需要的超前、实时、滞后码的相关值,伪码环和载波环模块进行时分复用以降低FPGA 资源消耗。在不同的时间段内遍历各个通道,分别读取某个通道超前、实时、滞后码的相关值进行伪码环和载波环的跟踪。每个通道的遍历时间在5 μs 左右,跟踪相关时间为1 ms,对12 个通道在1 ms 内完全可以遍历一遍。

图6 跟踪模块框图

2.3 DSP设计

DSP需要完成12个独立跟踪通道的控制、定位解算和数据接口的功能,对DSP 的运算能力和速度有较高的要求,根据需求选择TI公司的TMS320C6701。它是TI 公司的一款浮点运算DSP,适用于需要大量运算且实时性要求高的场合,如导航解算等。同时,在TI 公司浮点DSP 芯片中,TMS320C6701 也是一款可应用于恶劣环境(如太空环境),并具有高可靠性的产品。主控流程主要在DSP 中进行,如图7 所示。

图7 DSP捕获跟踪控制流程

接收机开始工作时,系统初始化模块对DSP、捕获模块、跟踪模块、TIC 时钟模块进行初始化。启动捕获模块工作,设置信道、捕获卫星号等信息。完成捕获后汇报捕获状态(中断),如成功则FPGA 切换为跟踪模块。跟踪模块按捕获卫星号,在给定跟踪信道进行跟踪,汇报测量信息、星历信息(中断)。

3 测试结果

该文采用GSS6560 导航星模拟器对接收机进行动态测试,导航星模拟器可以模拟GPS 星座、低轨卫星的空间运行以及导航信息,借助该仪器可以较完整地对接收机进行测试。

将GSS6560 导航星模拟器射频信号直接注入到接收机,在不考虑干扰和噪声等因素的影响下,统计得到位置均方误差为6.49 m,速度均方误差为0.17 m/s。当然,在实际情况中会受到外界噪声、接收通道噪声等信号的干扰,导致信噪比降低,精度会受到较大影响。该测试结果可以验证设计方案的有效性。

4 结束语

该文介绍了一种接收机的工程实现方案,测试结果证明了该工程方案的可行性。基于软件无线电思想而设计FPGA+DSP 的处理架构,在硬件架构上具有通用性、开放性和可重构性。在此基础上,通过加载不同的算法程序而实现不同的功能,可根据应用需求实现四大导航系统中任意的导航解决方案,也可以根据不同课题需求作出灵活调整。