一种低功耗高可靠性辐射加固锁存器设计

2023-02-02周静,徐辉

周 静,徐 辉

(安徽理工大学 计算机科学与工程学院,安徽 淮南 232001)

集成电路敏感区被空间辐射环境中的粒子撞击产生的电子空穴对被器件电极收集后,会导致集成电路发生瞬时或永久性的故障,产生单粒子效应(Single-Event Effect, SEE)[1]。单粒子效应引起的节点翻转给空间集成电路带来了很大的危害。一个粒子撞击锁存器可能会被多个敏感节点收集,从而引起多节点翻转(Multiple-Node Upset, MNU),随着存储单元之间距离的减小,多节点翻转发生的概率也随之增加[2]。为了缓解此类软错误的影响,国内外研究人员提出了多种加固方案,如版图隔离、空间冗余和抗辐射加固技术等[3]。其中,抗辐射加固技术在节省开销的同时能有效降低软错误造成的影响。常见的加固锁存器有DONUT[4],DNCS[5],TNU-latch[3],TNUHL[6-7],LCTNURL[8],QNUTL-CG[9],QNURL[10]等。目前能容忍多节点翻转的锁存器设计可靠性并不高,有的无法实现多节点翻转自恢复,有的虽然能够实现多节点翻转自恢复,但开销较大或对波动不稳定[11]。因此,本文提出一种能容忍多节点翻转包括单节点翻转(Single-Node Upset,SNU)、双节点翻转(Double-Node Upset,DNU)、三节点翻转(Triple-Node Upset,TNU)、四节点翻转(Quadruple-Node Upset,QNU)的低功耗高可靠性辐射加固锁存器QNULH。QNULH锁存器包括4个反馈模块,每个模块能够充分利用C单元的反馈锁存数据,锁存器节点通过不同的组合方式叠加模块冗余,同时使用时钟钟控技术和快速通路技术,大大减小锁存器的功耗和延迟开销。

1 QNULH锁存器概述

QNULH锁存器由4个反馈模块通过节点的排列组合形成一个环形结构,实现四节点翻转的完全自恢复。QNULH每个模块都由3个2-input C单元和3个钟控C单元组成,充分利用C单元的互锁反馈,实现数据的锁存。其中,每个存储节点都能够连接到4个晶体管,使节点产生更大的电容来存储数据,进一步提升加固可靠性。钟控技术和快速通路的使用可以降低锁存器的功耗和延迟。

QNULH锁存器结构如图1所示。图1中,TG1~TG6为锁存器的传输门;X1~X12为锁存器节点;P1~P12为PMOS晶体管;N1~N12为NMOS晶体管;D为输入,信号在X2节点输出;CLK和CLKB是系统时钟和负系统时钟。以DUT1模块为例,当CLK为1,CLKB为0时,锁存器处于透明期,6个传输门打开,输入信号D进入锁存器内部。输入D通过传输门TG1~TG3将信号写入X2,X4,X6,利用模块中C单元的反馈互锁,再将信号传输到X1,X3,X5。当CLK为0,CLKB为1时,锁存器进入锁存期,6个传输门关闭,输入信号D将不再进入锁存器内部。TG1~TG3关闭,输入信号传输路径阻断,系统时钟控制的PMOS管和NMOS管打开,对内部数据锁存。

图1 QNULH锁存器结构

锁存器仿真实验使用32 nm PTM (Predictive Technology Model)模型[12]和HSPICE仿真工具,供电电压为0.9 V,温度为27 °C,时钟频率为500 MHz。在无故障注入下,QNULH锁存器波形稳定,能够正常工作。

2 QNULH锁存器加固原理

2.1 SNU分析

当锁存器被高能粒子撞击发生单节点翻转时,以DUT1模块的X2节点为例(以下均在D为低电平时分析),其逻辑状态从低电平变为高电平,P5和P2关闭,N6和N1打开,X1和X3的逻辑值不发生改变,整个模块只有X2的逻辑值发生变化,其错误的逻辑值将会被锁存器的其他正确逻辑值的节点恢复过来,实现QNULH对单节点翻转的完全自恢复。

2.2 DNU分析

双节点翻转可以分为相邻节点对和相隔节点对2种情况。假设相邻节点对

2.3 TNU分析

三节点翻转中发生翻转的节点对可以分为5种情况:①互为相邻的节点,如

图2 QNULH锁存器在DNU和TNU故障注入下的仿真波形

2.4 QNU分析

四节点翻转中发生翻转的节点对可以分为6种情况:①4个节点互为相邻节点,如

图3 QNULH锁存器在QNU故障注入下的仿真波形

3 性能比较及PVT波动分析

3.1 加固能力比较

锁存器的加固可靠性对比见表1。从表1可以看出,DONUT和DNCS锁存器具有双节点翻转容忍性;TNU-latch,TNUHL以及LCTNURL能容忍三节点翻转,其中,LCTNURL具有三节点翻转自恢复性;QNUTL-CG只容忍四节点翻转,QNURL和QNULH锁存器既能容忍四节点翻转又能实现四节点翻转自恢复。

表1 锁存器的加固可靠性对比

3.2 开销比较

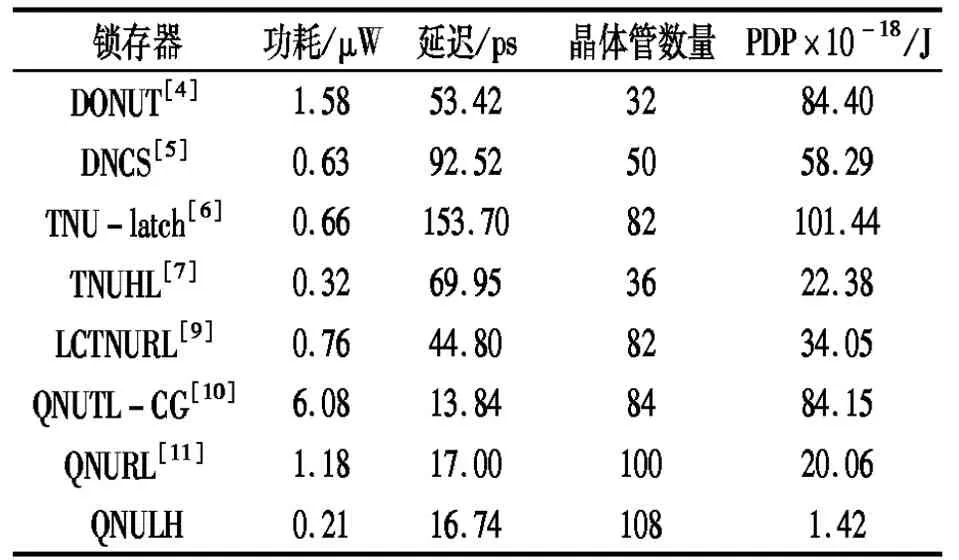

锁存器的面积开销用晶体管数量来衡量,功耗和延迟用功耗延迟的乘积(PDP)来衡量[13]。锁存器的开销对比见表2。从表2可以看出,QNULH的功耗、延迟、PDP有着明显的优势,功耗延迟积的综合性能是最优的。

表2 锁存器的开销对比

3.3 PVT波动分析

随着集成电路的发展和特征尺寸的不断降低,工艺-电源电压-温度(Process-Voltage-Temperature, PVT)波动对集成电路可靠性的影响越来越大[14]。在相同的仿真条件下,分别对QNULH的工艺、电源电压、温度的波动进行分析,观察其功耗和延迟的变化。利用样本标准差来判断变化的稳定性,数值越小其稳定性越高,反之则越不稳定[15]。样本标准差公式为:

(1)

3.3.1工艺波动分析

锁存器的工艺角分为5种,即FNFP(Fast NMOS and Fast PMOS),FNSP(Fast NMOS and Slow PMOS),TNTP(Typical NMOS and Typical PMOS),SNFP(Slow NMOS and Fast PMOS),SNSP(Slow NMOS and Slow)。5种工艺角下各锁存器的稳定性及标准差如图4所示。从图4(a)和(b)可以看出,各锁存器的功耗在FNFP工艺下最大,SNSP时最小,QNULH锁存器的功耗处于较低水平,各锁存器的延迟在FNSP时最小,SNSP时最大,QNULH的延迟也一直在较低的水平。从图4(c)和(d)可以看出,QNURL锁存器对工艺角波动最不稳定,LCTNURL最稳定,QNULH次之,但QNULH的加固可靠性优于LCTNURL。QNUTL-CG锁存器的延迟对于工艺波动的稳定性最佳,TNU-latch最不稳定,QNURL和QNULH的延迟相对较稳定。综合图4可以得出,QNULH锁存器的功耗和延迟对于工艺角波动都较稳定。

(a) 功耗变化 (b) 延迟变化 (c) 功耗标准差 (d) 延迟标准差图4 5种工艺角下各锁存器的稳定性及标准差

3.3.2电源电压波动分析

电源电压设置为0.75~1.20 V。电源电压波动下各锁存器的稳定性及标准差如图5所示。从图5可以看出,各锁存器的功耗随着电源电压的增大而增大,而QNULH的功耗在折线图中处于较低水平。各锁存器的延迟随着电源电压的减小而减小,QNULH的延迟也处在较低的水平。综上分析可知,QNULH锁存器的延迟和功耗对于电源电压波动都较稳定。

3.3.3温度波动分析

(a) 功耗变化 (b) 延迟变化 (c) 功耗标准差 (d) 延迟标准差图5 电源电压波动下各锁存器的稳定性及标准差

温度范围设置为25~65 °C。温度变化下各锁存器的稳定性及标准差如图6所示。从图6可以看出,各锁存器的功耗随着温度的增加而减小,QNULH的功耗稳定性最佳;各锁存器的延迟随着温度的增大而增大,DNCS和TNU-latch锁存器对温度变化都较敏感,QNULH的延迟较小,对温度变化也最稳定。综合图6可以得出,QNULH的功耗和延迟对于温度波动很稳定。

(a) 功耗变化 (b) 延迟变化 (c) 功耗标准差 (d) 延迟标准差图6 温度变化下各锁存器的稳定性及标准差

4 结论

设计的四节点翻转自恢复QNULH锁存器功耗低、可靠性高,能同时对单节点、双节点、三节点以及四节点翻转软错误现象进行保护。锁存器由4个反馈模块组成,模块内部结构充分利用C单元的互锁反馈,内部节点则通过排列组合结合使用时钟钟控和快速通路技术,有效降低了锁存器的功耗和延迟开销。仿真实验结果表明,与最新的四节点翻转自恢复锁存器QNURL相比,QNULH的功耗、延迟、功耗延迟积分别降低了82.22%,1.53%,92.92%;QNULH对工艺、电源电压和温度波动都较稳定,有较好的可靠性。