超大面积超导纳米线阵列单光子探测器设计与制备*

2022-12-31张笑吕嘉煜管焰秋李慧王锡明张蜡宝王昊涂学凑康琳贾小氢赵清源陈健吴培亨

张笑 吕嘉煜 管焰秋 李慧 王锡明 张蜡宝 王昊 涂学凑 康琳 贾小氢 赵清源 陈健 吴培亨

(南京大学电子科学与工程学院,超导电子学研究所,南京 210023)

超导纳米线单光子探测器(SNSPD)是综合性能最优异的新型单光子探测器之一,而传统的单像元SNSPD不具备空间分辨力,且光敏面小,光学耦合效率存在瓶颈,因此,研制大面积阵列器件是自由空间光子探测等应用的关键.然而,由于器件光敏面由大量超导纳米线组成,研发大面积的阵列SNSPD 面临工艺复杂、成品率低、制备困难等问题.本文设计了一种超大面积纳米线阵列结构,利用电子束抗蚀剂氢倍半硅氧烷(HSQ)曝光后可形成氧化硅电学隔离层的特点,仅使用简化二维工艺即可完成大阵列SNSPD 的制备,对多层结构的传统立体工艺实现了降维.器件经过行方向并联测量,未发现坏点,成品率高,且实现了基础的成像功能验证.此外,本设计中采用了全超导电极以减少电阻热效应,并在像元内增设了串并联电阻,从而均分偏置电流,同时能够可选地扩展阵列规模.本工作为超大型阵列 SNSPD 的设计与制备提供了一种思路,并有望应用于百万像素阵列 SNSPD 的制备,与高效读出电路结合实现兼备大视场和高灵敏度的焦平面光子探测与成像系统.

1 引言

超导纳米线单光子探测器(superconducting nanowire single photon detectors,SNSPDs)是一种用于快速、准确、高效地探测单光子的新型光探测器,在效率[1,2]、速度[3]、暗计数[4]、响应频谱范围[5,6]等方面极具竞争力.自2001 年Gol’tsman 等[7]首次报道SNSPD 至今,经过20 余年的发展,单像元及小阵列SNSPD 的制备工艺已相当成熟,展现出了稳定且优异的综合性能,并被广泛应用于激光雷达[8]、深空光通信[9]、量子信息[10,11]等领域.而暗物质探测[4]、空间态势感知[12]等一系列新兴应用的不断涌现,对探测成像系统的焦平面尺寸提出了越来越高的需求,一般情况下,使用的焦平面感光区域越大,扫描或凝视成像所需的时间则越短.在此背景下,单像元SNSPD 的缺陷将会凸显,其光敏面大小有限且不具备空间分辨力,若仅增加每个像元的面积而不改变器件结构,则纳米线的动态电感会随之增加,从而导致其死时间延长、探测速度降低,这就削弱了SNSPD 最根本的优势.鉴于无法在充分保证单个像元时间分辨率的同时、大幅增加其有效探测面积,进一步扩展阵列规模(增加像元数)将是SNSPD 适应新需求的关键一步.

焦平面单光子探测阵列的研制,在半导体领域已有了相当成功的实践.如单光子雪崩光电探测器(single photon avalanche diodes,SPADs)是目前具备单光子灵敏度、皮秒时间分辨瞬态成像能力的主流理想器件[13].2020 年,平面SPAD 阵列规模突破百万像素[14],像元规模大、集成度高是其突出优势,但其填充因子和量子效率相对低下,且随着节点尺寸进一步减小,光学串扰和暗计数表现也将恶化[15].尽管三维堆叠技术为新一代SPAD 阵列发展开辟了一条新道路[16],但与此同时带来的工艺挑战也不可小觑.相比之下,SNSPD 作为一种超导器件,其无需门电路,填充因子相对较高,且其具备比半导体光电探测器更宽的工作频段、更高的工作效率以及更低的暗计数率[17],此性能在阵列器件中将会得以继承,因此在一些对相关参数有极限需求的应用环境下,阵列SNSPD 将更具竞争力.

对于阵列SNSPD 的实现,读出电路的设计是主要难点之一.最直接的读出方式是将每个像元的输出分别由同轴线引出至室温外部电路[18],其读出速度快、准确率高,但随着像元数目的增加,大量的同轴线会从室温中引入过量的热,那么制冷机有限的制冷效率将限制SNSPD 像元数目的扩展.此时,直接读出变得不再可行,而能够有效减少连接线的各种多路复用架构则逐渐受到关注,如时域复用[19]、频分复用[20]、幅度复用[21]、码分复用(SFQ)[22]等读出架构.相比直接读出,它们所需的读出通道数目少,但往往需要加入额外的延迟线或电路元件,从而大大降低了像元的填充率,随着阵列规模扩展,其电路结构将更加复杂,且无论何种复用技术,都会牺牲一定量的光子信息.2014 年,Verma等[23]提出了行列复用的读出方式,仅需2N条电缆即可对N2像元的阵列进行读出,与前述复用方式相比,它能在保存绝大部分的光子信息的同时具备较高的占空比,目前已成功应用于1024 像元的SNSPD 阵列中[24],其填充率达36%,在系统效率达8%的同时也实现了一定的成像功能.由此,行列复用结构在多种读出架构中脱颖而出,展现了其在千像元量级SNSPD 阵列实现中的可能性.目前看来,对于像素数目巨大的阵列SNSPD 而言,使用行列复用的结构进行读出是最简洁有效的.

基于行列结构读出的SNSPD 阵列,在行列电极的相交处应构建必要的电学隔离,以避免行信号与列信号发生串扰.对于该结构的实现在工艺上目前存在以下几种方式.2019 年Wollman 等[24]制得的32×32 阵列SNSPD,其读出行和读出列被分别制备在两个结构层上,两层间采用全覆盖的氧化硅介电层进行电学隔离,通过对介电层穿孔、孔间填充金的方式来实现层间连接.这种工艺属于三维工艺,其复杂度及成本均较高,且在介电层上生长的超导薄膜的质量难以保证,纳米线的性能将受到介电层粗糙度等的影响.最终检测发现其实际电阻值(200 Ω)与设计值(50 Ω)之间有较大差异,此工艺下制得器件的1024 个像元中存在至少4 个坏元.2020 年,Allmaras 等[25]提出了双层热耦合行列复用的阵列结构,其同行(或同列)采用同一根纳米线,依靠双层纳米线的共计数来实现探测,可以有效地缓解行列电流的重分配问题,但与此同时,单一的微小缺陷将会影响其所在整行(或整列)所有像元的工作性能,对缺陷的高敏感度意味着对工艺的把控需要更加严格.此外,双层纳米线的制备同样引入了一定的复杂度,由于工艺问题,上层纳米线的超流往往低于下层纳米线的超流,这亦将限制器件的探测性能.总的来说,目前国际上已报道的基于行列结构的大型密集阵列SNSPD,其制备方式均涉及到立体工艺,普遍存在复杂度高、不确定度高、稳定性差等问题,我们亟需开发一种新的阵列SNSPD 的制备方法.

在本研究中,对行列复用阵列SNSPD 的立体结构实现了降维布局,展示了一种隔离层简化工艺,能够将上述介电层穿孔等三维工艺转化为二维平面工艺,有效地规避通孔制作、绝缘/阻挡/种子层沉积以及导电物质填充等复杂步骤,从而大大地提高工艺的稳定性;采用了全超导电极,在工作状态下产热更低;提出了通过在各像元内引入串联电阻,来保证器件在低温条件下工作时电流能够均匀分配.成功制备了一个32×32 像元的SNSPD 阵列,单像元尺寸为50 µm×50 µm,器件有效探测面积达1.6 mm×1.6 mm,像元占空比达44%,版图中还预设了可选择的并联电阻区域,通过添加并联电阻,每个单像元可进一步扩展为15 像元阵列(约4×4),即器件可扩展约为128 像元×128 像元的阵列SNSPD.经过测试,器件像元间均匀性表现良好,以行方向并联的方式检测其电学性能,未发现坏点,且实现了基础的成像功能验证,证明了该简化工艺的可行性,为构建更大型的高质量阵列SNSPD 奠定了基础.

2 实验部分

2.1 器件设计

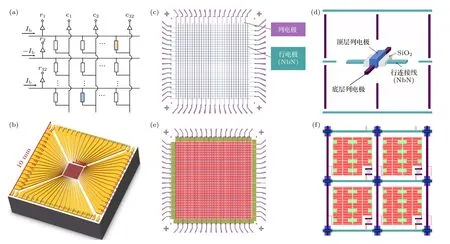

器件结构的设计和优化参考了Wollman 等[24]的设计.采用了行列复用的读出结构,作为一种典型的焦平面结构,其等效电路如图1(a)所示.器件整体尺寸为10 mm×10 mm,有效探测区域范围为1.6 mm×1.6 mm,包含了32×32 共计1024 个像元,器件由外围的64 个金电极将探测信号输出到外电路进行读出,其中32 个行输出和32 个列输出分别由探测区域的左右两侧和上下两侧交错引出,以保证结构的高度对称性(其芯片级布局见图1(b)).内部各像元则通过更加精细的行连接线和列电极相连,再进一步连接至外围金电极,如图1(c),深绿色线条为NbN 材料的行连接线,紫色线条为底层列电极(在进行超导薄膜刻蚀时该结构可视为一层掩膜,刻蚀后将保留为NbN 列电极),这意味着在低温状态下,在全方向上采用的都是超导导电而非金属导电,与传统的金属电极相比,其优势在于行连接线的厚度可以更薄,这有利于减小后续顶层结构的加工难度,以及一定程度压缩器件的垂直尺寸,同时,超导导电显然也可以提供更优越的电学性能.

图1 器件设计 (a) 行列复用结构示意图,图中的每个矩形代表一个像元,其中包含了超导纳米线结构.在行方向上添加正负交替的偏置电流,电流分配到每一行的各像元上,然后通过列方向输出线接到地端.列和行上的放大器被用来读取光子检测事件.在没有光子吸收的时候,整个阵列的行列读出线上均检测不到相应的脉冲,而当某一个像元(如橙色像元)吸收光子后,其超导态被破坏,此时会在它所在的行和列上产生极性相反的两个脉冲,通过对行与列的输出脉冲计数即可确定SNSPD 响应像素的位置.该读出方式结构相对简单,规模易扩展,其主要问题在于像元的不均匀性可能会带来电流的重分配问题,且该方法并不具备光子数分辨能力.(b) 阵列SNSPD 三维结构图.(c) 行列电极示意图.(d) 隔离层结构示意图,通过对行列相交处的小范围区域进行电子束曝光,显影后形成的氧化硅可充分覆盖暴露的行连接线,紧接着在氧化硅上制备顶层金电极,即可在不接触行连接线的同时,从上方跨越式地将底层列电极相连.采用此方法制备的隔离层覆盖面积小,以此可以保证超导薄膜直接在衬底上生长而不需要在氧化层上生长,从而进一步确保纳米线的质量.(e) 纳米线探测区域示意图.(f) 像元内部结构示意图,主要包括蜿蜒纳米线、用于扩展阵列数的15 个并联电阻(浅绿色)以及用于保证电流均匀分配的1 个串联电阻(浅灰色).占空比达44%Fig.1.Device design: (a) Schematic of the row-column multiplexing array.Each rectangle in the figure represents a pixel that contains an SNSPD.Alternating positive and negative bias currents are added in the row direction and distributed to each pixel (in each row),which are connected to the grounding terminal through the output line in the column direction.Amplifiers on rows and columns are used to read photon detection events.In the absence of photon absorption,the whole array output lines have an undetectable corresponding pulse.When a pixel (such as the orange pixel) absorbs photons,its superconducting state will be destroyed,which generates two pulses with opposite polarities in the direction of the row and column.The SNSPD response pixel can be located by counting the row-column output pulse.The structure of the readout is relatively simple,and its scale is easy to expand.The main problem lies in the inhomogeneity of pixels,which may lead to current redistribution.Furthermore,it suffers from a lack of photon number resolution capability.(b) Three-dimensional structure of the SNSPD array.(c) Diagram of the row-column electrode.(d) Diagram of the isolation layer.With electron beam exposure to a small area at the intersection of rows and columns,the silicon oxide formed after development can fully cover the exposed row connection lines.Then,the top gold electrode can be fabricated on silicon oxide,which connects the bottom column electrode from above without touching the row connection lines.In our methods,the fabricated isolation layer occupies a small coverage area,which ensures that the superconducting film grows directly on the substrate rather than on the oxide layer to further ensure the quality of the nanowire.(e) Diagram of the nanowire detection area.(f) Diagram of the internal structure of pixels,which includes sinuous nanowires,15 parallel resistors for expanding the number of arrays,and 1 series resistor ensuring an even current distribution.Fill factor: 44%.

在行列复用的读出结构中,各像元内的蜿蜒纳米线将起始于所在列电极,终止于所在行连接线,为避免器件短路,在行连接线和列电极的相交处,需要由特殊的结构来构建电学隔离(如图1(a)).在已报道的工作中[24],采用了在整个底层结构上方大面积生长厚氧化硅层,再对其穿孔的方式实现行、列电极的隔离,但此三维工艺复杂度高,基于此,提出了一种二维的隔离层工艺,如图1(d)所示.利用了电子束抗蚀剂氢倍半硅氧烷(hydrogen silsesquioxane polymer,HSQ)在经过电子束曝光(electron beam lithography,EBL)后会生成氧化硅电学隔离层的特性[26],这种平面工艺仅需在小范围内进行微结构的堆砌即可实现相同的隔离功能,从而大大地降低制备难度,提高了工艺稳定性.

此外,由于纳米线覆盖范围较大(见图1(e)红色部分),且EBL 过程中存在邻近效应,为保证整个器件上不同区域的线条粗细均匀,在纳米线周围添加了一圈图形校正区域(见图1(e)棕色部分),用于补偿外圈像元的欠曝光剂量.32×32 阵列SNSPD 的像元内部结构比传统的单像元或小阵列SNSPD 更为复杂.像元尺寸为50 µm×50 µm,有源面积约38 µm×38 µm.除了红色的蜿蜒纳米线结构,还在每个像元的纳米线末端添加了串联电阻(见图1(f)浅灰部分),通过工艺优化来控制电阻的阻值稳定,从而使行方向上施加的偏置电流在低温状态下能够尽可能均匀地分配给各像元.可以看见,像元内还设计了15 个并联电阻(见图1(f)浅绿部分),一方面,可将每个单像元进一步扩展为15 像元阵列(约4×4,其中右下角串联电阻占据一个子像元的位置),即器件可以扩展为128 像元×128 像元的阵列SNSPD.另一方面,此结构还为实现光子数分辨提供了可能.

2.2 可行性验证

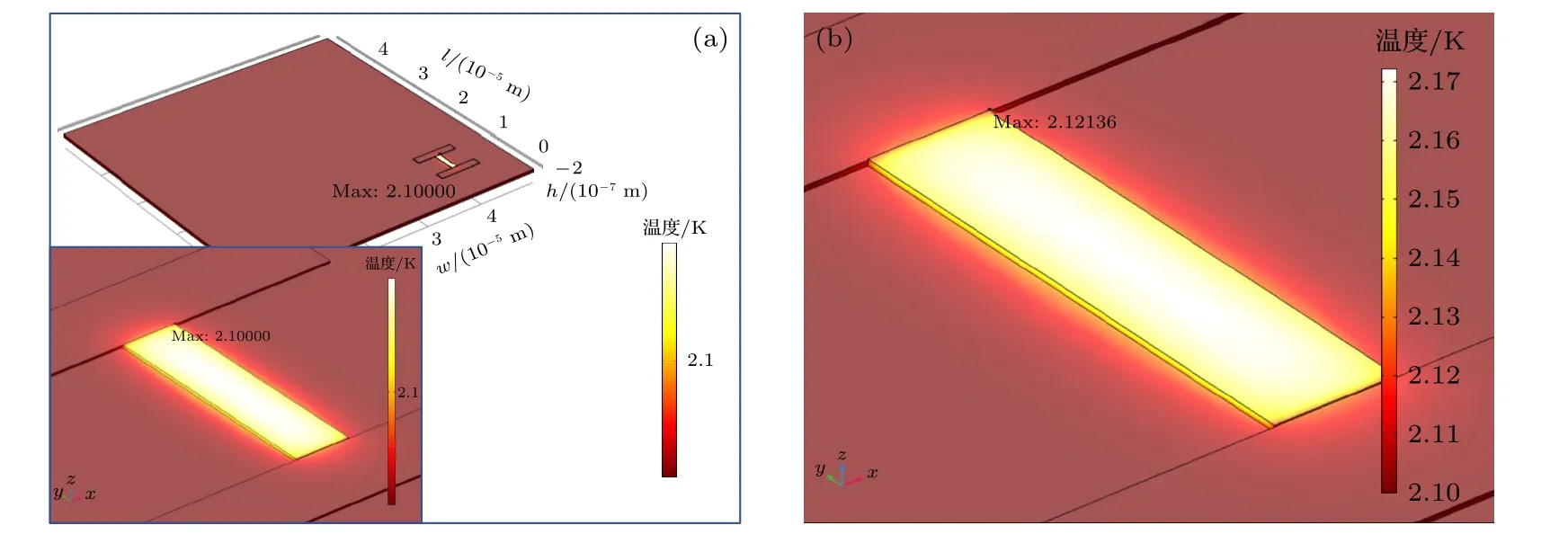

在像元中加入了串联电阻以保证电流在低温下能够进行均匀分配,但如果该电阻在低温下产生的焦耳热会影响纳米线状态,如导致线条失超、闩锁等,那么这个结构的设计就是不合理的.首先对串联电阻进行了焦耳热仿真,模拟了钛电阻在2.1 K 环境下、施加15 µA 典型偏置电流后的工作状态,可以看到,其周围温度也在2.1 K 附近(如图2(a)),不会造成明显升温;进一步将端口电流增加100 倍,钛电阻发热范围内最高温仅为2.2 K 左右,如图2(b).因此获得初步结论: 该版图中的串联电阻所产生的焦耳热不会影响纳米线工作.

图2 串联电阻可行性验证 (a) 典型偏置电流仿真结果;(b) 100 倍偏置电流仿真结果.仿真中采用的参考材料分别为Si 衬底、100 nm 电阻Au 支架、40 nm Ti 电阻.仿真设置环境是2.1 K,理论上更高工作温度下电阻焦耳热不会对纳米线功能造成影响Fig.2.Feasibility verification of series resistors: (a) Simulation results of typical bias current;(b) simulation results of 100 times bias current.The reference materials used in the simulation are a Si substrate,100 nm resistor Au bracket,and 40 nm Ti resistor.The simulation was conducted at 2.1 K.Theoretically,joule heat in the resistors will not affect the function of the nanowire at higher working temperatures.

2.3 制备工艺的设计与优化

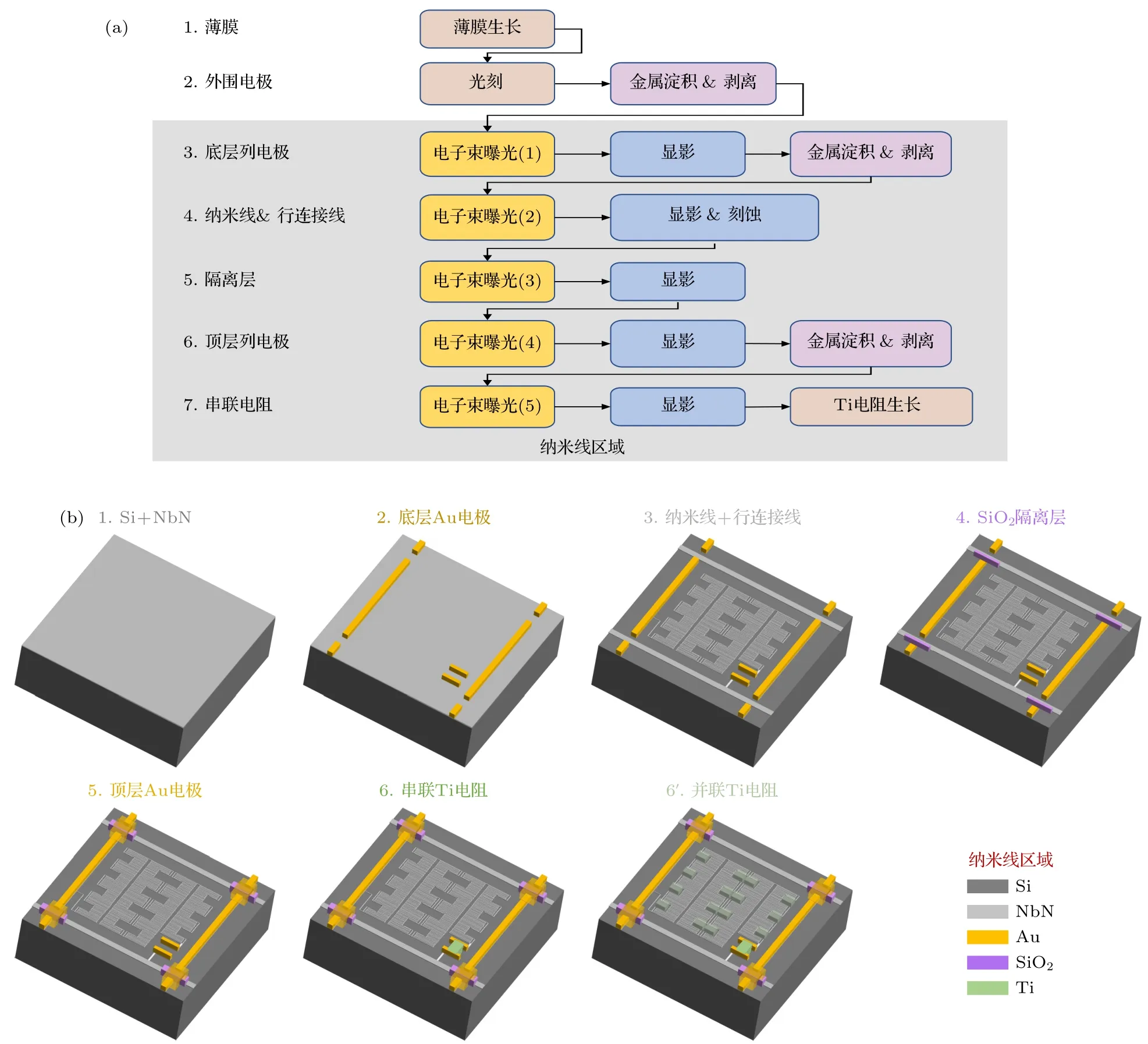

该阵列器件的整体制备流程如图3(a)所示,其中七个阶段分别对应了七大关键结构的制备.

图3 工艺流程设计 (a) 工艺流程图;(b) 纳米线区域工艺流程的三维示意图,与图3(a)中步骤3—7 可关联,且各结构并未按比例绘制Fig.3.Design of fabrication process: (a) Flow chart of fabrication;(b) a three-dimensional diagram of the fabrication process of nanowire area,which is associated with steps 3 to 7 in Fig.3(a).The structures are not drawn to scale.

首先在2 寸 (1 in=2.54 cm)的硅片上使用直流(DC)磁控溅射(型号DE500)的方法生长6—8 nm 的NbN 薄膜,薄膜方阻在68—75 Ω,Tc可达7.5 K.接着使用紫外光刻(ABM)转移外围电极图案,光刻胶为AZ1500,在4000 r/min 转速下胶厚约2 µm;然后使用磁控溅射生长厚度为120 nm 的金电极,为了增加金电极与NbN 薄膜的黏附性,在金与NbN 之间生长了10 nm 的Ti 层,通过lift-off 工艺来得到外围金电极.由于纳米线区域内部的结构尺寸较小(最小尺度约2 µm),普通光刻无法充分满足其精度要求,且不同微结构之间需要进行非常精密的对准,因此引入电子束曝光技术(型号EBPG5200 Raith)来完成接下来制备.通过旋涂AR-P 6200.13 电子束抗蚀剂,在4000 r/min转速下胶厚约300 nm,进行第一次EBL 后生成底层电极图案,使用与上述相同的长金方法生长5 nm 的Ti 黏附层与40 nm 的Au 层,剥离后得到底层金(列)电极.值得一提的是,这里的Au 层厚度是经过反复实验优化才确定的,采用薄金属层是为了避免底层电极对后续工艺造成影响,若其结构太厚,将导致抗蚀剂在电极周围堆积或胶厚不均、电子束曝光时金属导电改变电子分布、以及加大顶层电极的连接难度等,且此时的列电极并非连续的,而是以像元为周期的一条条线段,线段纵向的间隔是为行连接线预留的空间.下一阶段,在样品旋涂上浓度为2%的电子束曝光胶HSQ,在4000 r/min 转速下旋转1 min 控制胶厚在50 nm左右,使用100 keV 的加速电压和1 nA 束流进行第2 次电子束曝光,实际过程中需要约2 h 可完成千像元阵列的纳米线以及行连接线的书写.显影后,使 用SF6与CF3以40 sccm∶20 sccm (1 sccm =1 mL/min)为流速比例混合的气体、4 Pa 的气压和80 W 的功率进行反应离子刻蚀(RIE-10,SAMCO)36 s,获取纳米线和行连接线,同时,由于底层金(列)电极也可视为刻蚀掩膜,因此刻蚀结束后也将形成对应的NbN 列电极.根据2.1 节所述,需要先行制备隔离层,而后将分段的底层列电极相连.在样品上重新旋涂一层HSQ,经过第3 次电子束曝光和显影之后,在行列电极的重叠区域生成局部氧化硅电学隔离层.此时,以AR-P 6200.13 为抗蚀剂进行第4 次电子束曝光,成功转移图案后生长10 nm 的Ti 黏附层以及120 nm 的Au 层作为顶层电极,跨越下方被保护的行连接线,完成分段列电极的连接.最后,同样是以AR-P 6200.13 为抗蚀剂,第5 次电子束曝光将进行电阻区域的书写,显影后根据需要生长一定厚度的Ti 层(300 nm),通过剥离工艺得到我们的电阻.至此,整个器件的结构已制备完毕.

在图3(b)中以三维图的形式细化展示了纳米线区域内各结构的制备过程,为了更形象地展示我们平面工艺的“堆砌”特点,图中的结构厚度并没有严格按照实际比例绘制.

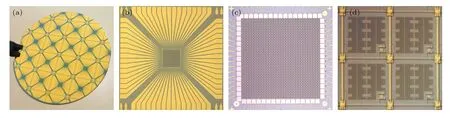

针对器件中的不同结构,各步工艺的侧重点有所不同,对于超导薄膜,需要预先进行厚度、生长条件、刻蚀条件的优化;对于外围电极,需要确保其对称性以及与精细结构连接的稳定性;对于内部精细电极,需要重点关注其厚度及剥离效果;针对串并联电阻,需要根据后期的低温测试结果来反向指导阻值的确定;针对纳米线区域,则离不开更细致的工艺优化,这点将在2.3 节中具体阐述.经过多次实验摸索,最终我们呈现出了以上工艺参数.总的来说,通过灵活设置各工艺步骤和顺序,有效地避免了电极与纳米线之间的相互影响,缩短了传统制备方法的工艺周期,实现了器件设计中多图层、高精度的焦平面结构的制备.图4 则展示了最终制得的阵列SNSPD 的光学显微图像.从图4 可以看见,在制备过程中对此大型密集面阵的样品洁净度控制良好,视野中也没有明显坏元,实验证明,这套工艺方案也具备相当的可重复性.

图4 阵列器件光学图片 (a) 样品实物图;(b) 器件预览;(c) 纳米线区域光学显微镜图像;(d) 像元内部结构光学显微镜图像Fig.4.Optical image of device: (a) The sample chips on wafer;(b) device preview;(c) optical microscope image of nanowire area;(d) optical microscope image for internal structure of pixels.

2.4 纳米线优化

保证纳米线的均匀性是制备过程中的关键挑战,因为常见SNSPD 的感光区域尺寸多为几十微米,而我们研究的阵列SNSPD 的核心纳米线区域尺寸达到了毫米量级,电子邻近效应在大面积曝光时将尤为突出.相比起中心纳米线,靠近边缘的纳米线会因缺乏周围像元的剂量补充而欠曝,在使用负胶(HSQ)的情况下,其线宽将会不足.因此合适的曝光剂量对纳米线的质量而言至关重要.如图1(e)所示,纳米线区域需要进行电子束曝光的部分包含3 个区域,分别是纳米线本体、图形校正区域和行连接线,三个区域分属于不同图层,通过分别调整这3 个图层的曝光剂量,即采用分布式电子束曝光技术,可以更灵活地进行综合调控,经过多次实验探寻最优剂量,以获得大面积范围内最均匀的纳米线条.

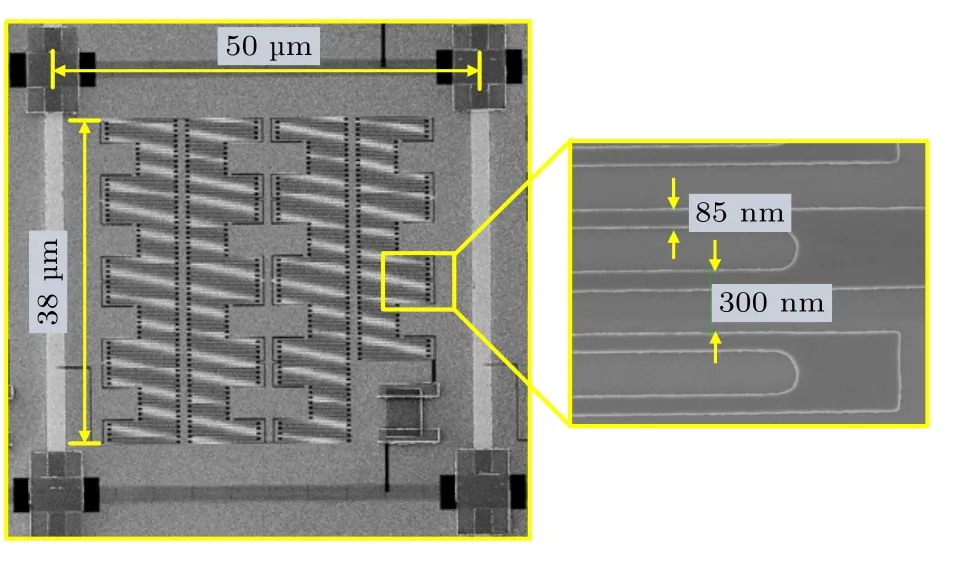

使用优化后的剂量进行器件制备,所得纳米线如图5(a)所示,线宽为(87±3) nm,均匀性良好,像元内各结构完整且形态正常,为实现器件更好的探测性能奠定了基础.

图5 一个像元的超导纳米线扫描电子显微镜图Fig.5.Scanning electron microscope image of a superconducting nanowire for a pixel in the fabrication device.

3 结果与讨论

保证毫米级大面积器件的均匀性,是阵列SNSPD 制备工艺的关键难点.至此,需要对其制备结果进行相关的测试表征.

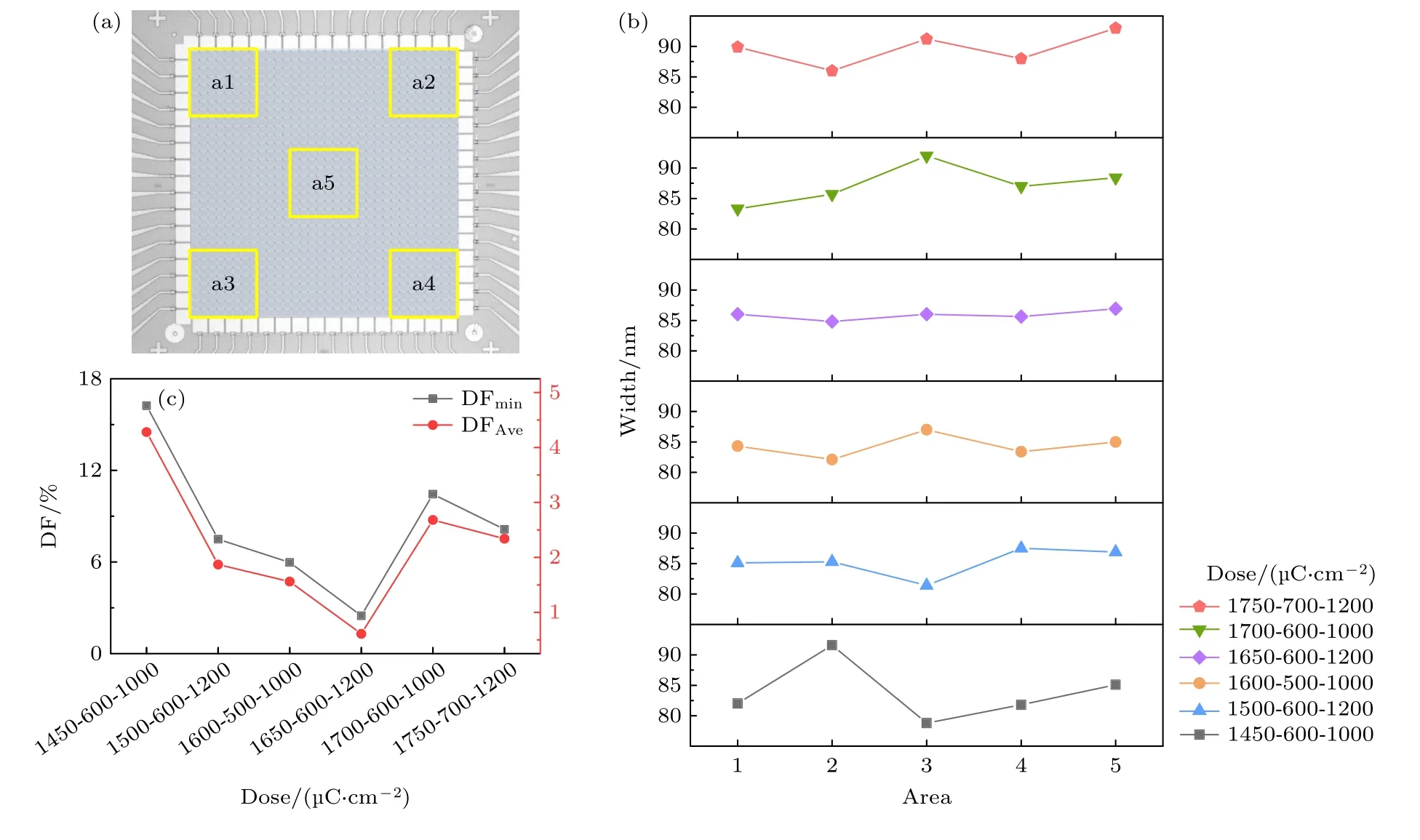

3.1 纳米线均匀性测试

为了衡量剂量优化后的分布式曝光效果,将阵列器件的感光部分划分为4 个边角加中心共5 个区域,从5 个区域的范围内各随机选取1 个像元来进行纳米线线宽标定,采集示意图如图6(a)所示.从扫描电子显微镜观测并记录的某次实验数据(图6(b))可以看出,不同曝光剂量会影响到同器件内不同区域的线宽分布,此处图例中的三个数据分别表示纳米线-图形校正-连接线区域的剂量.在1450-600-1000 µC/cm2的条件下,由于中心纳米线部分剂量严重不足、而图形校正部分剂量相对过剩,主剂量与补充剂量失配程度大,该器件5 个区域内的线宽在78.8—92.6 nm 较大范围内均有分布,且波动明显;与此对应的,在1600-500-1000µC/cm2的条件下,增加了核心纳米线部分的剂量,不同区域间的线宽均匀性有所提高,然而由于外围图形校正及行连接线部分的剂量仍处于偏低水平,无法为边缘像元的纳米线提供足够的欠曝补偿,则此时呈现出器件角落像元的线宽普遍偏小的情况;基于此,适当增大后二者的剂量,在1650-600-1200µC/cm2的条件下,5 个区域的纳米线线宽集中分布在84.8—86.9 nm 范围内,波动极小,此时纳米线剂量达到最佳范围,且与图形校正及连接线部分的剂量相匹配;进一步地,若继续增大纳米线剂量,器件线宽整体呈现上升趋势,不同区域间的线宽均匀程度显著下降,如在1750-700-1200 µC/cm2条件下,器件中心区域(a5)的纳米线线宽将明显大于四周区域,且由于剂量过剩,过曝光将导致器件整体线条边缘粗糙,纳米线规整度降低.

图6 纳米线区域剂量优化 (a) 单器件内标定纳米线线宽的采样点示意图;(b) 不同剂量下线宽的区域分布情况,其中图例显示的是纳米线-图形校正区域-行连接线的剂量;(c) 各剂量下同器件线宽偏差因子,灰线表示极差,红线表示相对平均偏差.以上为某次实验的6 个剂量组合条件下获得的线宽数据,已将剂量不合适的情况排除(剂量过小时纳米线易移位、断裂;剂量过大时线条边缘粗糙、易粘连).实验过程中每批次将同时曝光16 个器件,曝光阶段纳米线、图形校正区域及行连接线三种结构均采用一定范围的剂量分布,在研究阶段,此方法可保证每次实验都有数个器件的剂量合适,能有效减小仪器不稳定性造成的影响Fig.6.Dose optimization in the nanowire area: (a) Diagram of sampling points for calibrating nanowires in a single device.(b) Distribution of line width at different doses.The legend represents the dose of the nanowire-graphic correction area-row connection line.(c) Line width deviation factor of the same device at each dose.The gray line indicates the range,and the red line indicates the relative mean deviation.The above are line width data obtained under the conditions of six dose combinations (in one experiment),and the case of an inappropriate dose has been excluded (the nanowire is easy to shift and break when the dose is too small,while the line edge is rough and easy to stick when the dose is too large).Sixteen devices are exposed in each batch at the same time,and an appropriate dose distribution is adopted for nanowires,graph correction areas and row connection lines.In the research stage,this method ensures that there are several devices that enjoy the appropriate dose in each experiment and effectively reduces the negative influence caused by instrument instability.

上述结果表明,进行曝光的过程中,三个部分的剂量条件存在交叉影响,因此对三种结构均采用一定范围的剂量分布是非常有必要的.本次实验中,当纳米线-图形校正-连接线的剂量分别采用1650-600-1200 µC/cm2时,5 个区的纳米线线宽表现最为一致,即均匀性最佳.图6(c)显示了器件在不同曝光剂量下得到的纳米线宽度的偏差程度,偏差因子可由以下公式计算定义[27]:

其中Wmax,Wmin和分别为器件的最大线宽、最小线宽和线宽均值; DFmin表示某剂量下最大线宽与最小线宽的百分比差; DFAve则表示5 个区域线宽的相对平均偏差,进一步刻画了其离散程度.由图6(c)可见在上述1650-600-1000 µC/cm2的剂量条件下,两个偏差因子均可控制在3%以内.

3.2 器件电学性能测量

在完成器件制备以及初步检验了纳米线的均匀性之后,需要对器件的网络结构进行分析,搭建一套合适的系统以进一步获得器件的基础技术指标,从而进行均匀性和良率的表征.

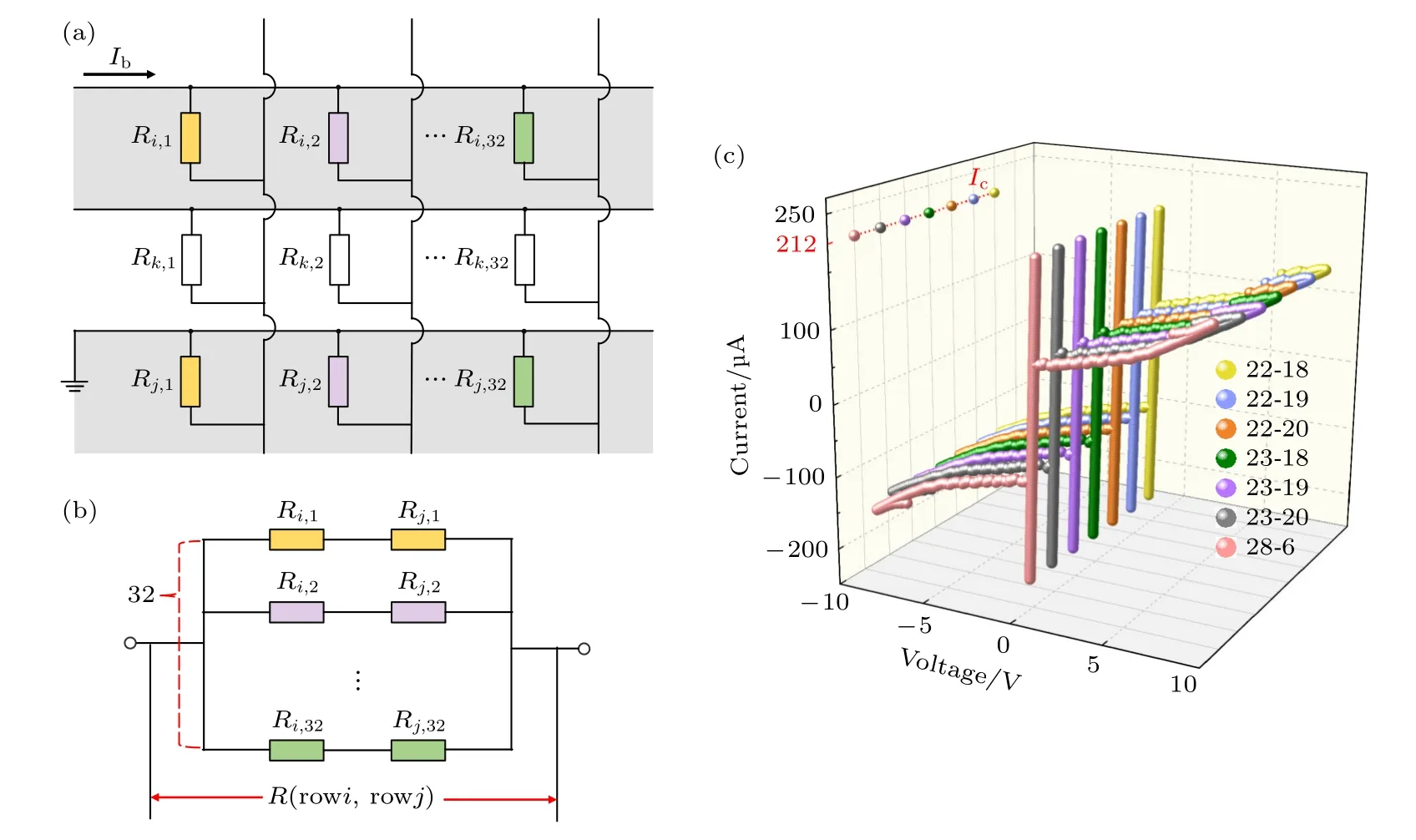

为了提高效率,在接入32×32 阵列SNSPD 专用封装和光电平台之前,将优先在液氦下初步测量其I-V特性.由于阵列数目较多,像元之间的连接形成了一个庞大的电阻网络,为了能够对像元整体与局部有一个统一的标定,对该电阻网络进行了模型简化.本文所采用的行列复用结构的示意图已经在图1(a)中给出,现有多种测量连接方式可供选择.第1 种方法是在测量某个像元阻值时将该像元的对应行与对应列分别接电源端与接地,即行-列连接法,该法的等效电路过于复杂,难以对测量结果进行有效的分析,少数情况下若被测像元短路,则测得阻值显然为零,而若被测像元开路,该法的测量结果与正常情况的差异不明显.第2 种方法是将被测像元的对应列与电源端直接连接,并将阵列的所有行都接地,这也是一种行列连接方式,该法使得接入网络的单元数减半,则单像元的波动对整个测量结果的影响将加倍,即使用该方法进行测量更容易发现像元的电阻异常情况,但随着接地的端口数激增,由点焊等操作带来的测量时间成本也将大幅增加,此法可用于后期将器件置于制冷机中进行高精度测量.第3 种方法抛开了行列连接的固定思维,将某两行(或者某两列)分别接偏置电流和地,如图7(a)所示,与前述方法相比,这种行-行(列-列)连接的方式可等效为非常直观的并联电路,见图7(b),由于各像元在器件设计和工艺制备上都使用了相同参数,所以理论上连接不同的行或列获得的电学参数应该相当,外电路测得的常温电阻理论上是单像元电阻的0.0625 倍.该法的测量难度小,且对个别像元的异常具备一定的敏感度,比如若某个像元与正常像元性能差距过大,那么该像元在其对应行与对应列被连接包含时的测量结果将会有波动,由此可以对问题像元进行定位,并通过多组结果的统计分析,来评判器件整体的均匀性.综上,第3 种方法可兼备测量结果的易分析性以及实验准备时间合理,是我们对工艺进行反馈式检验的阶段首选的测试方法.

采用探针台以上述“行-行”的连接方式对制得的阵列器件进行了阻值测量,其常温电阻分布均匀且基本与理论值相符,从侧面反映了器件的制备质量较高.进一步地,将经过了电阻初筛后的阵列器件置于低温下测试其超流特性(I-V曲线),以初步检验像元能否正常工作.同样采取第三种行-行连接的方式,将打线后的探测器芯片置于液氦中(工作温度约4.2 K)进行了一系列并联测试,均未发现坏点.此处分别展示了一端固定第22 行、另一端依次连接18,19,20 行;一端固定第23 行、另一端依次连接18,19,20 行;以及两端接入第28 行和第6 行的I-V曲线,如图7(c)所示.从图7(c)可以看出,多种行连接组合所得到的I-V特性曲线大致相同,其整体形状趋势和超导临界电流都十分接近,此即像元一致性较高的又一佐证.

图7 阵列器件均匀性测量,其中i 表示行号,j 表示列号 (a) 简化的阵列行-行(列-列)连接示意图;(b) 简化的阵列行-行(列-列)连接等效电路图;(c) I-V 特性曲线均匀性测量结果,其中Ic 为超导临界电流,T=4.2 KFig.7.Homogeneity measurement for array devices: (a) Simplified schematic of array row-row (column-column) connections;(b) simplified equivalent circuit diagram for array row-row (column-column) connections;(c) homogeneity measurement results (I-V curves),where Ic represents the superconductor critical current.T=2.4 K.

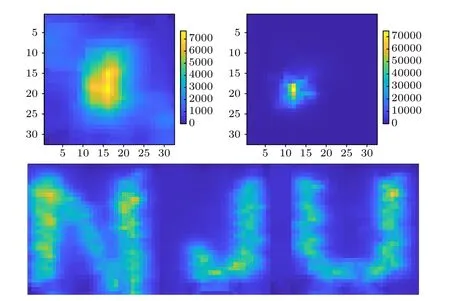

3.3 器件成像功能验证

在上述结果基础上,优化设计和工艺,挑选出的器件用于光子探测与成像测试,初步验证了阵列器件的成像性能.系统的电路部分由32 通道偏置电路、64 通道放大电路、64 通道时间数字转换器(time to digital converter,TDC)构成,基于行和列的时间戳符合计数(TDC 记录的行信号和列信号的到达时间差值小于8 ns 则视为该行列处像素产生响应)实现各像元信号的读出.采用自行搭建的共聚焦成像系统,对可见光光斑经过制冷机窗口和衰减片后照射到器件.图8 给出了小光斑和大光斑成像效果,以及对书写的“NJU”图像效果图.图中的纵坐标和横坐标分别表示行和列编号,右侧颜色条表示每一帧积分时间100 ms 时各像元的光子计数值.

图8 阵列器件被用于光子探测,实现对不同大小光斑的成像,以及书写的“NJU”图像效果(图中的纵坐标和横坐标分别表示行和列编号,右侧颜色条表示每一帧积分时间100 ms 时各像元的光子计数值)Fig.8.Devices are used for photon detection to achieve imaging of light spots of different sizes,as well as the written “NJU” image.The vertical and horizontal coordinates in the figure represent row and column numbers respectively,and the color bar on the right represents the photon counting value of each pixel at the integration time per frame of 100 ms.The vertical and horizontal coordinates in the figure represent row and column numbers respectively,and the color bar on the right represents the photon counting value of each pixel at the integration time per frame of 100 ms.

4 结论

综上所述,采用了一种简化的平面隔离层工艺,成功制备了一种基于行列复用结构的32×32阵列SNSPD,其复杂度与国际上已报道的用于实现相似结构的三维工艺相比大大降低.该阵列有效探测区域达1.6 mm×1.6 mm,像元内纳米线占空比达44%,且理论上可通过增加像元大小或使用微透镜阵列来进一步增加填充率.本设计使器件在低温状态下采用全超导电极传导,各像元内的串联电阻有利于偏置电流的均匀分配,同时可通过添加并联电阻,将器件进一步扩展为128 像元×128 像元的阵列.通过工艺流程的设计和一系列实验的反复优化,确定了合适的工艺参数,包括纳米线区域内多结构的电子束曝光剂量,整体工艺稳定性高、可重复性高.进一步,对其进行了纳米线均匀性的标定以及超流特性的测量,线宽偏差因子可控制在3%以内,器件在行并联检测下无坏点,与目前已报道的工作相比成品率高.整体实验结果表明,我们所研制的阵列SNSPD 在器件层面能够充分保证大面积范围内的像元均匀性,具备成像功能,证明了该简化工艺的可行性,有望使用于百万像元阵列SNSPD 的制备.后续将在此器件基础上引入低温读出电路,并结合压缩感知等技术,以实现准确、快速、高效的大面积阵列SNSPD 成像系统,满足极端环境下大视场、高灵敏、高分辨率的探测需求.