射频集成电路校准技术综述

2022-11-29李松亭

李松亭 颜 盾

①(国防科技大学空天科学学院 长沙 410073)

②(湖南大学信息科学与工程学院 长沙 410082)

1 引言

随着产品需求逐渐向小型化、低功耗化过渡,尤其是5G大容量通信[1]、雷达探测中高穿透力高分辨率需求[2]使射频通信频段逐步向毫米波段过渡,射频集成电路的制造工艺在需求牵引下逐渐由深亚微米级向纳米级过渡,集成电路中元器件之间的失配、工艺偏差、非理想器件特性等都有明显增大的趋势,加之元器件射频模型的不准确性以及封装等寄生效应的影响,造成射频集成电路产品成品率过低、产品开发时间过长等问题,给射频集成电路产品的设计带来了严峻的挑战。以互补金属氧化物半导体 (Complementary Metal Oxide Semiconductor, CMOS)工艺偏差带来的电阻值随机波动为例,采用归一化蒙特卡洛仿真,130 nm工艺电阻值的随机偏差位于3σ内(σ为标准高斯分布的方差),如果将工艺下降到55 nm,随机偏差可达到5σ。这势必会导致所设计射频集成电路性能的降级,甚至无法满足具体的应用场景需求。上述影响属于静态非理想因素,属于射频集成电路的一种固有属性,当一款射频集成电路封装完成后,这种属性会导致射频集成电路性能的固定比例降级。另外,射频集成电路的工作过程是一个典型的热变过程,温度的改变会动态地改变无源器件的阻抗值以及有源器件的迁移率、介电常数、跨导值等,造成电路性能降级。另外,链路增益以及输入/输出信号频率的改变也会对电路性能产生动态影响。这些影响属于动态非理想因素,属于射频集成电路的一种随机属性,其会动态地改变射频集成电路的性能,造成一定程度的性能降级,甚至影响正常使用。

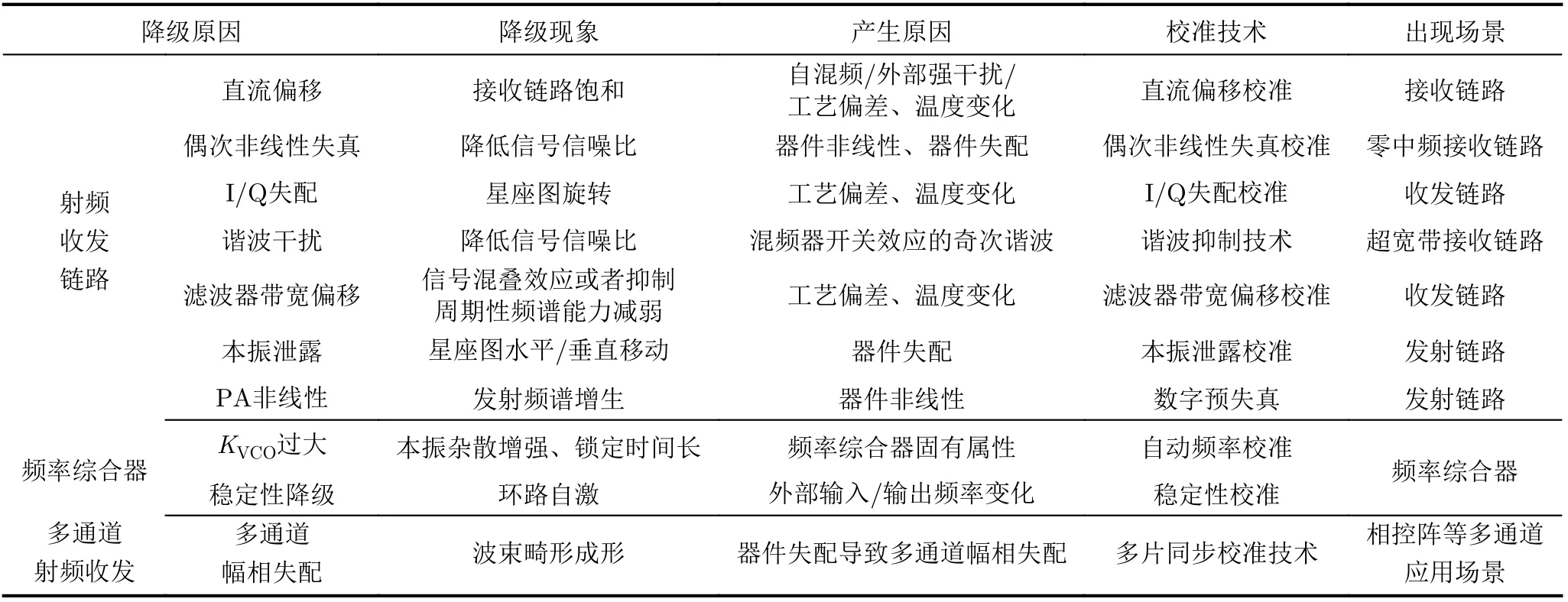

本文主要针对射频集成电路的性能降级机理进行分析,归纳总结能够提升射频集成电路鲁棒性的各类校准技术,为高性能射频集成电路的设计提供坚实的基础理论支撑。具体内容如表1所示。

表1 本文校准技术总结

2 射频收发链路校准技术

2.1 直流偏移校准

直流偏移对于射频接收机的设计是一个极为严峻的挑战,直流偏移的产生主要来自3个方面:(1)混频器本身的自混频效应;(2)外部的强干扰在混频器端产生的自混频效应;(3)工艺偏差、温度变化导致的直流偏移。当基带电路增益较大时,直流偏移极易导致射频接收链路的饱和。

直流偏移校准(DC Offset Calibration, DCOC)通常的做法是在电路中加入交流耦合电容,但是该方法并不适用于零中频架构以及中频频率较低时的低中频架构。另一种方法是采用无源低通反馈环路[3]或者有源积分[4]反馈环路。反馈式DCOC电路的实时性可以保证静态和动态非理想因素导致的直流偏移均被有效补偿,但是当基带电路提供的增益较高时,反馈环路中的电容值必须足够大以确保获得较低的高通截至频率,很难在芯片内部实现集成,通常采用多级反馈[4]的形式来大幅降低反馈电容的大小。由于高通截至频率的存在,上述DCOC方法并不适用于零中频接收机,否则会导致信号低频成分的损失,通过降低高通截至频率可以缓解部分损失,但是反馈电容的面积会大大增加。

适用于零中频接收机的DCOC电路[4–7]如图1所示,该电路包括静态校准和动态校准两部分,在内部状态机的控制下,静态校准部分依次闭合开关S1~Sn对各电路模块进行直流偏移校准,静态校准模块中的积分清零器每M1个时钟周期清0一次,N的值通常取0,比较结果反馈至二进制搜索算法模块通过数模转换器(Digital to Analog Converter,DAC)以补偿电流或者电压的形式对增益模块的直流偏移进行校准。静态校准模块中的比较器1采用自校准比较器避免其自身的直流偏移对校准结果产生影响[5]。基带链路的DCOC效果与链路的增益大小密切相关,为了保证自动增益控制工作模式下的DCOC效果,通常在芯片上电后会遍历基带链路的增益值并遍历上述DCOC过程,校准结果预先存储于查找表中,通过增益值直接查询补偿[4]。为了解决由于带外强干扰引入的动态直流偏移,可以在静态DCOC过程结束后闭合开关Sd打开动态DCOC环路[8],动态DCOC环路在数字域进行实现避免模拟域采用的大电容,乘法器的目的主要用于调节高通截止频率角,增益G的值越小,高通截止频率角也就越小,但是直流偏移压制效果也会越差,需要折中考虑。

图1 适用于零中频接收机的数字辅助DCOC

2.2 偶次非线性失真校准

奇次非线性失真对射频电路中的各种失配不敏感,通常可以通过提升电路模块本身的线性性能进行改善,但是偶次非线性失真对电路中的各种失配因素非常敏感,必须借助一定的校准手段进行提升。偶次非线性失真会导致接收机的输入2阶交调截取点(Input Second-order Intercept Point,IIP2)性能严重降级,此现象主要是由下变频混频器中存在的各种非线性及失配因素引起的[9]:输入跨导管的偶阶非线性、开关管/负载电阻的失配以及本振信号的非均匀占空比。文献[9]从电路设计的角度给出了针对性的解决方案,在跨导管源端加入尾电流源与电容并联结构,在保证跨导级正常工作的同时降低低频时的等效跨导。另外,通过在开关管的源端加入与寄生电容在本振频率处谐振的并联电感减小周期性阶梯信号的产生。优化后的IIP2可以达到+78 dBm。

考虑到工艺、电压以及温度(Process, Voltage and Temperature, PVT)的影响,偶阶非线性失真通常不能仅通过优化电路设计来满足系统设计需求,同样需要校准电路的辅助进行失真补偿。最小均方(Least Mean Squares, LMS)自适应校准算法是一种典型的用于补偿偶次非线性失真的自适应校准算法[10,11],如图2所示,其中d(n)为实际输入信号(输入有效信号和白噪声的叠加),e(n)为经过偶次非线性失真补偿后的实际输出信号,w(n)为用于校准补偿的1阶抽头系数,ref(n)是与偶次非线性失真严格相关的参考信号,文献[10]通过提取混频器输出端的共模信号成分并经低通滤波后作为ref(n)信号,文献[11]通过在基带算法中产生相应的基带信号,通过发射与接收闭环的形式对偶次非线性失真性能进行补偿校准,ref(n)信号选取为基带信号的幅值。LMS算法生成的1阶补偿系数w(n)通过调整混频器开关管的体电压[12]、栅电压[13,14]、混频器中注入直流偏移电流的大小[15],或者改变用于补偿功能的偶次失真量的大小[16]对偶次非线性失真成分进行补偿,校准后的IIP2可高达+90 dBm[14]。

图2 基于LMS算法的自适应偶次非线性失真校准电路

2.3 I/Q失配校准

I/Q失配主要是指收发链路中I/Q两路的幅相失配以及正交本振(Local Oscillator, LO)信号的相位失配,在零中频接收机中,I/Q失配导致的镜像频谱增生会使星座图产生旋转,对诸如多进制正交幅度调制(Multiple Quadrature Amplitude Modulation, MQAM)等高阶调制系统产生严重的影响,对于正交频分复用(Orthogonal Frequency Division Multiple, OFDM)多载波调制系统,镜像信号的存在会干扰其子载波成分,恶化信噪比。对于高阶调制系统,要求的镜像抑制能力通常需要超过60 dB,幅相失配必须控制在10 mdB和0.1o以内[17]。在低中频接收机中,I/Q失配会导致复数域镜像抑制滤波器的镜像抑制能力降低,无干扰情况下,低中频接收机的镜像抑制能力必须超过16 dB才能保证对信噪比的影响小于0.1 dB[18],在存在干扰的情况下,需要的镜像抑制能力会明显增加。对于零中频发射机,I/Q失配同样会在有效频带内引入镜像干扰降低有效信号的信噪比,对于低中频发射机,I/Q失配会导致天线输出端产生明显的镜像干扰信号,污染临近信道,同时还会降低针对功率放大器线性化的数字预失真精度[19]。

低中频接收机中的I/Q失配校准模块通常位于下变频混频器和复数域镜像抑制滤波器之间用以提升滤波器的镜像抑制能力,采用数模混合设计的方法,具体的补偿电路结构如图3所示[20,21],其中Imis/Qmis, Ical/Qcal分别表示校准前后的下变频正交信号,ε和φ分别指I/Q通路的幅度和相位误差。该校准电路中幅度误差检测电路和相位误差检测电路输出的均是相应的检测符号,并通过二进制搜索算法调整幅度/相位误差补偿电路的配置,从而补偿正交失配。需要注意的是,幅度/相位误差检测电路检测结果的准确性依赖幅度/相位误差的大小,较大的幅度/相位误差会引入较大的检测结果误差,因此,如果采用二进制搜索算法,则幅度误差校准和相位误差校准必须分时进行,否则会无法完成正常的失配校准。如果使用步进式加减算法则可以同时对幅度失配和相位失配进行校准。输入端的信号可以是一个单音信号[20]亦或采用经低噪放放大后的白噪声[21],幅度/误差补偿电路可以在模拟域构建相应的放大器和加法器进行实现[21]。

图3 适用于低中频接收机的正交失配校准电路

零中频接收机的I/Q失配校准通常在数字基带处理模块中进行补偿[22–25],典型校准电路结构如图4所示[22],其补偿原理与图3相似,只是采用LMS算法逐步将误差补偿电路中补偿参数的最优值估计出来。校准过程中的I/Q支路输入参数只要具有平稳随机特性,均适用于该校准机制。发射链路的I/Q失配需要借助接收机形成回环的方式进行校准,文献[23]采用串行校准的方式,首先采用内置的本振产生的单音信号注入射频接收机中对其I/Q通路进行失配校准,然后发射和接收链路形成回环,在基带中基于直接数字频率综合器(Direct Digital Synthesizer, DDS)提供单音信号,经过回环链路后估计出的I/Q通路失配即为发射链路的I/Q失配参数。发射链路中的失配校准电路除了在基带中实现以外,还可以采用具有双开关结构的上变频混频器在模拟域进行实现[17]。为了进一步加快校准速度,文献[24,25]利用I/Q失配能够引入镜像信号的原理,采用多个不同频率的单音信号[24]或者设置不同的收发本振频率[25]在频域上对收发链路的镜像信号进行区分,可以同时对收发链路进行校准。

图4 I/Q失配基带自适应LMS校准电路

对于宽带通信系统,I/Q误差失配除了与PVT,LO相位失配等因素相关外,还与频率有着明显的关系(滤波器的群时延失配导致I/Q相位失配与频率密切相关),文献[26]通过在回环链路的发射输入端注入两个不同频率的单音信号,通过交叉回环连接的方式,利用线性内插可以同时计算出收发链路群时延失配与频率的关系,通过在I/Q支路中引入具有不同群时延特性的FIR滤波器[26]或者负载电容调谐[27]来补偿I/Q支路的相位失配与频率的关系。文献[28]在文献[26]的基础上通过引入相位旋转模块有效解决了I/Q幅度失配与频率之间的依赖关系。针对温度变化对I/Q失配的影响,文献[29]提出了一种基于迭代技术的在线追踪方案,可有效跟踪温度变化对发射机I/Q失配造成的影响并进行动态补偿。

2.4 谐波抑制技术

谐波抑制技术是软件定义无线电射频接收机中的一个关键指标[30–32],由于混频器LO开关引入的奇次谐波,接收机输入端在无声表面波(Surface Acoustic Wave, SAW)滤波器或者SAW滤波器带外抑制性能较差时,输入端存在的奇次谐波干扰会通过与LO信号的奇次谐波混频干扰有效频带内的信号。

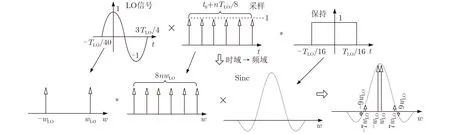

典型的双平衡混频器(Gilbert架构)等效于对LO信号进行2倍频采样保持,正交双平衡结构等效于对LO信号进行4倍频采样保持,此两种结构中的本振信号均会提供3/5/7···等奇次谐波,幅度与保持功能对应的频域辛克(Sinc)函数直接相关,无法满足谐波抑制功能。谐波抑制的典型电路结构是采用多相(>4)混频结构[33],以8相为例[34],相应的LO开关频谱如图5所示,8倍频采样可以有效地避免LO信号中3/5次谐波的出现,有效地抑制输入信号中存在的3/5次谐波干扰。为了抑制更高的奇次谐波,还可以采用16相甚至更高的多相采样结构[35]。

图5 八相混频器本振信号频域等效图

为了避免多相电路结构对压控振荡器(Voltage Controlled Oscillator, VCO)的高输出频率要求以及多相支路累加结构带来的复杂度,文献[30]在双平衡无源混频器的基础上提出了一种采样保持型电容负载结合可调本振信号占空比的组合结构,该结构通过改变本振信号的占空比动态调整Sinc函数幅频响应的过零点,可以有效地抑制输入端的各奇次谐波。文献[36]通过对占空比为25%的四相信号引入相同时间宽度的频隙和频带同样也会产生相应的谐波抑制能力。文献[37]采用基于脉宽调制技术提供的本振信号也实现了较好的谐波抑制能力。但是为了实现上述技术,最终的硬件开销以及设计复杂度并不比采用多相结构占据多少优势,在具体设计过程中需要折中考虑。

多相本振信号的相位失配以及接收链路中的延迟及增益失配会明显地限制电路的谐波抑制能力,典型情况下,多相混频结构提供的谐波抑制比在30~35 dB[37],文献[38,39]提出了采用两级谐波抑制结构增强电路鲁棒性的设计方法,配合对多相本振信号的重定时电路,谐波抑制比可以超过70 dB[39]。但是重定时结构通常面临亚稳态的问题,且补偿的相位精度与重定时时钟抖动密切相关。文献[31]提出了基于高精度时间-数字转换器(Time to Digital Converter, TDC)估计多相本振信号相位失配及补偿的具体电路结构进一步改善LO信号的输出相位关系。文献[32]提出了一种数模混合的接收机幅相失配校准方法,在输入端输入相应的谐波信号,基带通过对残留下变频信号的功率进行估计动态调整多相支路中的增益值以达到最优的谐波抑制性能,校准后的3/5次谐波抑制能力分别超过70 dB和50 dB[32]。文献[32]还基于仿真手段对输入谐波频率与失配参数之间建立了1阶对应关系,并在实际测试中验证了模型的准确性。文献[40]在数字域首先对多相支路中的失配参数矩阵进行估计,并提出了一种基于优化后Jacobi叠代方法进行谐波抑制的失配参数补偿方法,补偿后的谐波抑制性能可以超过80 dB,但是该方法需要模拟域提供多相支路输出,是以牺牲硬件设计的复杂度及功耗为代价的。

2.5 滤波器带宽校准

射频接收机中集成的基带或者中频滤波器主要用于避免采样过程中的混叠现象,低中频结构中还需提供镜像抑制能力。发射机中由于单边带架构的原因,通常集成低通滤波器,起到抑制基带信号中周期性频谱的作用。射频收发机中通常集成连续时间滤波器,主要包括有源电阻电容(Resistor and Capacitor, RC)[6,21,41]以及Gm-C[42]两种结构,有源RC结构采用闭环结构,线性度较高,但是需要进行复杂的稳定性设计,Gm-C结构采用开环结构,稳定性较好,但是线性度较差。两者提供的带宽精度分别与时间常数RC以及C/Gm有关,由于PVT的影响,滤波器提供的带宽精度通常有±20%的波动范围[41]。带宽的波动可能会导致有效信号边沿频谱的抑制或者影响采样过程中的抗混叠效果,导致信噪比的恶化。因此设计过程中需要对时间常数进行PVT补偿。

对于有源RC滤波器,典型的补偿算法通常采用基于RC时间常数的开关电容充放电机制对带宽偏差进行校准[6,41–44],但是由于校准自由度的限制,这种带宽校准电路并不适用于软件定义无线电射频收发机的设计中,这是因为在滤波器设计中每增加1个带宽频点,就必然要在每一个电容或者电阻网络中加入一个相应的电容或者电阻元件,导致设计复杂度较高、芯片面积较大。另外,为了适应不同的晶振输入频率需求,文献[45]通过引入一个可变的电阻网络与其进行匹配,但是仅支持8个不同的晶振输入频率,不能满足对宽范围晶振输入频率的需求。文献[6]通过增加滤波器带宽校准自由度,在较低复杂度和较小面积条件下,提出了一种适用于软件定义无线电应用场景的滤波器带宽校准机制,但是其校准过程需要构建RC振荡器以及频率综合器及小数分频器的支持,且校准算法比较复杂,功耗及资源消耗量较高。此外,在文献[6]的基础上,文献[46]通过RC振荡器与标准参考时钟的比较,实现了滤波器带宽的动态校准,避免了温度波动对滤波器带宽的影响。在文献[6,46]的基础上,一种更简洁的宽带滤波器校准方案如图6所示,此时的电阻和电容既可以用来调节滤波器的带宽,同时也可以起到校准带宽精度的作用。该方法需要预先在典型工艺角情况下建立带宽调整控制信号与调节电压Vadj之间的查找表关系,通过改变带宽调整控制信号得到高精度的滤波器带宽配置。针对Gm-C滤波器,文献[42]提出了一种收发回环校准机制,通过DDS模块动态改变发射单音信号的频率,在接收端扫描滤波器的幅频响应曲线预估滤波器的带宽,通过与预设带宽的比较逐步调整Gm的值提升滤波器带宽精度。文献[47]将跨导放大器的Gm值通过反馈结构等效于一个电阻值,并通过构造一个RC振荡器来校准其时间常数。文献[48]通过构造Gm-C积分器,并通过自动锁幅原理与参考电压相比较来校准时间常数的值。

图6 宽带滤波器带宽校准电路

通过人为增加滤波器的带宽避免由于PVT波动造成的带宽压缩抑制有效信号的边缘频带也可以保证电路的正常功能[49],但是为了避免采样混叠或者获得更好的周期频谱抑制比,必须提高ADC/DAC的采样频率,同时更高的带宽设置还需要更高的运算放大器增益带宽积或者更高的Gm,会明显增加电路的整体功耗。

2.6 本振泄露校准

LO泄露同时存在于射频的收发链路中,主要是由I/Q支路中存在的直流偏移、混频器开关管以及驱动管的失配导致的。接收链路中的LO泄露向解调方向会导致直流偏移饱和接收机,向天线方向会导致直接泄露。直流偏移可以通过直流偏移校准有效抑制,向天线方向的直接泄露由于低噪放较高的反向隔离度也可以忽略不计。但是对于对线性性能要求较高的Mixer-first接收机而言[50],为了避免对其他通信系统的干扰,必须对缺少反向隔离导致的天线端LO辐射进行抑制。文献[50]通过将混频器进行DAC化,实现了对LO开关管及驱动管1%的尺寸微调功能,有效抑制了LO的反向辐射大小。

发射机中的LO泄露会导致调制信号星座图的移位(直接上变频)、发射频谱增生(带子载波上变频),对于FDD收发机,严重时会饱和接收链路。发射链路的LO泄露校准通常采用收发回环的校准方式[25,26,51–55],通过泄露幅值检测(图7)[54]、下变频至基带或者直流进行数字域功率检测(频域检测[25,27,53]或者时域检测[52])等方式估计泄露LO信号的大小,并与预设功率值进行比较,产生的反馈信号通过DAC对I/Q两路的失配进行电压或者电流补偿以抑制LO泄露的大小。为了避免功率预估过程引入的电路设计复杂度,文献[51]提出了数字域微分及符号量化的方式并采用二进制搜索算法对I/Q两路的直流失配分别进行补偿,复杂度得到了有效降低,且校准时间仅为16 μs。文献[56,57]采用高精度ADC直接对发射机中的差分支路进行直流偏移检测,根据反馈的差值对相应差分支路进行补偿,避免了收发回环过程带来的较高设计复杂度,但是此类方法对ADC的精度要求较高,且无法校准由于混频器开关管以及驱动管的失配导致的LO泄露。

图7 发射端载波泄露校准电路

2.7 数字预失真

功率放大器(Power Amplifier, PA)的线性化是射频集成电路中一项重要的性能优化工作,由于AM/AM以及AM/PM失真的存在,PA的输出频谱中存在大量的交调失真信号,除了导致严重的频谱增生效应外,还会恶化发射机的发射信号性能,尤其是对于具有较大峰均比的高阶调制。通常采用功率回退的方式增大PA的线性性能,但是会明显降低PA的功率转换效率。为了在较高效率的情况下减小失真的存在,包络跟踪PA[58]、G类(Class-G)PA[59,60]、 异相(Outphasing)PA[61]、多合体(Doherty)PA[62]、Class-G+Doherty混合PA[63]等结构分别被提了出来,但是上述结构仅从PA本身的构造出发,为了保证较高的增益及转换效率,仍无法有效遏制PA线性性能的恶化。数字预失真(Digital Pre-Distortion, DPD)技术通过在PA前级基带电路中加入预失真模块补偿AM/AM以及AM/PM失真来有效提升PA的线性性能,在目前的高性能PA设计中得到了广泛的应用。

本节主要从PA行为模型、DPD学习结构、DPD参数辨识方法以及DPD补偿模块模型4个方面对DPD技术进行总结。

PA的行为模型包含无记忆行为模型[64,65]和有记忆行为模型[66,67]两种,PA的记忆行为表现为电路中电容/电感元件的频率敏感性引入的AM/PM失真,在窄带通信情况下,电容/电感元件的频率敏感性会大大降低,PA的行为模型可近似采用无记忆行为模型等效。常用的无记忆行为模型有Saleh模型[68]、Rapp模型[69]、Ghorbani模型[70]、幂级数模型[71]等。而对于宽带通信系统或者多载波通信系统(4G/5G等),常用的有记忆行为模型为Volterra级数模型[72]、Wiener模型[73]、Hammerstein模型[74]、Wiener-Hammerstein模型[75]、并联Hammerstein模型[73]、并联Wiener模型[76]、神经网络模型[77]等。相较于其他有记忆模型,Volterra级数模型可以方便地将PA的非线性和记忆特性结合在一起,能够精准地对PA进行建模,但是随着非线性阶次及记忆深度的增加,需要计算的参数量也会迅速增加[66],很难直接用于高阶有记忆的DPD的设计中,在大多数设计中通常均采用简化后的基于Volterra级数模型的记忆多项式模型[64–67,78–86]对PA进行近似建模。

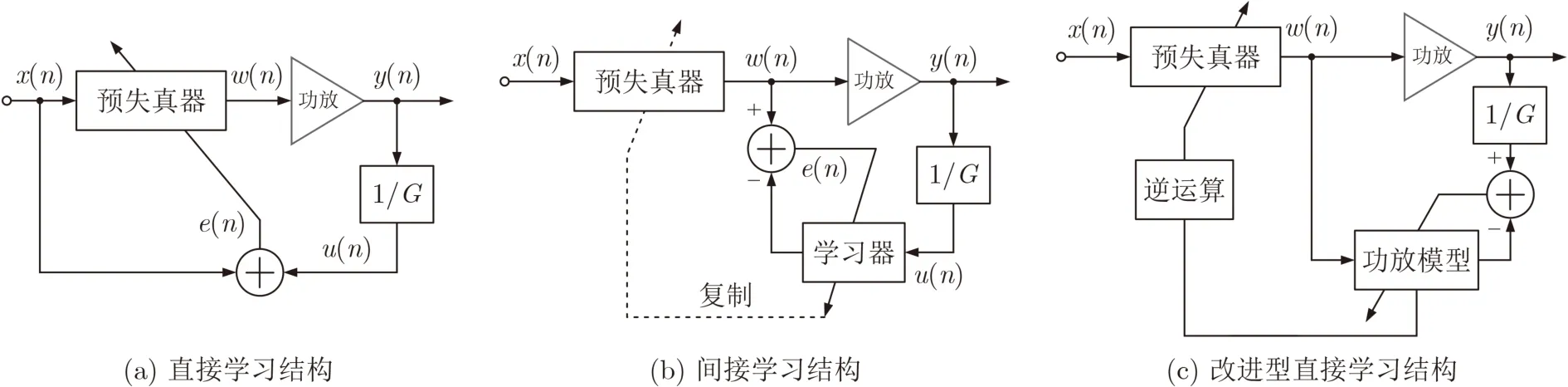

DPD的学习结构包括直接学习结构[83,84,86]、间接学习结构[80,86]、改进型直接学习结构[64]3种,如图8所示,直接学习结构通过求取功放的前逆对PA的非线性进行补偿,但由于预失真器的输出直接影响PA的输出,因此是一个闭环反馈系统,存在稳定性问题。如果采用的DPD参数辨识方法不收敛或者遇到外界干扰,可能导致系统的非正常工作。而间接学习结构通过增加一个学习器求取PA的后逆,再将通过辨识算法计算出的后逆参数送至预失真器来补偿PA的非线性,学习过程开环化,避免了稳定性问题,间接学习结构对于大部分PA均是成立的,目前的商用化数字预失真器中大多采用此类结构,但是对于部分较复杂的PA模型,其后逆与前逆并不一定相等,因此会引入部分补偿误差,同时PA中产生的噪声也会导致学习器的收敛值部分偏离预期[87]。而改进型直接学习结构兼顾直接学习结构和间接学习结构的优点,首先求取PA模型,再通过求逆运算将预失真器等效为PA的前逆,但是求逆计算量往往较大。

典型的DPD参数的辨识方法包括LMS算法[64]和递归最小二乘(Recursive Least Squares, RLS)算法[80,85]两种,由于LMS算法涉及期望值的求解,因此要求输入的信号必须具备广义平稳特性,而RLS算法则无此要求,且RLS收敛速度快,不存在稳态误差,辨识性能更高。但是由于涉及矩阵乘法及向量除法运算,消耗的资源量是非常巨大的,目前工程实现中多数仍采用LMS算法。

DPD补偿模块模型,即图8中的预失真器模型,包括查找表结构和矩阵多项式结构[66,80,85]两种,查找表结构又包括映射查找表[88,89]、复增益查找表[90]以及极坐标查找表结构[91],其中映射查找表的补偿速度最快,且需要的资源量最小,但是其通常适用于无记忆PA模型,无法校准PA的AM/PM失真[89]。根据PA是否采用记忆模型,复增益查找表还可分为无记忆查找表[64,65]和有记忆查找表[70]两类。查找表结构是一种静态DPD机制,通常在上电复位后完成校准并将补偿参数写入查找表。而矩阵多项式结构是一种动态DPD机制,可以根据实时的输入与输出信号动态调整预失真器内的矩阵多项式参数值,跟踪性能优良,但是消耗的计算资源、补偿时长、功耗等均较高。

图8 DPD学习结构

目前对DPD技术的研究主要集中在上述4个方面,近年来多数的创新性成果大多是对具体的电路结构及应用场景进行优化设计,例如,传统的DPD反馈链路需要I/Q两个支路同时存在,且由于PA的非线性效应,反馈支路ADC的采样率需要达到输入信号带宽的5倍以上才能准确预估PA的前逆或者后逆模型[78],需要的硬件开销及功耗均较大,文献[79,80]分别提出了基于单支路硬件架构[79]以及欠采样条件下[80]的DPD补偿电路模型,大大简化了电路设计的复杂度。同时,相控阵[81,82]以及多载波应用场景(4G/5G)[64,83]条件下的DPD补偿技术也逐渐成熟化。

3 频率综合器校准技术

在实际的工程实现中,VCO振荡频率的PVT相关性会导致设计的振荡频率偏离10%~15%,因此为了覆盖所需的频点,频率综合器的设计通常都是具有一定输出频率范围的宽带电路,对于软件定义无线电等宽带应用场景更是如此。这就要求频率综合器在设计过程中需要在两个方面特别注意[4]:一是必须增加必要的自动频率校准(Automatic Frequency Calibration, AFC)功能,射频收发机中的VCO一般采用LC负阻结构,金属-绝缘体-金属(Metal-Insulator-Metal, MIM)电容网络实现输出频率的粗扫描,可变电容提供输出频率的精确锁定,粗扫描过程是由AFC模块来完成的,精确锁定通过锁相环来实现;二是必须提供稳定性校准功能,宽带频率综合器中的分频器通常会设计为小数分频结构,为了抑制SD调制器引入的高频噪声,锁相环通常采用4阶II型结构,当确定了锁相环的环路带宽后,无源滤波器的参数值决定了环路的稳定性,在宽带频率综合器中,输出频率以及输入参考频率的改变会改变环路带宽的值,同时随着频率的改变,VCO的电压-频率KVCO也会发生变化,对环路带宽同样也会造成明显的影响,恶化环路的相位裕量,甚至有可能出现自激的情况。

3.1 自动频率校准

AFC分为开环AFC和闭环AFC两种[92],如图9所示,开环AFC的锁定标记为VCO的控制电压位于两个参考电压Vrh和Vrl之间,其锁定速度较快,无须搜索完电容阵列的所有编码,仅以电压范围作为判决标准,但是开环结构容易受工艺及温度偏差的影响,不易锁定最优频率调谐线。闭环结构中,VCO的时钟频率对分频后的参考时钟高电平周期进行计数,随着MIM电容网络控制字的变化,VCO的输出振荡频率也变化,根据计数值与预设分频比的对比结果调整二进制搜索算法的搜索方向,并最终确定MIM电容网络的控制字。闭环结构中的计数器类型有单相(计数误差为1)[93]、双相(计数误差为1/2)[94]以及四相(计数误差为1/4)[92,95]等,其校准精度依次提升,但是所需要的计数器也会逐渐增多,电路设计复杂度及功耗相应增加。在上述基础上,文献[92,94,95]通过引入最小误差寄存比较模块使AFC的最终校准结果始终落在最优点所在的调谐曲线上,进一步加快了锁相环的锁定速度,同时增加了对PVT变化的鲁棒性。

图9 AFC校准方法

为了在减少计数器的情况下进一步提升AFC的锁定精度,文献[21]提出了一种仅需1个计数器的带有小数误差补偿逻辑的八相计数器,在减小电路设计复杂度的情况下将计数误差减小至1/8。为了进一步提高计数精度,在同样只需要1个计数器的情况下,文献[96]提出了一种基于TDC结构的小数误差补偿逻辑,可以将计数误差减小至任意范围之内,但是精度越高,TDC中所需的反相器和触发器也会越多,需要折中考虑。为了加快AFC的锁定速度,文献[97]提出了一种首先预存各频率调谐曲线对应的分频比的快速锁定方案,大大加快了AFC的锁定速度,但是此方法要求输入的参考频率是固定的,不适用于软件定义无线电场景。上述校准方法的校准时序均受控于输入参考频率,文献[98]提出了一种校准时序受控于VCO输出频率的校准方法,并采用计数误差自适应的方式尽可能在VCO高频情况下完成AFC过程,在没有增加复杂度的情况下大大减小了锁定时间。

对于包含多个VCO的频率综合器而言[94],在进行AFC锁定之前,首先需要确定选择哪一个合适的VCO,VCO的选择依赖频率综合器输出频率的大小。

3.2 稳定性校准

频率综合器环路稳定性的维持需要在完成稳定性预设计后保证环路带宽的恒定性,以4阶II型频率综合器为例,如图10所示,其环路带宽的表达式为[4]

其中,ICP为电荷泵的充放电电流,N为频率综合器的分频比,C1为环路滤波器的第1级电容值。因此如何维持上述参数之间的平衡性是稳定性校准需要解决的问题。

由于KVCO与输出频率的3次方成正比[4],为了避免KVCO的较大波动对环路稳定性造成影响,首先需要将KVCO恒定化,典型的做法有可变电容串联补偿方法[99]、分段补偿法[100]、温度计编码补偿法[101]等。完成KVCO的补偿后,通过电荷泵充放电电流ICP的可配置化(AFC控制)补偿分频比N的变化从而保证环路的稳定性[101]。在软件定义无线电应用场景中,需要兼容宽范围的输入参考频率,在输出频率保持不变的情况下,输入参考频率的变化会导致分频比N的变化,通常的做法是首先在最大输入参考频率的情况下按照上述步骤对环路进行补偿,然后在此基础上,通过将环路滤波器中的各无源器件参数值等比例可配置化来补偿输入参考频率的变化[4]。相应的校准示意图如图10所示,校准过程可概括为:(1)KVCO恒定化;(2)可配置ICP补偿分频比N的变化;(3)通过可配置化输入参考频率分频器和环路滤波器补偿输入参考频率的变化。

图10 频率综合器稳定型校准示意图

上述校准过程可以支持非常宽的输出频率范围及输入参考频率范围,但是电路复杂性较高,根据式(1)右边等式可知,环路带宽的恒定性仅与输出频率的平方成正比,因此仅通过可配置化ICP对输出频率的变化进行补偿也可以维持环路的稳定性[102]。但是此方法也面临一个严重的问题:当输入频率范围较宽时,低频段的KVCO值会被压缩得非常小,对工艺及温度变化的鲁棒性变差,极易导致失锁问题。为了解决此问题,通常的做法是通过等比例改变VCO中的电感值集成多个VCO,保证KVCO变化处于可接受的范围内[94]。

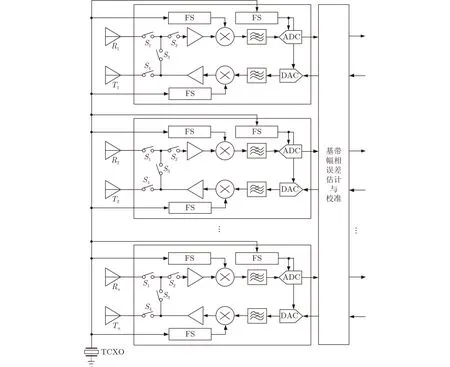

4 射频集成电路多片同步校准技术

5G时代,相控阵、MIMO技术得到了大规模应用,致使多通道射频收发集成电路逐渐出现,最典型的为ADI公司的2×2多通道RFIC—AD9361/AD9371/AD9375系列芯片以及4×4多通道RFIC—AD9026芯片。上述应用场景除了多通道需求外,还要求多通道射频收发具备射频同步性、基带同步性以及多通道的幅相匹配性。

多通道射频同步性主要依靠收发通道本振信号的相位同步性来保证,对于整数型频率综合器,只要能够保证输入参考频率的一致性,多个频率综合器在锁定后会自动保持一致。但是对于小数型频率合成器,即使处于锁定状态,由于Σ∆调制器的存在,无法保证可编程分频器的分频值顺序是完全相同的,因此多个小数分频器之间的相位是随机的,需要在锁定后重新复位Σ∆调制器,使可编程分频器的分频值顺序趋于一致,完成射频同步[103]。基带同步性主要是为了保证ADC和DAC的采样时钟是同步的,除了保证用于提供采样时钟的基带频率综合器的输出频率同步性以外(与射频同步相同),还必须在基带频率综合器完成同步后复位后续的外部分频器以保证采样频率的同步性,完成基带同步[49]。

对于射频通道的幅相匹配性,校准过程如下:首先在外部放置一个单音发射源,同时闭合开关S1和S2,选取任意接收通道为参考通道,剩余接收通道的输出依次(或者同时)与该参考通道的输出进行比较(相除),并将比较结果依次作为各对应接收通道的幅相补偿值[104,105],具体工作原理如图11所示。完成接收通道的校准后,可以将对应的系数写入(上电置位)数字基带处理模块中,避免每次上电后均需要校准。发射通道的校准是在接收通道校准完成的基础上通过回环的方式完成的(闭合S2和S3,断开S1和S4),校准方式与接收通道类似,只是信号需要通过发射链路从基带输入[106]。为了避免温度变化对幅相失配的影响,通常还需要在不同的温度值下进行幅相失配校准并存储校准系数,然后根据温度传感器选择需要切换的补偿系数。

图11 多通道幅相校准图

采用校准系数存储的方案对各通道由于老化导致的失配较敏感,为了保证校准精度的实时性,接收通道幅相失配校准的信号源可以通过芯片内部的频率综合器提供,即接收通道校准时的输入信号源可以由发射通道的射频频率综合器提供(射频同步完成后),这样可以保证芯片在每次上电时都可以进行一次校准,保证校准的实时性。

5 结束语

射频集成电路中的校准技术是高性能射频集成电路设计必须要克服的关键技术,这些校准技术种类繁多,实现复杂,且需要通过严格的状态控制逐一完成,是一项高难度的系统性工程。文中所述的校准技术是目前应用最广泛、效果最明显的10个核心校准技术,涉及射频收发链路、频率综合器、多片同步等3大方向,并且较全地给出了目前各类典型的校准算法,为高性能射频集成电路的设计打下了良好的基础。

前述的综述部分主要针对模拟域的收发架构进行了校准技术的归纳,由于工艺移植的便捷性、较强的抗干扰性以及对工艺温度偏差的极高鲁棒性,数字化技术逐渐成为射频集成电路设计中的一个重要发展趋势,下面简要从数字化的角度进行相关校准技术的综述。

(1)射频收发链路:射频收发链路的数字化可以很大程度上避免多数校准技术的使用,例如DCOC、偶次非线性失真、I/Q失配校准、谐波抑制技术、滤波器带宽校准以及本振泄露校准等,但是对于接收链路而言,目前数字化技术的主要矛盾还是集中在高精度高采样速率ADC的研究上,针对某些专用应用场景,射频接收链路的数字化具备较大的实现可能性,但是在大多数应用场景中,尤其是软件定义无线电应用场景,短期内并不能取得较明显的突破,可以肯定的是,零中频架构和低中频架构仍会在射频接收链路的设计实现中占据可观的时间长度,上述校准技术仍是高性能接收电路设计所必需的。发射链路的数字化目前已经取得了非常明显的进步,典型的数字化发射架构包括数字极化发射机[107–109]、数字正交发射机以及数字LINC发射机[108],内置的数字化PA包括数字Doherty PA[62]、数字化Class-D PA[107]、数字化Class-G PA[59,60]、LINC class-E PA[110]等。但是数字化发射机内部的工作时钟通常处于过采样状态,对于高码速率通信系统而言消耗的功耗较高。如果采用极化发射架构,还需内置数字相位插值器[111],该插值器的固有延迟对工艺/温度变化同样敏感,极易恶化PA的频谱性能。另外,极化/LINC架构中内置的Cordic算法本身固有的非线性会进一步拓展幅度支路和相位支路的带宽,对芯片内部的工作时钟要求更高。同时,正交架构和LINC架构还需额外增加一个数字PA来实现相应的电路功能[108],在发射功率较大时,功耗会明显上升。

但是,无论是采用模拟架构还是数字架构,对于发射链路而言,PA的DPD补偿在调制信号的峰均比较高的情况下仍是确保高性能发射的必需手段。

(2)频率综合器:全数字频率综合器(All Digital Frequency Synthesizer, ADFS)最早是2003年由TI公司的Staszewski等人[112]提出并设计实现的,采用计数器和TDC结构替换模拟域的PFD+CP结构,数字滤波器替换环路滤波器等实现频率综合器的数字化,根据计数器位置的不同,可分为锁相或者锁频型数字频率综合器。数字频率综合器中不存在模拟域中PFD+CP和环路滤波器引入的相位噪声,但是各模块却增加了量化噪声,并且异步时钟(LO时钟和输入参考时钟)的同步操作还会引入不可避免的亚稳态现象。其校准仍分为AFC和稳定性校准两部分[113],AFC部分的校准相较于模拟域电路而言,更加复杂,为了避免VCO中电容阵列过大,AFC过程共包括3部分:粗精度AFC、中等精度AFC以及高精度AFC,通过对滤波后的数字相位误差进行判决实现三者之间的串行切换。ADFS同样也存在稳定性的问题,但是ADFS中不存在电荷泵、分频器等模拟模块,因此稳定性仅受数控振荡器(Digital Controlled Oscillator, DCO)增益KDCO的影响,DFS的稳定性校准通常是通过对DCO模块进行增益归一化实现的[113]。

(3)多片同步校准:由于ADFS是通过TDC产生相位/频率误差的小数部分,因此不存在Σ∆调制器产生的随机分频现象,锁定后ADFS即实现输出频率的相位同步,同时发射链路的数字化也无需进行多通道发射链路的幅相失配校准。