S波段超宽带抗干扰发射信道的设计与实现

2022-11-08侯武斌

侯武斌

S波段超宽带抗干扰发射信道的设计与实现

侯武斌

(中国西南电子技术研究所,成都 610036)

S波段超宽带抗干扰发射信道作为卫星通信系统机载终端的核心设备,其信道的抗干扰能力直接影响着整个系统的性能。通过跳频技术来提升通信系统的抗干扰能力的关键是提高跳频速度和拓展跳频带宽,因此该超宽带信道杂散、增益平坦度以及载波的低相噪、捷变频速度等性能指标的优劣就显得极为重要。本文基于传统通用芯片设计了采用二次变频的宽带收发信道,通过切换混频本振、分段开关滤波、多通道一体化集成设计,实现了超宽带信道低杂散、低相位噪声以及高速换频等关键技术指标,并在实际工程应用上得到了验证。

超宽带;低杂散;低相噪;捷变频

0 引言

随着信息传输速率的加快,多用户同时使用需求的提高以及密集复杂多变的电磁干扰环境,无线通信系统向着宽带、集成化及多载波抗干扰方向发展。这些需求和发展,导致收发系统载波的工作频率和瞬时带宽越来越宽,载波的跳频速度也越来越高,通过提高载波跳频速度和拓展跳频带宽来提升通信系统的抗干扰能力就成为了当务之急。其中射频收发信道的宽带设计就成为关键和重点,宽带信道[1]的杂散,增益平坦度,载波的低相位噪声和载波频率的高速捷变频设计,对整个信道性能指标的优劣显得至关重要。

本文选用国内外先进的器件和工艺,采用理论公式计算、软件仿真与硬件电路实物相结合的设计方法,完成S频段超宽带抗干扰发射信道的研制[2]。其信道内集成有两路发射通道(含本振频综)、五路接收通道(含本振频综);在外部终端RS422串口的控制下,采用ARM+FPGA来实现工作模式切换、射频参数配置、跳频控制等功能;信道具有常规、跳频两种工作模式,两种模式分时工作,全双工方式。

1 总体设计方案

发射信道是将70 MHz中频信号带宽选择后上变频到S频段,带宽扩展到1 600 MHz,信道自身混频产生的低阶组合频率落入发射带宽内形成杂波,需要通过频率优化,使组合频率分量尽可能少的落入工作带宽内,对于宽带系统无法避免时就要求落入带内的干扰信号组合阶数高,通过适当降低产生组合交调杂散的基频信号功率来减小干扰电平,也可通过对输出信号分段开关滤波来避免组合交调杂散落入信号带内,减小相应中频滤波器的实现难度[3]。为满足系统杂散指标抑制,本发射信道采用二次上变频,将输出S频段信号划分为四段,每段带宽为400 MHz,分段开关滤波,使落在中频带内的组合干扰能满足系统使用要求[4]。

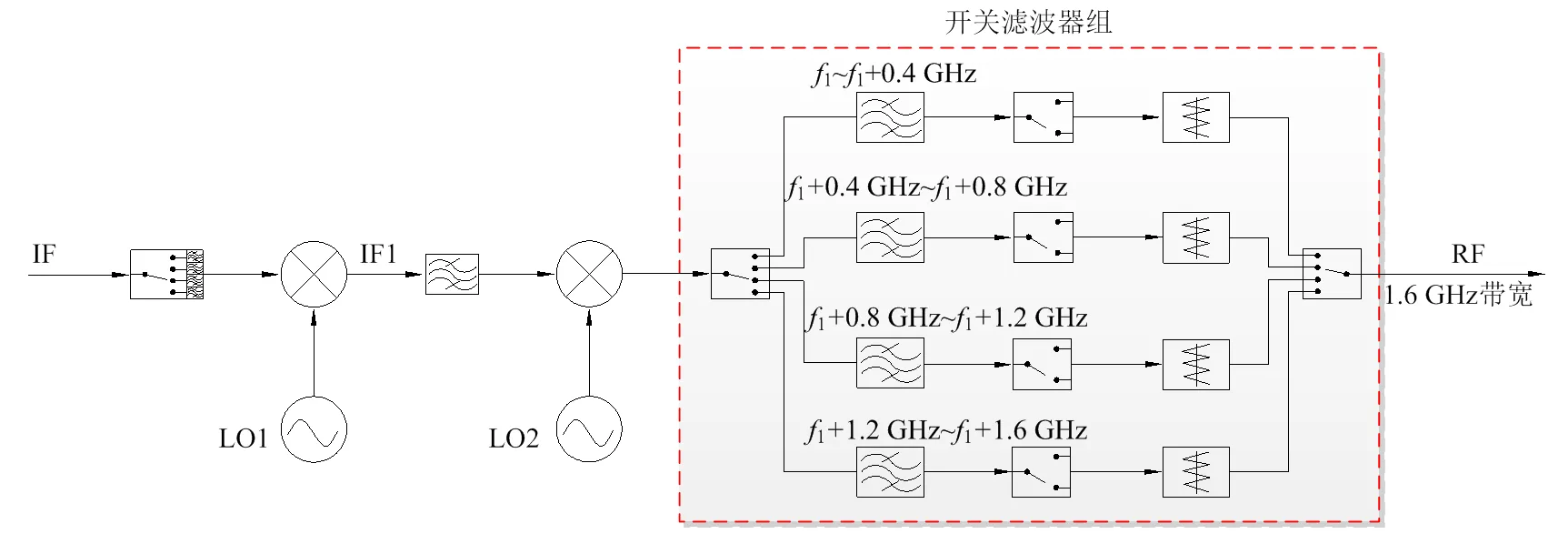

发射信道电路组成框图如图1所示,发射信道首先将IF中频信号进行带宽选择,滤波放大与一本振信号LO1上变频到IF1,经滤波放大与二本振信号LO2上变频到RF,然后分段开关滤波,放大后通过数控衰减器调节信号输出幅度,再与100 MHz参考时钟信号合成后输出,数控衰减的调节范围为50 dB。

发射频综包含P波段一本振和C频段二本振,其中一本振为单点频,频率为LO1,由带压控振荡器(Voltage Controlled Oscillator,VCO)的集成锁相环ADF4360-5产生,后经放大、滤波、功分两路输出[5]。二本振LO2为C波段宽带频综,采用乒乓环设计,频率带宽1.6 GHz,步进为100 Hz,跳频周期小于200 μs,换频时间小于5 μs。

图1 发射信道电路组成框图

2 关键电路指标设计与实现

2.1 发射信道杂散指标分析

输入中频信号与两个本振混频,除了得到所需频率信号外,由于混频器的强烈非线性作用,还产生了大量组合杂散信号。在方案设计上,对两个混频本振分别采用高本振方式,使得本振信号落在所需信号带外,以便于滤波器滤除;对两个混频本振分别采用单刀单掷开关以提高本振之间的隔离度;对混频后的宽带射频信号,采用开关切换分段滤波器组,各段均采用单刀单掷开关提高隔离度[6]。

发射信道部分的杂波主要来源于三个方面:一是混频产生组合分量以及本振信号落在带宽内成为杂波;二是频综产生的杂波进入发射带宽成为杂波;三是信号空间泄漏杂散。

2.1.1 混频产生组合分量以及本振信号落在带宽内成为杂波

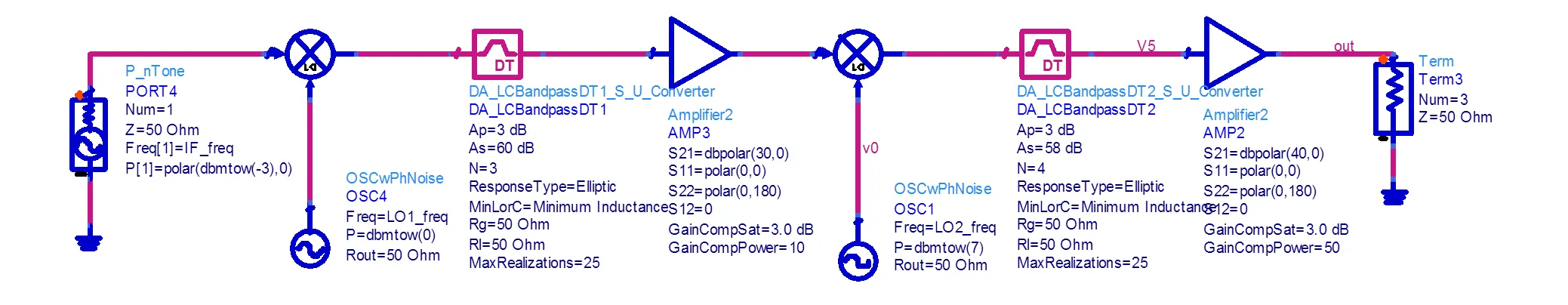

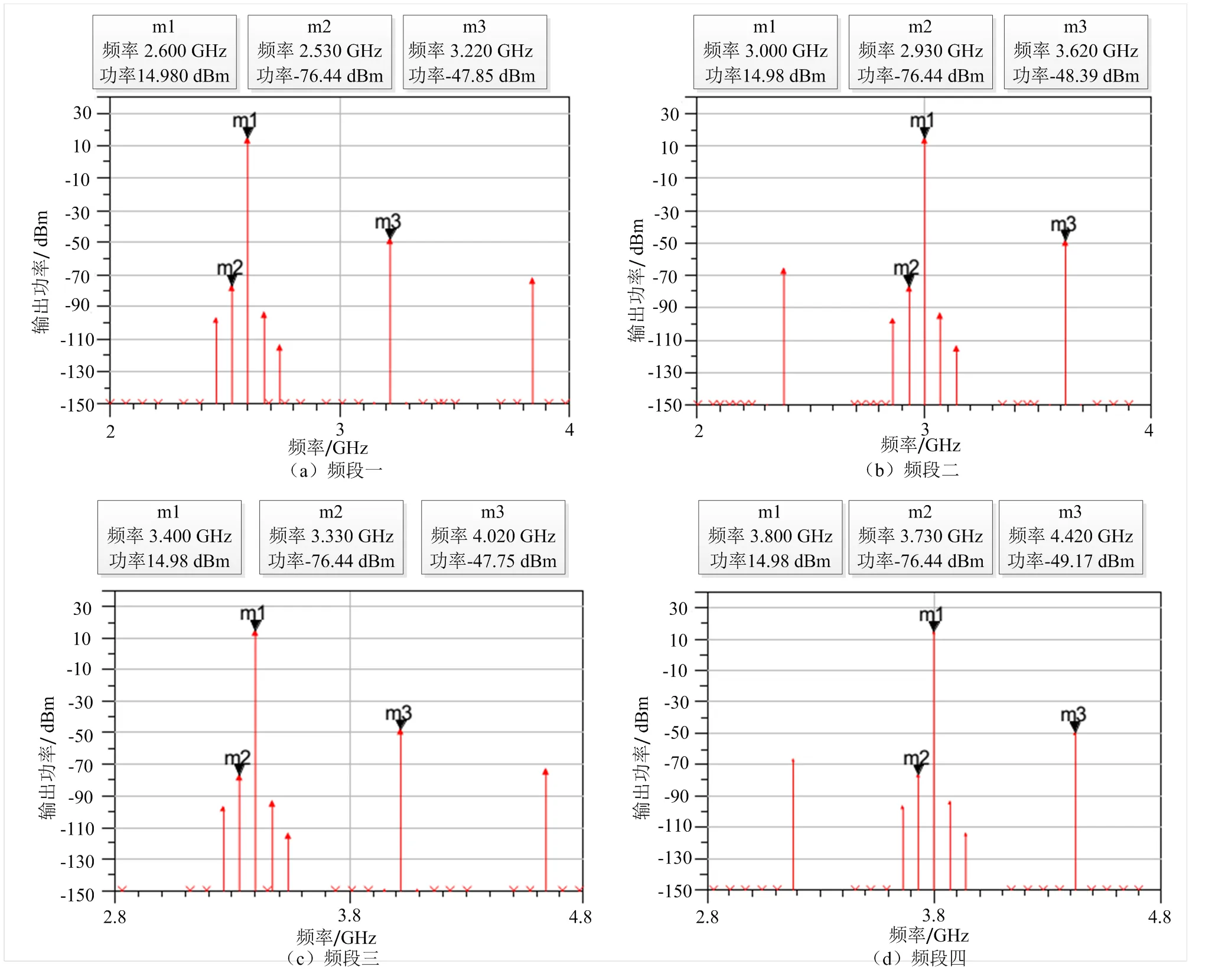

对于第一种杂波,首先在ADS中建立模型用谐波平衡法仿真[7]计算,通过频率关系找到可能存在的交调干扰的分量,再结合其信号幅度、混频器压缩点以及滤波器性能进行分析。图2为发射信道的ADS仿真模型,图3为发射信道杂波抑制ADS仿真结果。

图2 发射信道ADS仿真模型

图3 发射信道杂波抑制ADS仿真结果

由于发射信道的一混频,本振为固定点频,信号带宽为20 MHz,带宽较窄,输出的带通滤波器对本振信号以及组合的交调杂波抑制相对容易实现,可以比较容易的实现杂波65 dBc的抑制,因此我们重点来分析二混后信道杂散的抑制情况。

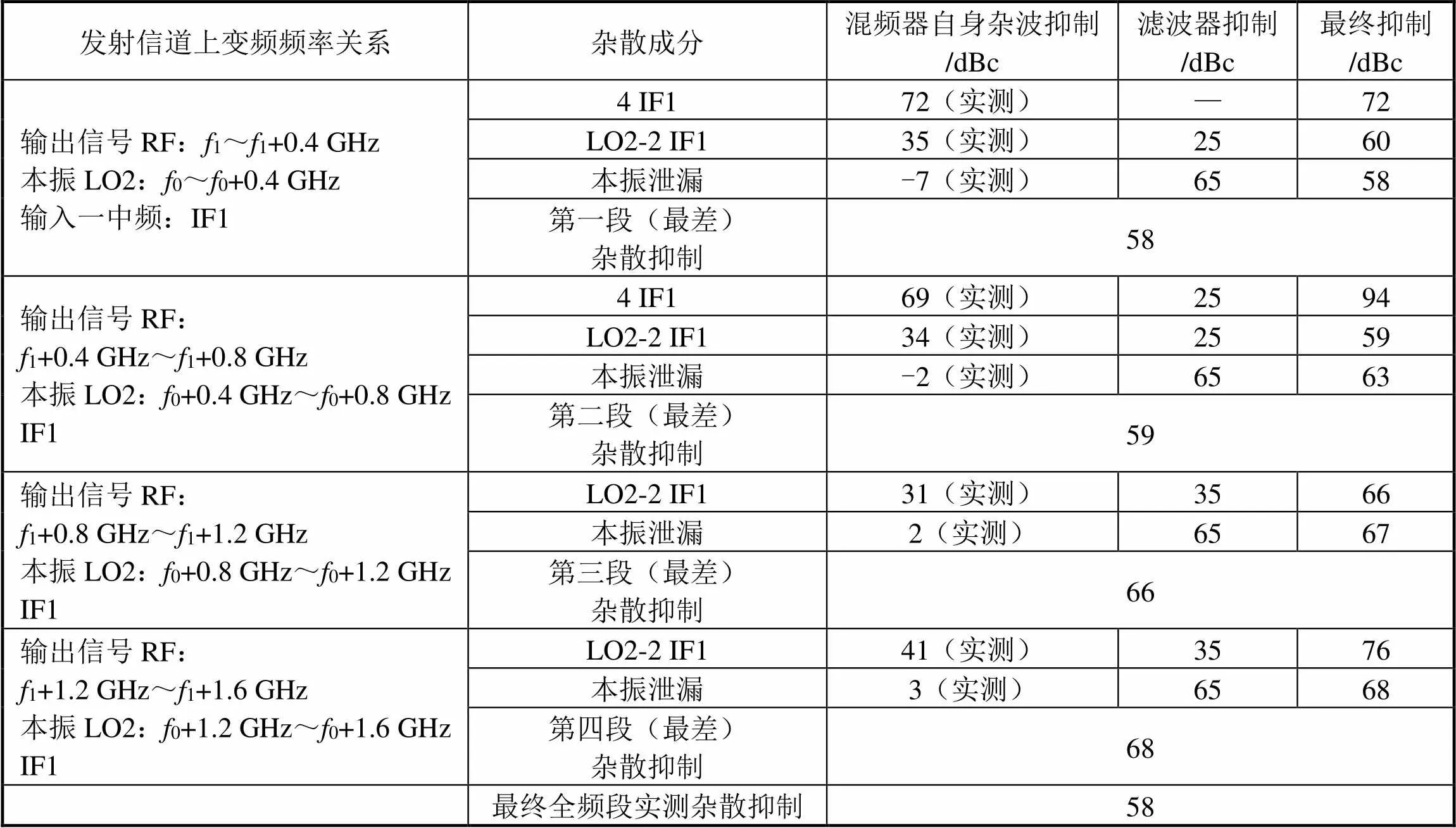

发射二混后,由于混频后对输出信号分为4个400 MHz频段,用分段开关滤波组件对杂波进行抑制,因此对发射混频分4段进行交调干扰仿真,其仿真结果如表1所示(表1测试条件为:一中频IF1输入电平-7 dBm,本振LO2电平13 dBm)。

表1中可看出,发射带内存在的最低阶组合干扰量是4阶,混频器自身对+4×IF1(2.48 GHz)的抑制为72 dBc,满足指标要求。

低端最低阶组合干扰+1×LO2-2×IF1,混频器自身抑制再加上滤波器的抑制,最差杂散抑制为59 dBc,满足指标要求。

高端最低阶组合干扰+1×LO2,由于混频的本振信号为+13 dBm,本振通过混频器泄漏到射频端口的信号为-12 dBm(混频器本振与射频的隔离度为25 dB),主信号经过变频后功率为-12 dBm,本振信号的泄露与主信号电平相同,最终主路信号上的杂波(本振泄露)抑制,完全取决于分段开关滤波对本振信号的抑制,最差杂散指标为58 dBc。

表1 发射信道二混后杂散分析

2.1.2 频综产生的杂波进入发射带宽成为杂波

对于第二种频综产生的杂波,要求其杂波抑制达到60 dBc以上。频率综合器的杂散成分主要有以下来源:直接数字频率合成(Direct Digital Synthesis,DDS)产生的杂散、锁相环(Phase Locked Loop,PLL)的鉴相频率泄漏和开关电源频率调制杂散。

DDS的杂散主要来源于三个方面:相位截断误差、幅度量化误差和DAC的非线性。虽然目前针对这三种杂散来源有一些改善DDS输出频谱质量的方法,但都需改变DDS内核设计。

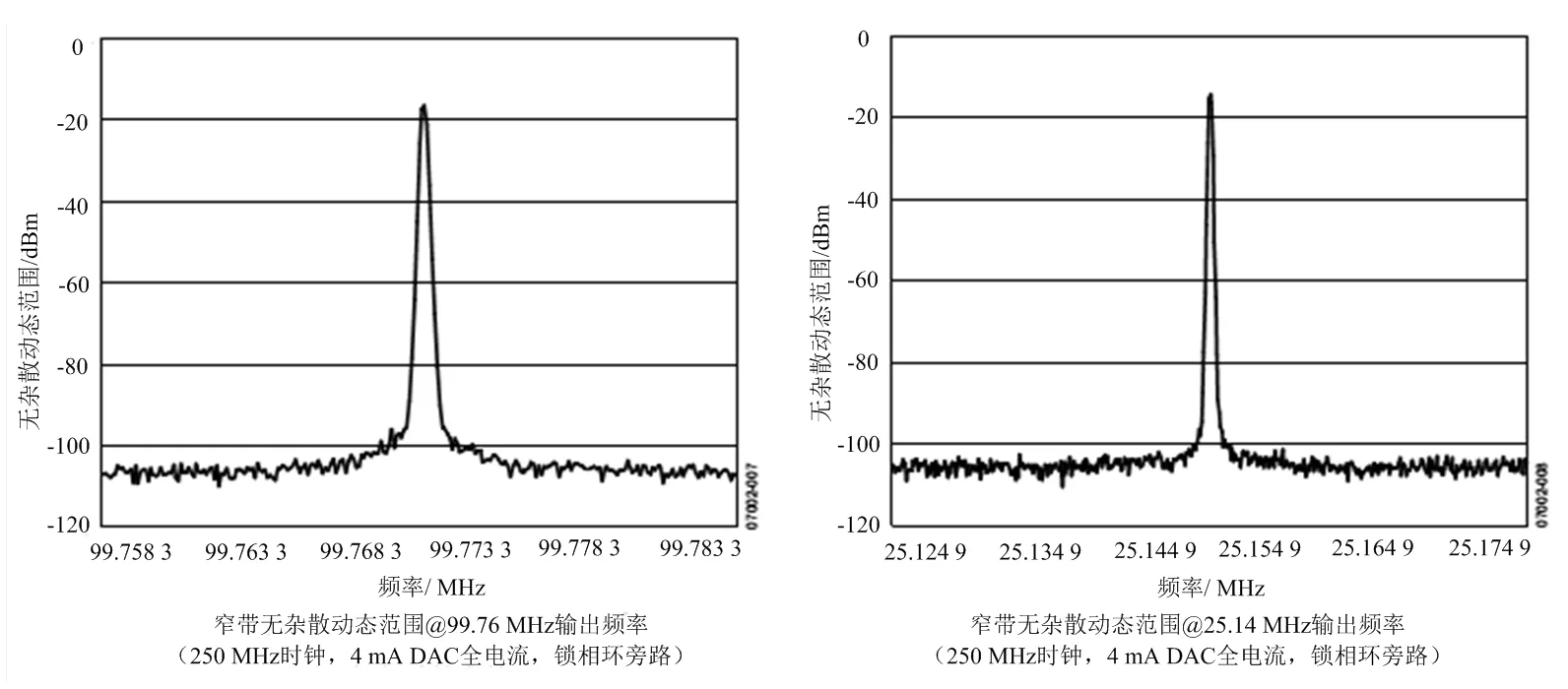

本文DDS选择的是AD9913,其典型杂散电平如图4所示。根据器件手册介绍,AD9913输出信号近端杂散优于80 dBc,经锁相环倍频恶化37 dB,杂散只有43 dB,不能满足指标要求,因此,DDS输出频率范围尽量选窄,并且选择杂散较小的一段(根据实验结果,选出杂散优于100 dBc的一段),以满足DDS杂散指标要求。

图4 AD9913典型杂散电平图

频综器中锁相环的鉴相频率分别为50 MHz和DDS输出频率,由于鉴相频率较高,通过合理选择环路带宽,加强电源滤波隔离,能够对鉴相参考信号实现很好的抑制,可以达到约65 dB的抑制度。

对于电源频率调制杂散,对PLL电路采用二次线性电源稳压,加强VCO等敏感器件的电源滤波等措施可以抑制到较低的水平。根据经验,可以将这种杂散抑制到65 dBc以下。由以上分析,频综输出信号杂散抑制能够满足60 dBc的指标要求。

2.1.3 信号空间泄漏杂散

对于第三种杂波,在空间泄漏杂散方面,做好不同信号腔体间的屏蔽隔离,杂散相对容易满足系统指标要求。

2.2 本振相位噪声指标分析

发射一本振为单点频,由带VCO的集成锁相环ADF4360-5产生,后经放大、滤波、功分两路输出。

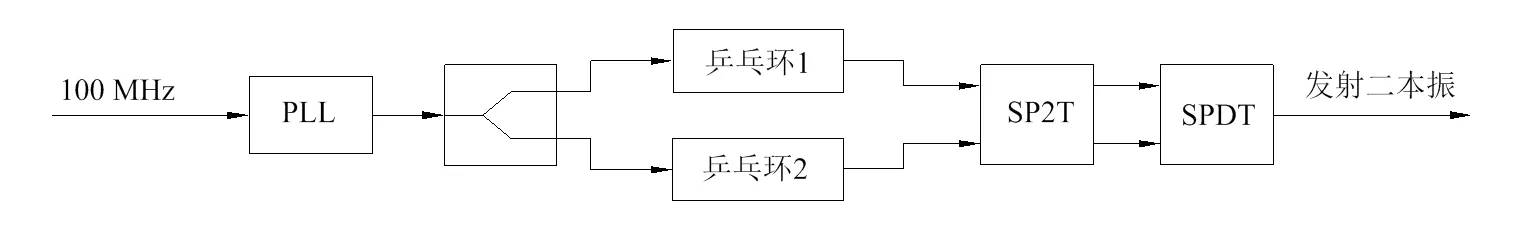

图5 发射二本振工作原理框图

发射信道二本振工作原理框图如图5所示。发射二本振为C波段宽带频综,带宽1.6 GHz,频率步进为100 Hz,跳频周期小于200 μs,换频时间小于5 μs。为保证5 μs的换频时间,频综采用乒乓环设计,即两个完全一样的频综同时工作,接收跳频指令后通过单刀双掷开关进行切换,同时单路上增加单刀单掷开关来提高乒乓环输出信号之间的隔离度,减少信号串扰。

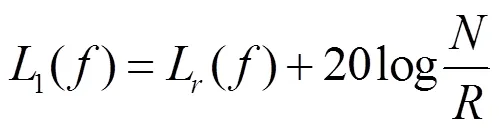

每个独立的频综[8]采用DDS+PLL的方式实现,通过DDS输出保证100 Hz的频率步进。DDS选用AD公司的超低功耗器件AD9913,时钟信号为 250 MHz,由晶振输出的100 MHz参考信号通过鉴相器ADF4002锁相得到,DDS输出频率 61~62.5 MHz,作为末级锁相环的参考信号,锁相环选用Hittite公司的HMC704LP4,采用小数分频模式,VCO选用十三所的微封装压控振荡器,最终输出C波段宽带频综信号[9]。

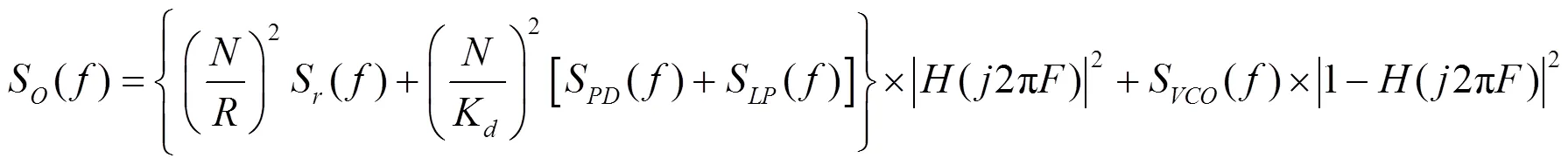

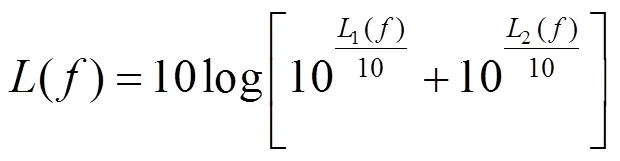

本振信号的相位噪声是所有噪声同时作用的结果[10]。锁相环附加噪声源的系统框图如图6所示。数字锁相环在锁定状态下可以认为是线性系统,应用线性叠加原理,将各噪声源反映到本振源输出端的相位噪声功率谱密度相加,则可得到总的相位噪声功率谱密度,单位为dBc/Hz,如式(1)所示:

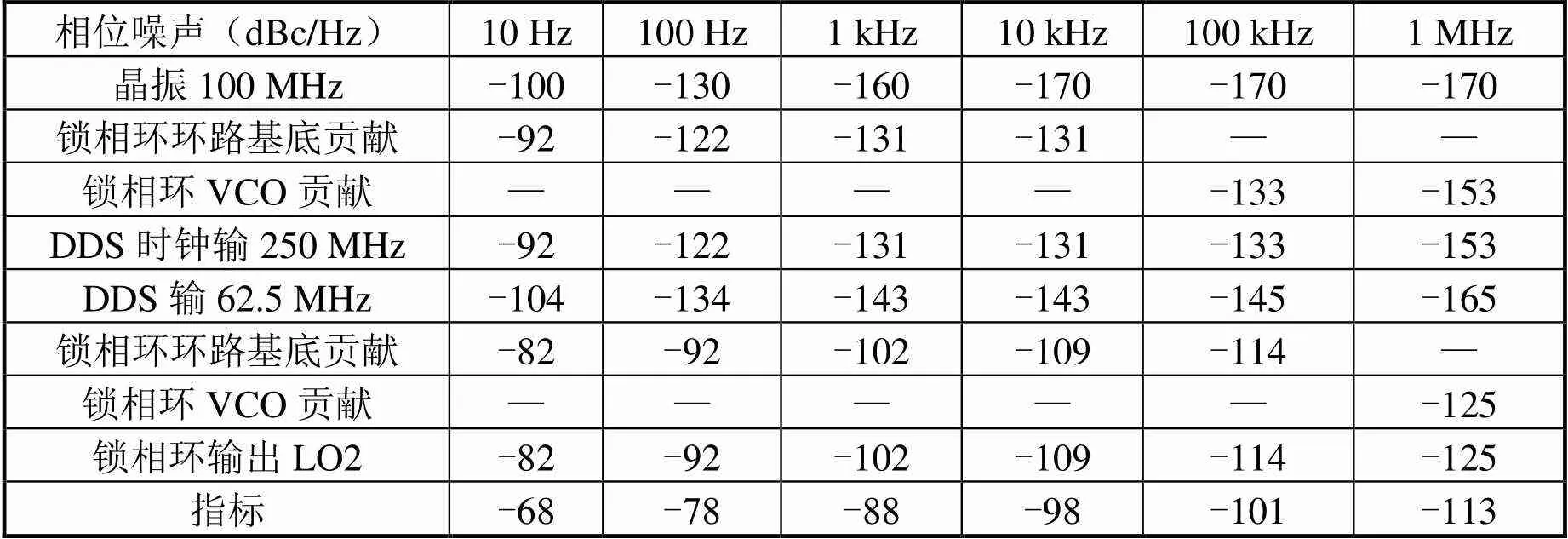

发射二本振相噪指标分析如表2所示。 100 MHz晶振作为参考信号通过鉴相器ADF4002锁相得到250 MHz,作为DDS的时钟,输出频率61~62.5 MHz,DDS输出频率作为末级锁相环的参考信号,锁相环选用Hittite公司的HMC704LP4,采用小数分频模式,最终输出C波段宽带频综信号。其中,前级和后级锁相环的环路基底相位噪声贡献包含对应鉴相器ADF4002/HMC704 LP4基底和环路滤波器的基底相位噪声贡献。由表2可见,相位噪声指标可满足系统要求。

表2 发射二本振相噪指标分析

2.3 本振换频时间指标分析

发射信道二本振乒乓环工作原理如图7所示。

图7 本振乒乓环工作原理框图

频综采用乒乓环方案,即两个预先锁定的频综通过开关切换,换频时间取决于开关切换时间,开关选用HMC336MS8G,其切换时间为20 ns左右,满足指标要求。

跳频周期包含频综控制时间和环路锁定时间。采用FPGA作为频综的控制器,实现频率控制字的译码计算、对DDS的串口控制和对开关通断状态的译码控制。FPGA的写操作包含了两个部分,一个是对DDS寄存器进行操作,需要进行64 bit的写操作,另一个是对PLL704进行写操作,需要进行48 bit写操作,由于采用25 MHz的移位时钟,故写操作大约只需要5 μs,再考虑到时序可靠保证处理所花费的时间,FPGA的解析和送数实际处理时间应该小于10 μs。环路带宽取200 kHz左右,环路锁定时间约为50 μs。因此,换频周期约为60 μs,满足指标要求。

3 实验结果及其分析

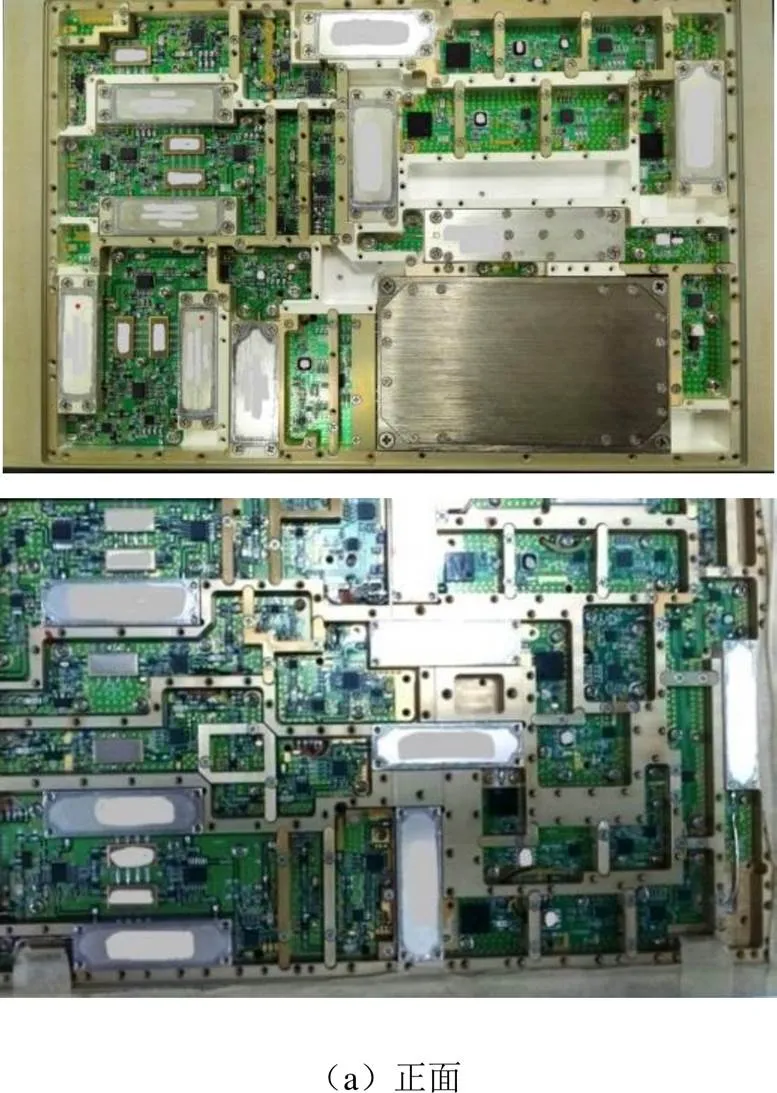

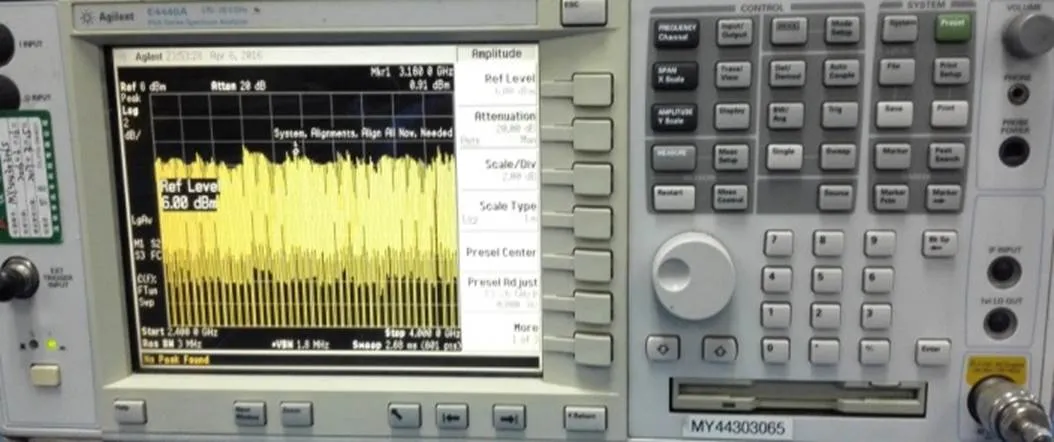

收发信道实物照片如图8所示,反面为对应变频通道的本振频综,利用测试工装夹具通过控制变频信道的二本振频综对整个发射频段1.6 GHz的信号进行扫频,观察1.6 GHz带宽内,杂散最差为 58 dBc,满足系统杂波抑制55 dBc的要求。发射信道1.6 GHz带宽内的增益平坦度实测曲线如图9所示。

图9 发射信道1.6 GHz带宽内的增益平坦度实测曲线

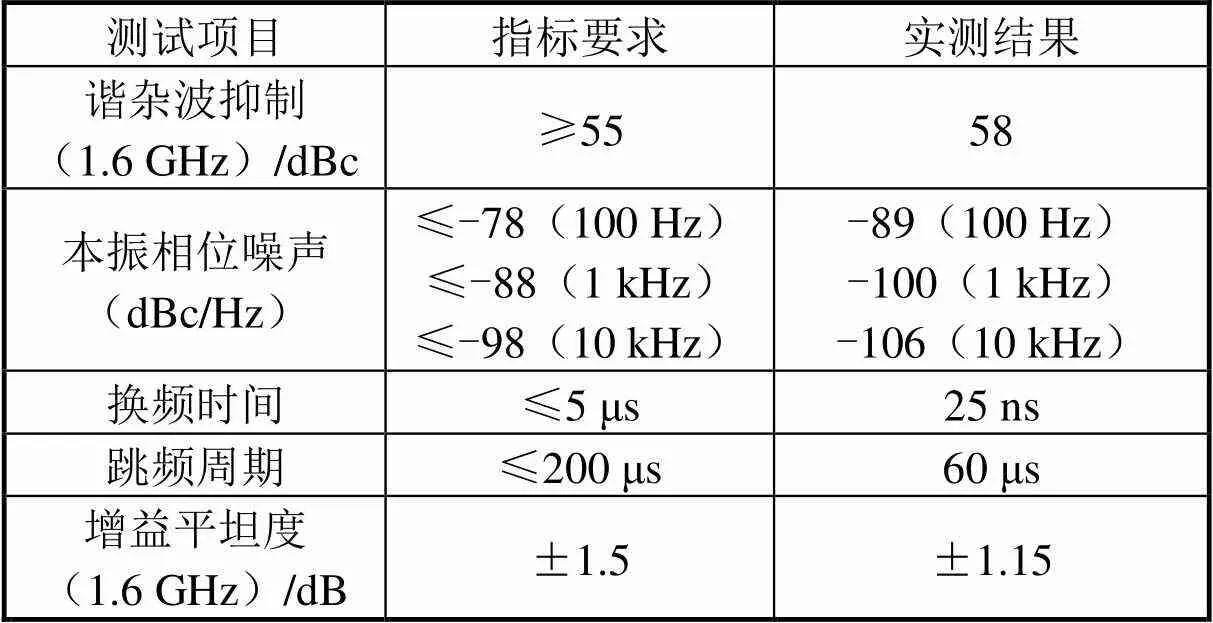

发射信道实测结果如表3所示,与仿真结果基本吻合,满足该S波段超宽带抗干扰收发信道系统的使用需求,这说明本文所提出的超宽带抗干扰收发信道的变频以及频综电路方案设计合理,电路布局优化,设计方法是完全可行的。

表3 发射信道实测指标

4 结语

本文对S频段超宽带抗干扰发射信道的低杂散、低相噪、本振捷变频设计做了详细的分析,提出合理的变频方案,并对重要指标进行了论证和计算。其中,各收发通道均采用独立腔体屏蔽布局和二次电源独立稳压设计,减少收发信号的空间和电源串扰,实现了收发75 dB的高隔离度,避免了系统杂波恶化,同时充分利用软件建模仿真和实物测试验证的对比结果,不断改进优化设计手段。通过采用微波复合多层板优化印制板布线,合理规划频率关系,降低频综设计的难度等方面提高设备的电磁兼容性能。从最终实物测试结果来看,该变频信道性能指标优良,实现了1.6 GHz超宽带信道58 dBc的杂波抑制、C频段本振频综-100 dBc/Hz@1 kHz低相位噪声以及25 ns的本振高速换频时间,全面满足了系统指标要求,在实际工程应用中设备状态表现优异稳定可靠。

[1] 刘伯文,梁剑锋,崔平. 一种宽带Ka频段上变频模块的设计与实现[J].无线电工程,2019,49(1):72-75.

[2] 姚若妍,魏斌. Ku波段收发组件设计分析[J]. 电子与封装,2016,16(2):33-36.

[3] 校莉. Ku频段无线数字通信系统射频信道设计[D]. 成都:电子科技大学,2009.

[4] 闫超,赵家敏,姚武生. 一种S波段高线性度下变频模块的设计[J]. 雷达与对抗,2017,37(2):55-107.

[5] 陈杨梦,张伟昆.一种基于AD4360-9和FPGA的合成时钟源设计[J].桂林电子科技大学学报,2019,39(3):223-228.

[6] 王立生. 一种新颖的捷变频频率合成器设计[J]. 电讯技术,2011(12):105-108.

[7] 雷兴旺,原庆,尹华. 毫米波上变频模块的仿真与设计[J]. 现代信息科技,2020,4(5):42-44.

[8] 孙吉良,何勰,申江江,等. 基于DDS和PLL的LFMCW雷达频率源设计与分析[J]. 国外电子测量技术,2021,40(1):106-109.

[9] 柴俊,张必龙. Ka波段频率合成器设计[J]. 舰船电子对抗,2021,44(1):87-91.

[10] 李春利. 频率源相位噪声性能提升方法研究[J]. 现代雷达,2021,43(1):76-80.

[11] 侯武斌. 一种新颖的内外频标自适应式时钟源的设计[J]. 现代电子技术,2009,32(9):175-177.

Design and Implementation of S-Band Ultra-Wideband Anti-Jamming Transmission Channel

HOU Wubin

S-band UWB anti-jamming transceiver channel is the core equipment of airborne terminal of satellite communication system,The anti-interference capability of its channel directly affects the performance of the whole system. The key to improve the anti-interference ability of communication system by means of frequency-hopping technology is to increase the frequency hopping speed and expand the frequency hopping band width. Therefore, the performance indexes of UWB channel, such as spurious, gain flatness, carrier low phase noise, fast frequency conversion speed, are very important. A broadband transceiver channel with secondary frequency conversion is designed based on traditional universal chip. By switching mixing local oscillator, segmented switching filter and multi-channel integration design. The key technical indexes of UWB channel such as low spurious (58 dBc), low phase noise and high speed frequency hopping are realized and it is verified in practical engineering application.

UWB; Low Spurious; Low Phase Noise; Fast Frequency Conversion

TN927+.2

A

1674-7976-(2022)-05-350-08

2022-09-06。侯武斌(1980.05—),陕西宝鸡人,工程师,主要研究方向为微波射频组件及射频系统集成。