采用反馈时钟检测的锁相环校准电路设计

2022-10-29张礼怿张沁枫

张礼怿,张沁枫,俞 阳,卓 琳

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

压控振荡器(VCO)作为锁相环(PLL)中的关键模块,其性能在很大程度上决定了PLL的综合工作性能。通常低相位噪声、宽频带单片PLL电路多采用电感电容压控振荡器(LC-VCO),且所用的电感为固定值电感,振荡频率调整由电容变化来实现。为了覆盖较宽的调谐范围,业内常采用开关电容阵列构成连续且有部分重叠的多个子频带[1],作为LC-VCO的粗调电容,可变电容作为LC-VCO的细调电容,以此来实现目标频率的锁定,配合自动频率校准(AFC)[2]技术选择合适的子频带,可以优化输出噪声。同时,LC-VCO中的晶体管性能会随工作频率的变化而变化,从而导致其电压输出幅度的变化,而电压输出幅度的变化也会影响LC-VCO的输出噪声性能,因此有必要同时进行VCO的自动幅度校准(AAC)[3]。

传统AFC电路可分为开环校准[4]和闭环校准[5]两大类,近年来也出现了很多校准电路新结构[6-7]。闭环校准电路通过将VCO调谐电压与2个参考阈值电压进行比较,来调整开关电容的接入大小;开环校准电路的VCO调谐电压为固定值,通过在固定时间窗口中计算VCO的周期并与所需周期进行比较,来调节接入电容的大小。相较于闭环校准依赖整个环路条件,开环校准的灵活性更高。此外,AFC可以分为数字AFC、模拟AFC、数模混合AFC,数模混合结构AFC兼具易于实现、误差小和工作频率高的优点[8]。

本设计在传统数模混合结构AFC的基础上,采用开环模式、利用反馈时钟的采样触发机制进行频率检测,在只增加部分数字电路和少量模拟电路的前提下提高了频率校准精度,实现了自动频率校准,有效降低了VCO噪声在PLL输出噪声中的占比,最终实现了PLL频率综合器的相位噪声和均方根抖动指标的提升。

2 自动校准流程及电路设计

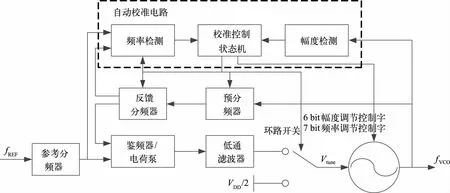

VCO自动幅度、频率校准电路结构如图1所示,控制校准过程的有限状态机(FSM)在校准启动后切断原有PLL环路,将VCO的控制电压Vtune钳位在电源电压的一半,即VDD/2,同时将预分频器(DIVP)和反馈分频器(DIVN)设置为固定分频比,根据输入的频率检测结果和幅度检测结果,FSM向VCO输出6 bit幅度调节控制字和7 bit频率调节控制字,图中fREF为参考时钟输入频率,fVCO为VCO输出频率。

图1 VCO自动幅度、频率校准电路结构

目标VCO的频率范围为2.7~3.1 GHz,由于Vtune受限于电源电压,为实现宽调谐范围,需要压控增益KVCO值很大,这就需要可变电容的C-V曲线非常陡峭,从而导致可变电容调频-调幅(AM-FM)效应带来的噪声急剧增加[9]。因此本设计采用电容阵列将VCO划分为多个子频带。为进一步提高VCO的近端噪声性能,采用PMOS交叉耦合对结构,尾电流源采用开关电阻阵列结构,利用电阻改变偏置电流大小,有效地隔绝地和MOS电流管的噪声进入VCO。

2.1 自动校准流程

校准控制状态机的输入为幅度控制字初始值、频率控制字初始值、幅度初始阈值VT1、幅度最大阈值VT2、频率初始阈值fT1、频率最大阈值fT2,以及3个确认计数器阈值N1、N2和N3,相关控制信号有幅度检测反馈信号、频率比较反馈信号、状态机使能信号和复位信号,状态机输出为幅度比较使能、幅度控制字、频率检测使能、频率检测触发脉冲和频率控制字。VCO自动校准启动时,VCO可以通过寄存器预设幅度控制初始值正常启振;频率控制初始值设置在接入最大电容值处,使频率检测可以从最低频率开始。自动校准流程如图2所示。

2.2 幅度校准电路

自动幅度校准电路(AAC)如图3所示,主要由参考电压偏置电路、采样比较器以及数字状态机3部分组成[10]。VCO的输出信号通过缓冲电路由差分信号转换为电压信号,输入电压比较器的一端,比较器另一端输入的是预设参考电压,模拟电平比较器将两者比较后的结果反馈到数字控制状态机中,数字状态机根据输入的比较结果对幅度控制字进行调整。

图2 自动校准流程

图3 自动幅度校准电路

2.3 频率校准电路

自动频率校准电路(AFC)在设定目标频率后通过切换固定分频比,利用fREF和fVCO应有的比例关系来进行频率校准,即fREF/M=fVCO/(P×N),其中M为参考分频比,P为预分频比,N为反馈分频比。本设计采用的是基于反馈时钟信号连续触发固定周期数的参考信号来实现频率检测的方法,该方法利用了连续除2分频器构成的N分频器的输出信号特性。

反馈分频器电路结构如图4(a)所示,反馈分频器FDIVN由20级连续电流模式逻辑(CML)结构除2分频器串联构成,再通过CML结构逻辑与门将逐级2分频后的输出信号相与。D[19:0]是20级分频器的置位端,分频计数的初始值对应D[19:0]的值取反。FDIVN_EN信号则是使能信号,FDIVN_EN为0时,反馈分频器处于置位状态;FDIVN_EN为1时,反馈分频器处于计数状态。fVCO经过预分频器输入反馈分频器时钟端FDIVN_CP,计数器对输入的时钟信号进行连续计数,终值为0xFFFFD。

反馈分频器的输出FDIVN_OUTN接触发器DFF1的D端,CP端信号则与反馈分频器时钟相同,当计数到0xFFFFD的时候,FDIVN_OUT由低变为高,在下个fVCO/P上升沿时,DFF1采样到低电平,它的QN端 输 出 到MUX1,MUX1的 输 出 反 馈 到FDIVN_EN。因此在计数到终值0xFFFFD后的下个FDIVN_CP上升沿时,FDIVN_EN为0,FDIVN进入置位状态,载入此时D[19:0]的值,同时使反馈分频器的输出OUT也由高变为低,DFF1在下个时钟上升沿采样到低电平,通过MUX1反馈到FDIVN_EN,工作时序如图4(b)所示。MUX1在正常分频状态时,选择IN2作为输入,而在频率校准状态时则选择IN1作为输入,此时的IN1是专为校准进行重定时的A_CP信号。

图4 反馈分频器电路和时序

AFC的频率检测由重定时电路和触发电路来实现,频率校准电路如图5所示,重定时电路利用校准控制状态机给出的N2_A、fREF、fVCO/P信号产生关键的触发信号A_CP,而状态机给出的N2_ENQ信号则用于复位触发电路中的锁存器RS1和2个触发器DFF5和DFF6。

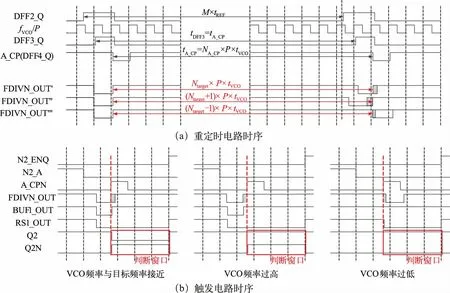

重定时电路的3个CML结构触发器中,DFF2用fREF触发,DFF3和DFF4用fVCO/P触发,通过DFF4的Q端来复位DFF2和DFF3,使得DFF4的输出信号A_CP/A_CPN(DFF4_Q/QN)的脉宽固定为一个fVCO/P周期。重定时电路时序如图6(a)所示,状态机输出的N2_A脉冲周期为M个参考时钟周期tREF,到达重定时模块后用fREF信号在DFF2进行边沿对齐,DFF2_Q在输入到DFF3后,被fVCO/P触发,再经过DFF4的复位,使得DFF3的输出周期tDFF3与DFF4的输出周期相同,而DFF4的输出DFF4_Q为关键信号A_CP,它的周期tA_CP为整数NA_CP个P乘以VCO输出时钟周期tVCO,其中高电平为(NA_CP-1)个P×tVCO周期,低电平为1个P×tVCO周期。在进行频率校准时,如果VCO振荡频率在目标范围内,对于目标分频比Ntarget,应该有Ntarget×P×tVCO与M×tREF相等,此时NA_CP=Ntarget,A_CP信号周期为NA_CP×P×tVCO;如果VCO振荡频率过低,P×tVCO增大,当增大到(Ntarget-1)×P×tVCO=M×tREF时,A_CP则会少1个P×tVCO周期,即NA_CP=Ntarget-1;如果VCO振荡频率过高,P×tVCO减小,当减小到(Ntarget+1)×P×tVCO=M×tREF时,A_CP则会多1个P×tVCO周期,即NA_CP=Ntarget+1。将A_CP信号通过MUX1输入到反馈分频器的FDIVN_EN端,触发电路通过A_CPN信号触发反馈分频器的输出FDIVN_OUT,从而进行频率检测。

图5 频率校准电路

图6 频率校准工作时序

校准模式下的反馈分频器依然根据输入的时钟fVCO/P进行计数,此时N与Ntarget相等,每个分频周期需要FDIVN_EN来进行复位。FDIVN_EN由原来通过FDIVN_OUT信号控制改为通过A_CP信号控制,可以实现A_CP信号的NA_CP个P×tVCO周期和反馈分频器的Ntarget个P×tVCO周期的比较。由于NA_CP可能会发生变化,而反馈分频器的Ntarget是固定的,所以FDIVN_OUT会有3种不同的情况。如图6(a)中所示,FDIVN_OUT'为NA_CP与Ntarget相等时的输出,此时反馈分频器计数时长N×P×tVCO与M×tREF的时间差不超过1个P×tVCO;FDIVN_OUT″为NA_CP与Ntarget+1相等时的输出,此时反馈分频器计数时长比M×tREF小1个P×tVCO以上;FDIVN_OUT‴为NA_CP与Ntarget-1相等时的输出,此时反馈分频器计数时长比M×tREF大1个P×tVCO以上。

AFC的触发电路由1个缓冲器BUF1、1个锁存器RS1、2个触发器DFF5和DFF6组成。触发电路分为2条检测路径,输入信号均为FDIVN_OUT,一条通过BUF1进行延迟,另一条通过锁存器RS1进行锁存,锁存器的复位信号是状态机输出的N2_ENQ,输出的信号再分别输入DFF5和DFF6,它们的CP信号是A_CPN信号。只凭借重定时电路A_CP信号触发反馈分频器FDIVN_OUT信号反映的3种频率比较状态不适于状态机中的数字电路处理。对于FDIVN_OUT信号,通过锁存器RS1后保留了下降沿的信息,在N2_ENQ的上升沿恢复为高;而通过BUF1保持和RS1的输出一样的下降沿延迟。触发电路时序如图6(b)所示,这样DFF5(Q2)和DFF6(Q2N)就可以产生出多种不同的情况,3种频率状态分别表示VCO频率与目标频率接近、过高和过低,比较结果用于数字电路控制VCO频率调整。

3 仿真及版图

通过仿真,整个VCO子频带可以覆盖2.65~3.15 GHz,每个子频带覆盖范围为30~50 MHz,KVCO为10~15 MHz/V。设置目标VCO频率为2949.12 MHz,启动自动校准后,电阻控制字RS[5:0]设为0x05,电容控制字CS[6:0]设为0x40,在TT条件下,利用仿真工具进行混合仿真,VCO自动校准时序仿真结果如图7所示,从20 μs开始,电路大约需100 μs完成整个自动校准过程,通过减少幅度检测和频率检测的确认次数,此时间可缩短到50 μs以内。

图7 VCO自动校准时序仿真结果

在本设计中,幅度校准电路实际版图和频率校准电路实际版图如图8所示,幅度校准电路的尺寸大约为400 μm×200 μm,频率校准电路的尺寸约为390 μm×70 μm。

图8 自动校准电路版图

4 测试与对比

锁相环频率综合器中的VCO校准模块测试环境包括电源、信号源、信号源分析仪和测试电路板,用于验证频率综合器输出时钟相位噪声受VCO自动校准功能的影响。

电路测试环境如图9(a)所示,在室温环境下,VCO工作在2949.12 MHz,VCO自动校准功能未开启时的相位噪声如图9(b)所示,24分频后输出122.88MHz时的1 MHz频偏处的相位噪声为-149.5 dBc/Hz,0.01~10 MHz积分抖动为124.5 fs。当开启VCO自动校准功能后,输出分频时钟相位噪声如图9(c)所示,带外相位噪声变为-152.5 dBc/Hz,抖动性能提高,0.01~10 MHz积分抖动减小为105 fs。

测试结果与现有国内外应用于低抖动频率综合器自动校准技术的研究成果对比如表1所示,可以看出,本文提出的自动校准电路在频率检测精度和输出相位噪声方面有一定优势。

图9 锁相环电路测试

表1 本文工作与其他文献比较

5 结论

本文提出了一种采用0.18 μm SiGe BiCMOS工艺设计的锁相环自动校准电路。该电路利用原有反馈分频器,通过参考信号对状态机频率检测脉冲进行重定时,再用反馈分频信号触发检测,实现了高精度频率检测。同时结合幅度检测,保证VCO工作在最佳子频带的同时处于最大输出幅度,得到最优的相位噪声性能。测试结果表明,该校准电路可以有效提高输出时钟信号的带外噪声性能,是超低抖动频率综合器电路的关键模块之一。