用于网络处理芯片的片上电源产生电路设计

2022-10-29闫振林温芝权靳新波史顺达

闫振林,温芝权,张 兵,靳新波,史顺达

(苏州雄立科技有限公司,江苏苏州 215000)

1 引言

网络处理芯片是实现计算机物理层所必需的功能器件,其信号处理的核心技术在于路由查找方案。比较成熟的专用集成网络处理芯片技术是基于三态内容寻址存储器(TCAM)实现的硬件路由查找,核心骨干网路主要采用的是TCAM和随机存取存储器(RAM)查找方案[1-2]。在基于静态随机存取存储器(SRAM)和硬件算法逻辑集成在搜索芯片内的方案中,路由表被内部可配优先级标记,使得表项维护无需像TCAM那样按照长度序列进行存储,大大减少了表项管理的复杂度[3-4]。

随着网络带宽的跨越式发展,网络处理芯片的处理速度和数据规模呈几何级数增长,芯片集成的功能模块快速增加,包括多通道高速输入/输出(I/O)接口、大规模SRAM、搜索引擎算法内核、时钟管理和复杂控制逻辑等模块,功能模块的片上供电管理问题日益重要。本文设计了一种用于网络处理芯片的片上电源产生电路。

2 电源产生电路结构

本文设计的用于网络处理芯片的片上电源产生电路如图1所示,包括高精度带隙基准电路、缓冲驱动电路、4个快速响应LDO电路和电压异常检测电路。电路采用外部供电电源,VCC=2.5~3.3 V,其中I/O接口电路直接采用VCC电压,内部大规模数字电路和模拟电路则采用图1所示的电路分模块供电。由高精度带隙基准电路产生1 V的参考电压,经运算放大器A1、电阻串R1~R5和MR1构成的缓冲驱动电路,得到不同的参考电源电压VR2、VR3和VR4。LDO1和LDO2根据VR2产生搜引擎内核和大规模SRAM(Block SRAM)供电电源电压VCC,CORE和VCC,SRAM,LDO3和LDO4分别根据VR3和VR4产生时钟电路模块和控制电路模块供电电源电压VCC,OSC和VCC,CTRL。分别通过异常检测电路对VCC,CORE、VCC,SRAM、VCC,OSC和VCC,CTRL进行检测,并在任何一路供电电源电压异常时产生错误信号Err,对芯片状态进行保护,提高整体芯片供电可靠性。电路中4个LDO电路分别用于给搜索引擎算法内核、大规模存储器、时钟管理和控制逻辑独立供电,实现细分功能模块的电源稳定性。由于VCC,CORE和VCC,SRAM需要提供大负载电流,并且芯片正常工作时需要快速响应,LDO1和LDO2均采用了动态偏置的快速响应LDO电路结构。图1中给出了LDO1的简化结构,误差放大器A2根据负载情况动态偏置。当负载电流突然增大时,LDO1的输出电压VCC,SRAM会突然降低,调整管MP1的状态会出现异常波动,动态偏置电路将会检测到该异常波动,并产生动态偏置电流Idb,误差放大器的总偏置电流增大为Ib+Idb,从而增加了信号带宽和瞬态响应速度。动态偏置电路通常由负载检测电路、比较器和动态电流源阵列构成[5]。

图1 片上电源产生电路结构

3 电路实现

3.1 带隙基准电路

传统带隙基准结构基于电压求和方式产生基准电压,并且运算放大器失调电压会影响基准电压的温度系数[6]。为得到高精度基准电压,尽可能降低失调电压的影响,本文通过NPN三极管电流求和的方式来生成1 V的带隙基准电压,所设计的带隙基准电路如图2(a)所示。MP1、MP2、MP3和A3、A4形成一个负反馈环路。Q1、Q2基极相连,流出正温度系数的电流I1、I2和负温度系数的I3。通过运算放大器的钳位,B1、B2、B3三点的电压相等,支路电流合并通过电阻R3产生1 V基准电压,此时A3和A4的失调电压不会影响到基准电压VBG。NPN三极管使用深N阱工艺,相对于传统的PNP三极管具有衬底干扰小的优势。图2(b)为所设计带隙基准电路的温度特性仿真结果,可以看出,在-25~100℃范围内,基准电压波动仅为2.2 mV。

图2 带隙基准电路实现及温度特性仿真曲线

3.2 电压异常检测电路

本文设计的电压异常检测电路结构如图3(a)所示,它由4个相同的电压异常检测单元电路、输出多路选择器(MUX)和数字滤波电路构成。当VCC,CORE、VCC,SRAM、VCC,OSC和VCC,CTRL中任何一个供电电源电压异常时,MUX将会产生错误信号Err0,然后数字滤波电路对错误信号进行处理,得到最终的Err,对芯片状态进行保护。电压异常检测单元电路内部包括一个由Rf和Cf组成的RC低通滤波器和一个迟滞比较器Comp1。以VCC,CORE为例,比较器负输入端直接连接到VCC,CORE,正端则连接到VCC,CORE经RC滤波后的信号。当外部干扰使得VCC,CORE产生一个高频波动时,比较器负输入端会直接产生高频波动,而正输入端信号经RC低通滤波后成为平缓变化的信号,此时比较器的输出将会发生变化,当正负端的信号差模量大于一定阈值时,比较器输出将会触发电压异常检测信号。为避免比较器输出震荡,本文采用了具有高频滤波和迟滞功能的比较器电路。为避免芯片上电过程中电压异常检测电路输出状态的不确定,电路由整体SoC芯片的控制电路统一管理,上电稳定之后控制信号才会开启异常检测电路。数字滤波电路采用高频计数器对Err0进行计数控制。正常情况下Err0为固定电平,当Err0电平突然改变后,滤波器内部的计算器将会开始计数,若计数时间大于16个时钟周期,将改变输出Err的状态,表示电源状态异常;若计数时间小于16个时钟周期,将不改变Err的状态,表示电源波动范围可控,无需发出电源状态异常信号,避免比较器经常性地开关对系统芯片造成危害。Comp1的电路如图3(b)所示,该电路由两级比较器、RC滤波器和施密特触发器级联组成。M31、M32、M33、M34、M37、M38、M39、M35和M36构成两级比较器。当输入电压Vin>Vref(参考电压)时,第一级比较器输出为低电平,第二级输出电压Vo1为高电平;当Vin<Vref时,即欠压状态,第一级比较器输出为高电平,Vo1为低电平。为提高Vo1的可靠性,在Vo1输出节点连接了带RC滤波器的级联反相器,由M310、M311、M312、M313、R31、R32和C31构成。M314、M315、M316、M317、M318、M319组成了施密特触发器,M320、M321、M322和M323组成了输出缓冲器。整体电路采用RC低通滤波和施密特触发器组合滤波,从而避免了高频干扰,以及经常性地开关状态变化对系统造成的危害。

4 电源产生电路在网络芯片中的应用

将本文设计的电源产生电路应用于一种基于SRAM和自适应映射算法实现的网络芯片中,网络芯片架构及芯片版图如图4所示。网络主处理芯片(NP)发出搜索键值的串行比特,芯片Serdes的RX_x24接口接收串行比特,Interlaken-LA(ITLA)模块从串行比特中恢复出搜索键值,发送给解包(Unpack)模块。解包模块对接收的搜索键值进行解析,并分发给搜索引擎内核(SEC)进行处理。处理完成后,搜索结果被发送给封包(Pack)模块,封包模块将搜索结果封装为ITLA接口格式,最终通过Serdes的TX_x12接口将搜索结果串行比特发送出去。Serdes模块包含了12组高速TX接口和24组高速RX接口,由外部供电电源VCC直接供电,VCC电压为2.5~3.3 V。外部供电电源同时给高可靠电源产生电路供电,分别产生1.0 V的VCC,CORE、1.0 V的VCC,SRAM、1.2 V的VCC,OSC和1.2 V的VCC,CTRL。VCC,CORE(含ITLA、Unpack、Pack供电电压)的设计负载电流为200 mA;VCC,SRAM的设计负载电流为50 mA;VCC,OSC的设计负载电流为5 mA;VCC,CTRL的设计负载电流为10 mA。采用本文设计的电源产生电路的网络芯片最终在28 nm工艺下实现。整体芯片尺寸为5 mm×8 mm,其中本文设计的片上电源供电电路占用芯片的尺寸为0.4 mm×1 mm,单个通道供电电源面积为0.1 mm2。

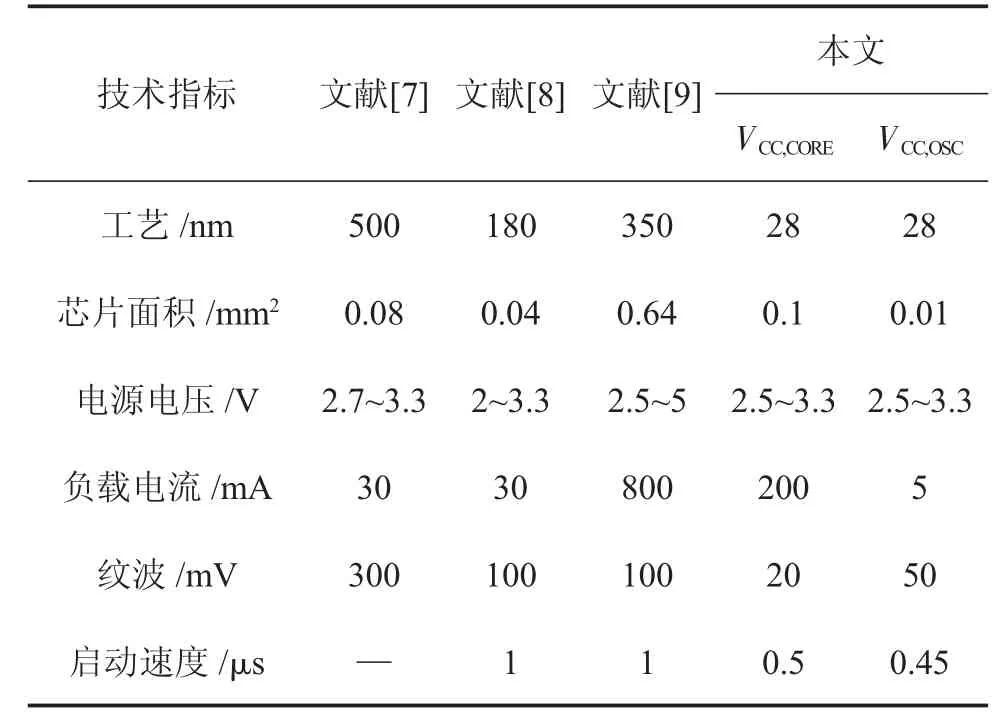

VCC,CORE仿真和测试结果如图5所示,图中ICC,CORE为搜索引擎内核电流。图5(a)为负载仿真波形,可以看出,ICC,CORE在150~250 mA变化时,VCC,CORE波动为35 mV。图5(b)为测试波形,3.7 μs后VCC,CORE供电正常,从3.7 μs到4.2 μs,近500 ns的延时内,提供近200 mA的负载电流。本文设计的4路供电电源的测试结果与现有文献的对比如表1所示,本文设计的电源电压的供电电流产生时间均不大于500 ns,具备快速响应的特点;电源纹波为20~50 mV,时钟电路的纹波相对较大,内核模块纹波较小。本文设计的片上电源供电电路具有相对更快的启动速度和更小的纹波。

图3 电压异常检测电路实现

图4 网络芯片架构及芯片版图

图5 VCC,CORE特性仿真和测试结果

本文技术指标 文献[7]文献[8]文献[9]VCC,CORE VCC,OSC工艺/nm 500 180 350 28 28芯片面积/mm2 0.08 0.04 0.64 0.1 0.01电源电压/V 2.7~3.3 2~3.3 2.5~5 2.5~3.3 2.5~3.3负载电流/mA 30 30 800 200 5纹波/mV 300 100 100 20 50启动速度/μs — 1 1 0.5 0.45

网络芯片测试系统包括解复位芯片、龙芯子卡和采用本文提出的电源产生电路的网络处理芯片,复位芯片先启动,然后龙芯子卡与网络处理芯片通信,相互发送协议数据。使用Robot框架对芯片中各模块的功能进行系统的测试。网络芯片功能测试结果如图6所示,可以看到12个matchN_hit_o(其中N=0~11)信号在有效期内都生成了对应的命中信号,12个matchN_index_o信号也在命中时产生了相应结果,芯片可以快速解析输入报文,并根据键值快速匹配查找表项,可针对不同的使用需求灵活选择。

图6 网络芯片功能测试结果

5 结论

本文针对网络协议处理芯片的片上供电问题,提出了一种采用分布式动态管理技术的片上电源产生电路设计方案。该电路通过给网络协议处理芯片内部存储器、搜索引擎算法内核、时钟管理和控制逻辑分别独立供电的分布式供电技术,实现了细分功能模块的电源稳定性,避免了相互干扰;另外设计了异常检测电路,结合数字滤波和模拟RC滤波等技术提高了抗干扰性能,在电路异常时产生错误信号,快速关断电源,提高了整体芯片供电可靠性。电路采用28 nm工艺,提供的最大负载电流达200 mA,满足网络芯片系统需求。