碳化硅与氮化硼协同增强PVDF电介质材料的设计与性能研究

2022-10-29张婷婷李雨凡赵天浩毕雪庆李玉超

张婷婷,李雨凡,赵天浩,王 振,毕雪庆,李玉超

(聊城大学 材料科学与工程学院 山东 聊城 252059)

0 引言

随着新能源领域的蓬勃发展,具有高介电常数、低介电损耗以及高储能密度的电介质材料成为了行业关注的热点。相比于传统的陶瓷电介质,聚合物复合电介质材料具有质量轻、柔性好、机械性能优异、易加工的特点,在微电子器件、电力工程及通讯技术等方面有着巨大的应用前景[1]。根据电介质储能理论,电介质材料的储能密度与其介电常数和击穿强度的平方成正比,但高的介电常数往往伴随着低的击穿强度。因此,如何同时提高电介质材料的介电常数和击穿强度,是当前电介质材料研究的重要方向之一[2]。

聚合物基复合电介质材料主要包括陶瓷填充聚合物复合电介质、导体或半导体填充聚合物材料、全有机电介质和三元或多元杂化体系聚合物材料[3,4]。其中,半导电填充聚合物复合电介质能够在提高材料介电常数的同时避免导电通路的形成,为获得高储能密度聚合物电介质材料提供了新的可能。南江等人[5]通过模压成型制备了聚四氟乙烯(PTFE)/碳化硅(SiC)纳米复合材料。研究发现SiC/PTFE复合材料的介电常数随SiC含量的增加有所提高,当SiC质量含量为10%时复合材料在100 Hz下的介电常数达到2.9,相比于PTFE材料(介电常数为2)提高了145%,然而SiC的加入同时也提高了材料的介电损耗(0.009)。传统的二元体系复合电介质材料已经不能满足行业研究的发展要求,因此越来越多的研究人员开始利用结构设计的方法改善电介质材料的储能特性。Yu等[6]将聚乙烯吡咯烷酮(PVP)包覆在BaTiO3(BT)纳米颗粒表面(PVP-BT),制备出了具有高介电性能的PVP-BT/PVDF复合材料。在含有55 %PVP-BT的复合材料中,1 kHz下的相对介电常数高达77,而介电损耗仅有0.05。Zhang等人[7]采用静电纺丝、溶液流延、热淬火和热压工艺制备了PVDF基三明治结构复合介电材料。中间层用BN包覆的四氧化三铁(Fe3O4@BN)作为“硬层”提高复合膜的击穿强度,以锆钛酸钡钙陶瓷(BZT-BCT)在两侧为“软层”用于增强复合膜的介电性能。结果表明,在100 Hz下体积分数3% BZT-BCT/5% Fe3O4@BN/3% BZT-BCT的复合材料介电常数达到17,击穿强度高达350 kV/mm,同时其能量密度升高到8.9 J/cm3。说明三明治结构复合材料通过多层膜的结构设计,充分展现了“软-硬”层协同作用,在提高材料介电常数的同时能够保持高击穿强度,进而达到提高材料储能密度的效果。

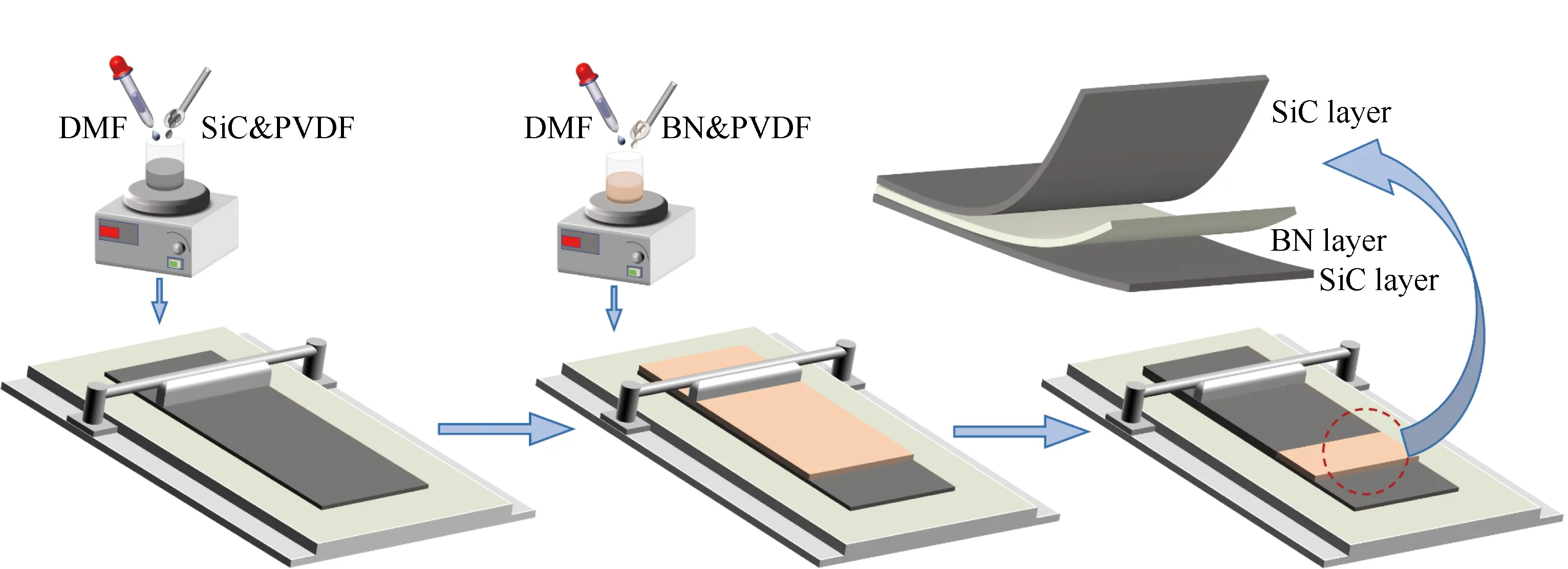

本实验利用溶液涂膜法制备了以PVDF为基体的三明治结构复合电介质薄膜(如图1所示),其中SiC/PVDF作为介电增强层,BN/PVDF作为击穿增强层,期望通过介电和击穿协同增强作用提高电介质材料的储能特性。

图1 三明治结构复合电介质材料制备示意图

1 实验部分

1.1 实验材料与仪器

聚偏氟乙烯(PVDF,Kynar740,1.78 g/cm3,Atofina Chemical Inc);聚苯乙烯磺酸钠(PSS,Mw=2×105,Sigma-Aldrich);六方氮化硼(BN,Mw=24.82,99.9%,粒径1~2 μm,Macklin);碳化硅(SiC,99%,平均粒径约50 nm,宏武新材料);N,N二甲基甲酰胺(DMF,ρDMF>98%,Sigma-Aldrich),异丙醇(IPA,ρIPA>98%,西陇化工厂),丙酮(Acetone,ρACE>99.5%,科密欧)

X射线衍射仪(XRD,D8 ADVANCE,布鲁克)、场发射扫描电子显微镜(FESEM,SIGMA500,卡尔蔡司)、同步热分析仪(STA,STA449C,耐驰)、精密阻抗分析仪(UC2876,优策)、耐击穿试验仪(ZJC-50KV,中航时代)、自动涂敷机(MSK-AFA-Ⅲ,合肥科晶)

1.2 材料的制备

1.2.1 氮化硼纳米片的剥离。本实验采用液相超声法剥离BN获得氮化硼纳米片(BNNs)[8]。首先称取0.3 g BN分散于75 mL IPA中,50 ℃下超声剥离3 h。随后将超声后的溶液自然静置8 h,取上层清液离心10 min(8 000 r/min),最后将剥离所得的BNNs在60 ℃下烘干后备用。

1.2.2 三明治结构复合膜。首先,称取0.01 g BNNs超声分散(30 min)在2 mL DMF中得到均匀溶液。然后向上述溶液中依次加入0.99 g PVDF和2 mL 丙酮,在80 ℃下物理分散1 h,得到质量分数1%的BN/PVDF溶液(B1)。按上述步骤分别制得2%、4% SiC/PVDF溶液(S2、S4)。

利用溶液涂覆法制备三明治结构复合薄膜。取2 mL(溶液浓度为15%)的S2溶液滴加到底板上,调节涂敷机刮刀高度为30 μm,刮涂后置于60 ℃烘箱干燥10 min,初步得到厚度为30 μm左右的单层SiC/PVDF薄膜;然后,将刮刀高度调整至60 μm后,取2 mL的B1溶液在干燥后的SiC-2薄膜上继续涂敷获得S2B1两层膜,再次烘干;最后设置刮刀高度为90 μm重复上述步骤,最终制得实际厚度为90 μm左右的三明治结构复合电介质薄膜S2B1S2。为比较不同复合材料的性能差异,本实验控制复合材料中BN的含量始终为1%,研究不同SiC含量对复合电介质材料的介电及储能性能影响。制备了不同BN、SiC含量的复合电介质薄膜,其组成如表1所示。

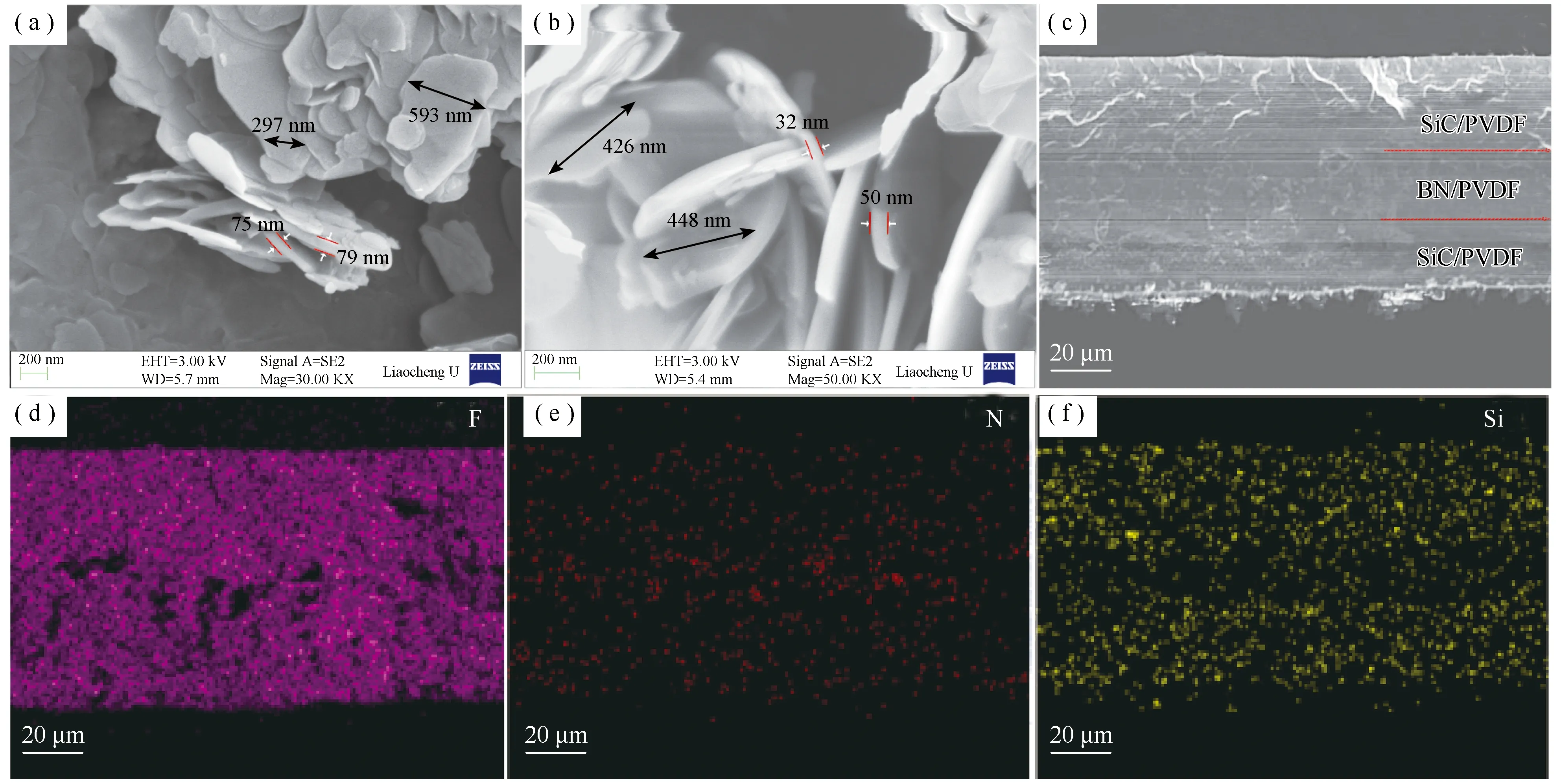

表1 不同BN、SiC组分含量的PVDF复合材料

2 结果与讨论

2.1 结构与形貌

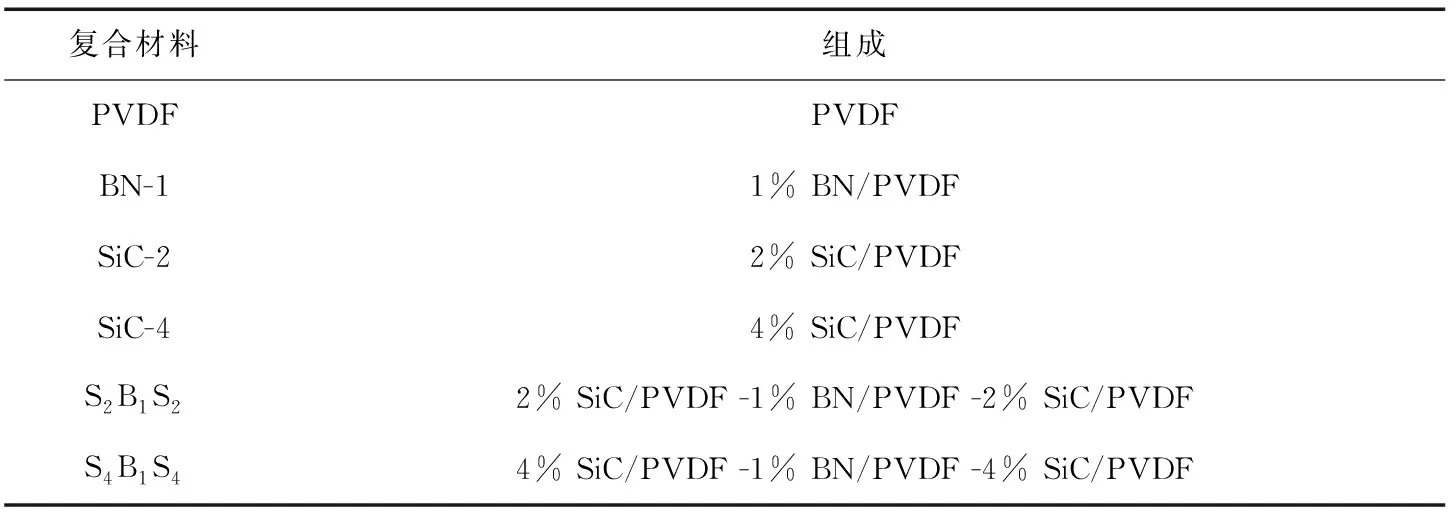

图2 BN,SiC填料及PVDF,S2B1S2薄膜的X射线衍射图谱

图2是BN、SiC填料以及PVDF、S2B1S2薄膜的XRD图谱。其中,2θ=18.3°、20.2°、26.6°和38.3°处的衍射峰分别代表α相PVDF的(020)、(110)、(021)和(002)晶面的特征峰[9]。2θ=35.7°的峰对应的是α相SiC的(101)晶面[10]。26.5°的峰对应BN的(002)晶面[11]。S4B1S4复合薄膜的XRD图包含了明显的α-PVDF、BN、SiC的特征峰,但SiC(35.7°)和BN(26.5°)填料的衍射峰强度显著降低,主要是由于两者含量较低导致。从三明治结构复合材料的XRD图谱中可以明显看出BN与SiC特征峰的存在。各图谱显示材料中无其他杂相的衍射峰,说明样品具有较高的相纯度。三明治结构复合电介质中PVDF的峰位基本不变,表明填料的加入及三明治结构的设计未改变聚合物基体的构型。

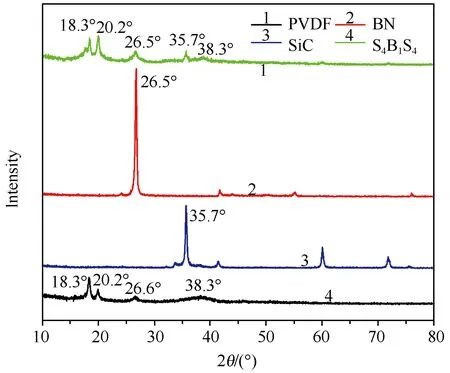

图3(a)和图3(b)分别是BN剥离前后的FESEM图。从图3(a)可看出剥离前的BN片相互堆垛在一起,大小和厚度不一。剥离后的BN(图3(b))结构比较疏松,片层间距较大,片尺寸略有降低,但片厚度并没有多大变化。图3(c)是S4B1S4的FESEM图,由图中可见填料在基体中分散均匀,不同填料填充的基体层间结合紧密。图3(d)、(e)和(f)分别是S4B1S4复合材料F、N、Si元素的元素分布图。从图3(d)、(e)和(f)可以看出,F元素在复合材料中整体分布,N元素和Si元素分别分布在中间层及上下两层,可以明显看出复合材料S4B1S4的三明治结构。

图3 剥离前(a)和剥离后(b)BN及S4B1S4复合材料(c)的SEM图;(d)、(e)和(f) 为S4B1S4复合材料元素分布图

2.2 介电性能

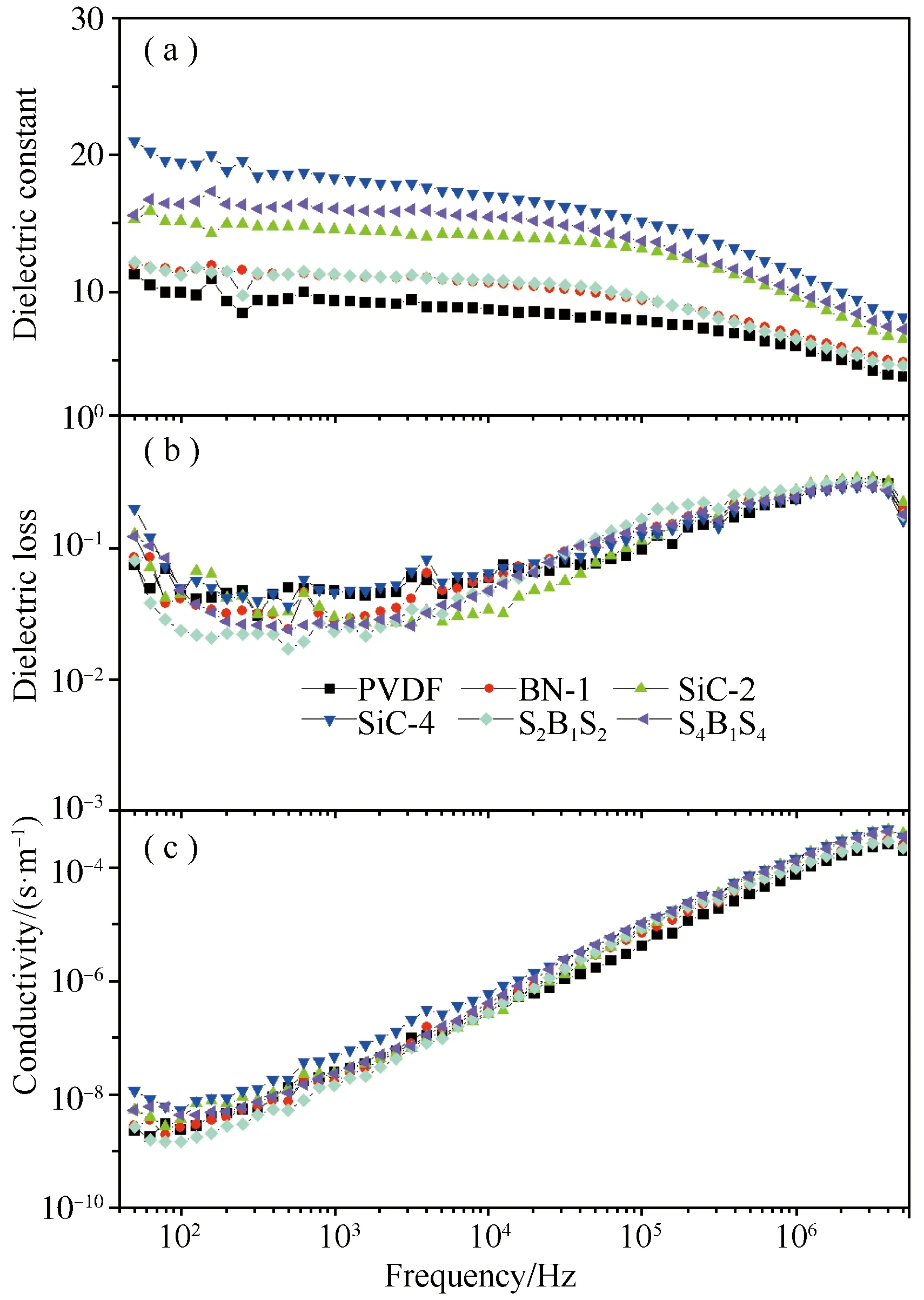

注:(a) 介电常数; (b) 介电损耗; (c) 电导率。图4 三明治结构复合材料介电性能测试图

图4(a)是复合材料介电常数的频谱图,从图中可以看出材料的介电常数具有很强的频率依赖性,介电常数随频率的增加而下降,这是由于高频下聚合物基体的偶极子转向受到抑制而产生了极化迟滞现象[12]。此外,复合材料的介电常数随SiC含量的增加呈现上升趋势。当SiC含量达到4%时SiC/PVDF复合材料的介电常数达到19.5,相比于纯的PVDF薄膜提高了1.97倍,说明SiC的引入有效促进了复合材料的极化;而氮化硼的引入对PVDF介电常数的提升影响较小。三明治结构复合材料SBS的介电常数介于BN-1和SiC-4之间,起到了明显的协同效用。图4(b)为电介质材料介电损耗的频谱图,从图中可以明显看出复合材料的介电损耗随频率的增加呈现先减小后增大的趋势。这是由于在低频率下聚合物的偶极子转向极化会产生较大的能量损耗,但随着频率的升高偶极子极化滞后于外电场变化,导致了介电损耗降低;当频率进一步升高,离子极化和电子极化发挥了更多的作用,从而使复合材料的损耗再次增大[13]。从图中可见BN-1的损耗值与PVDF相近,这是由于BN较好的绝缘性抑制了导电通路的形成,从而能够保持复合材料较低的介电损耗。三明治结构复合电介质材料相比于二元体系兼具有较高的介电常数和较低的介电损耗,表现出综合的介电性能。图4(c)展示了电介质材料电导率随频率的变化,复合材料的电导率随着交流电场频率的增加而增大,但始终保持在较低的水平。

2.3 击穿性能

图5 电介质薄膜材料Weibull击穿分布图

Weibull统计方法常被用来对材料的耐击穿性能进行分析[4]。Weibull分布可由

P(E)=1-exp ((E/E0)β0),

(1)

式中P为累计击穿的概率;E为材料的击穿场强;E0为击穿概率为63.2%时的击穿场强;β0为形状因子,用来表征介质材料的击穿场强分布情况。此公式可转化为式(2),式(2)中ln[-ln(1-P)]与lnE成线性关系,由此公式作图可得材料击穿性能的Weibull分布图。

ln[-ln(1-P)]=β0(lnE-lnE0)。

(2)

图5是纯PVDF和不同SiC、BN组分复合材料的击穿强度Weibull分布图,从图中可以看出材料的测试结果符合线性拟合规律。其中BN-1的击穿强度最高为127.1 kV/mm,这是由于BN的加入抑制了击穿的扩展,使材料表现出较为优异的击穿性能[14]。而添加半导性的碳化硅(SiC-4)后的击穿强度仅为43.3 kV/mm,较PVDF(98.2 kV/mm)有明显下降。三明治结构复合材料的击穿强度介于纯PVDF和BN-1体系之间,其中S2B1S2复合材料的击穿强度达107.0 kV/mm。这说明添加SiC在一定程度上降低了材料整体的击穿强度,而BN层的存在能够使三明治结构复合材料的击穿强度保持在较高水平。

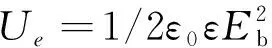

表2不同电介质材料的介电性能及储能密度

2.4 热学性能

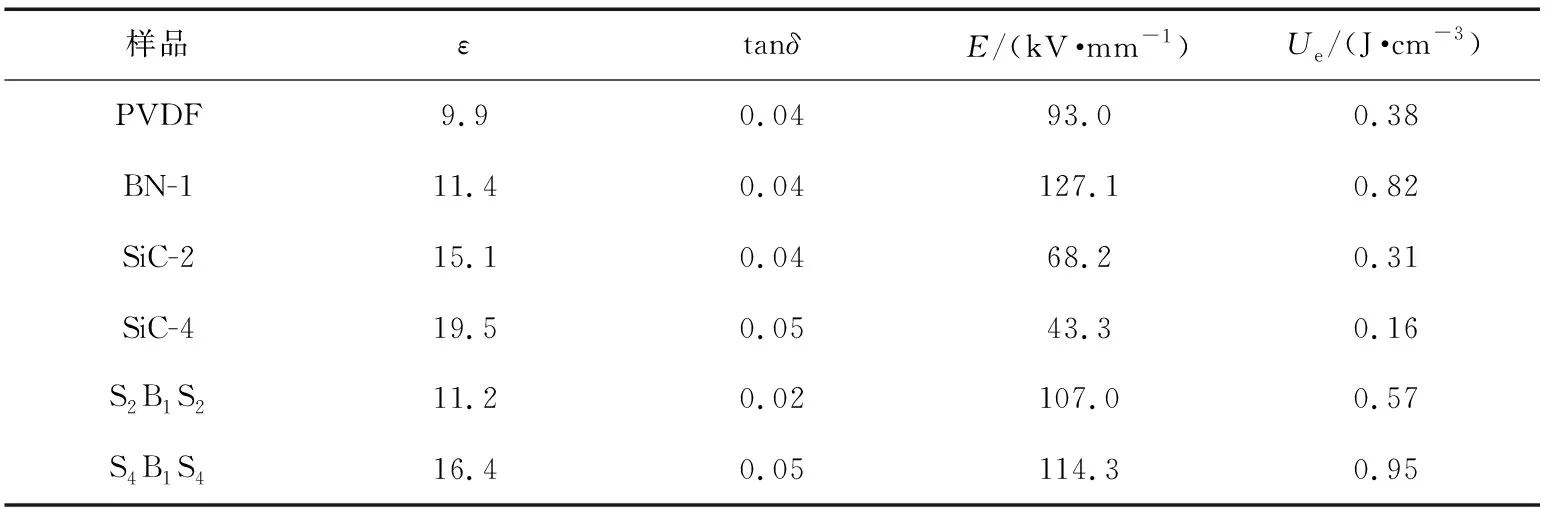

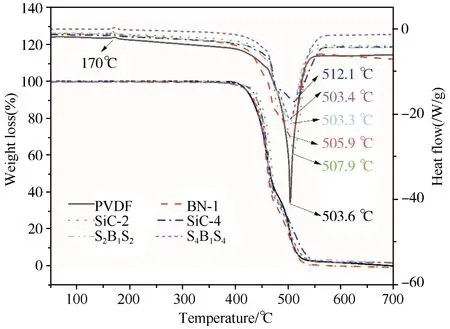

图6 复合电介质薄膜热学性能TG、DSC曲线

图6是PVDF、BN-1、SiC-2、SiC-4、S2B1S2及S4B1S4的热学性能曲线图。由图6可知,PVDF基复合材料的分解主要分为两个阶段,第一阶段(400~450 ℃)主要为复合材料中氟基团的脱除;第二阶段(450~500 ℃)主要为PVDF的氧化分解。由图6 DSC曲线可以看出170 ℃左右为PVDF的熔融峰,503.6 ℃是PVDF的分解峰;此外,由TG曲线可见PVDF在450~500 ℃温度范围内质量出现多次转折,分解速率先变缓后升高,主要原因在于氧气气氛下加速了材料的裂解。加入填料后的薄膜表现出与PVDF相似的降解趋势,说明填料的加入并未改变PVDF基体氧化分解过程。SiC/PVDF薄膜的分解温度随SiC含量的增加而提高。当SiC质量含量增加至4%时,分解温度达到512.1 ℃,相比PVDF薄膜(503.6 ℃)有明显提高。这是因为SiC的存在抑制了PVDF基体的热运动,阻碍了热分解过程中副产物的分解和挥发,同时SiC本身具有耐高温、热稳定性好的特点[16]。BN-1的分解温度为505.9 ℃,因此向PVDF基体中添加热稳定性高的填料,有利于提高材料的热分解温度。但不同含量的三明治结构复合电介质薄膜的分解温度均略低于PVDF,其中S4B1S4分解温度为503.4 ℃,S2B1S2分解温度为503.3 ℃。这可能是由于各层界面之间存在少量小分子分散剂,使得材料的界面结合能力减弱,因而降低了复合材料的热稳定性。

3 结论

本实验以SiC/PVDF作为介电增强相(S相),BN/PVDF作为击穿增强相(B相),利用溶液法交替涂膜制备了的具有三明治结构的PVDF复合电介质薄膜(SBS)。结果表明:三明治结构S4B1S4薄膜介质具有综合的介电储能特性,其介电常数为16.4,击穿强度为114.3 kV/mm,储能密度为0.95 J·cm-3,是纯PVDF薄膜(储能密度为0.38 J·cm-3)的2.50倍。因此,三明治结构的设计协同增强了电介质薄膜的击穿强度和介电常数,因而有效的提高了复合材料的储能密度,为制备性能优良的复合电介质材料提供了方向。