逐次逼近型模数转换器研究进展

2022-10-19田芮谦宋树祥刘振宇岑明灿蒋品群蔡超波

田芮谦, 宋树祥, 刘振宇, 岑明灿, 蒋品群, 蔡超波

(广西师范大学 电子工程学院, 广西 桂林 541004)

当前,市面上主流的模数转换器有快闪型模数转换器(Flash ADC)、流水线型模数转换器(Pipelined ADC)、积分求和型模数转换器(Sigma-delta ADC)和逐次逼近型模数转换器(SAR ADC)4种。Flash ADC以高速度的特点适用于需要较大带宽的应用,但功耗大、成本高、分辨率低的缺点使其应用场景受限。Pipelined ADC适用于中等速度和中等精度的场景,该结构具有良好的线性度和低失调特性,但其需要结构复杂和多级级联的模拟电路。Sigma-delta ADC具有很高的分辨率,但速度相对较慢,且在相同转换速率下,功耗比SAR ADC高。而SAR ADC以中等速度和精度、低功耗、面积小等优势在医疗、军事、便携式可移动设备等方面得到广泛应用,且以SAR ADC为核心的混合型ADC结构有着良好的发展前景。

1 SAR ADC原理与基本结构

图1 二分搜索法原理Fig.1 Schematic of binary search method

SAR ADC利用二分搜索法(也称折半查找法)原理[1],将采样后的输入信号与DAC产生的信号经比较器比较得出数字高低电平。比较器每进行1次比较,得到1位数字输出码,并通过SAR逻辑电路对电容阵列的开关调整1次。开关每进行1次调整,也意味着参考电压进行了折半,最终可得到不断逼近输入信号值的数字输出码。二分搜索法逐次逼近过程如图1所示。

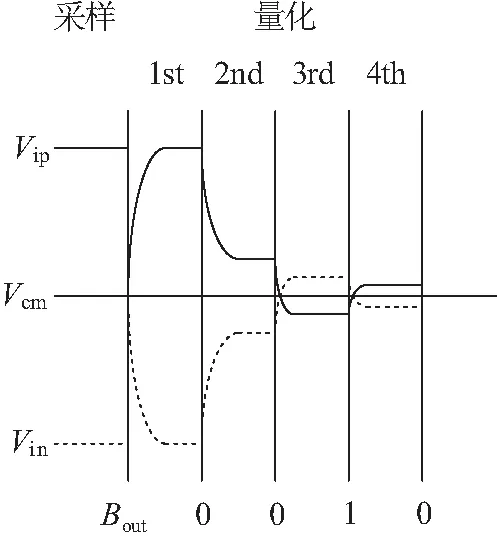

以3 bits传统SAR ADC为例对转换过程[2]进行具体分析,分析过程如图2所示。

在第1个工作状态,电路开始采样,电容阵列上极板接至共模电平Vcm,下极板分别接输入信号Vip、Vin,此时,比较器正负两端电荷分别为:

Q+=23(Vcm-Vip)C,

(1)

Q-=23(Vcm-Vin)C,

(2)

且

Vcm=(Vip+Vin)/2。

(3)

采样结束后,先后断开共模电平和采样开关,可减少电荷注入对电路造成的影响。

图2 3 bits传统SAR ADC转换过程[2]Fig.2 3 bits traditional SAR ADC conversion process[2]

第2项工作进行最高位电容的转换。将最高位4C电容预置为1,即比较器正端最高位电容下极板接Vrefp,其余位电容接Vrefn,比较器负端与之相反。此时比较器正负两端电荷量变化为:

Q+=22(VP1-Vrefp)C+22(VP1-Vrefn)C,

(4)

Q-=22(VN1-Vrefn)C+22(VN1-Vrefp)C。

(5)

由式(1)、(3)和(4)可得,此时比较器正端电压变化为

(6)

由式(2)、(3)和(5)可得,此时比较器负端电压变化为

(7)

因此,比较器正负两端电压差值为

ΔV=VP1-VN1=-(Vip-Vin)。

(8)

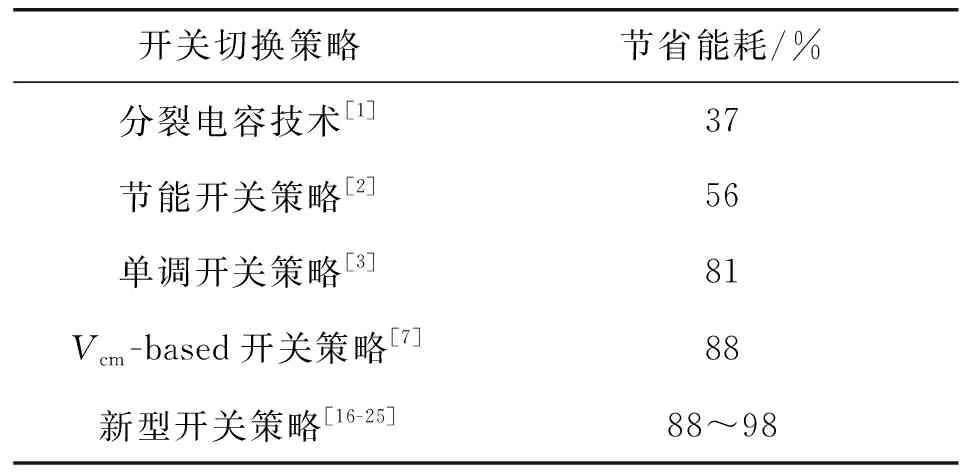

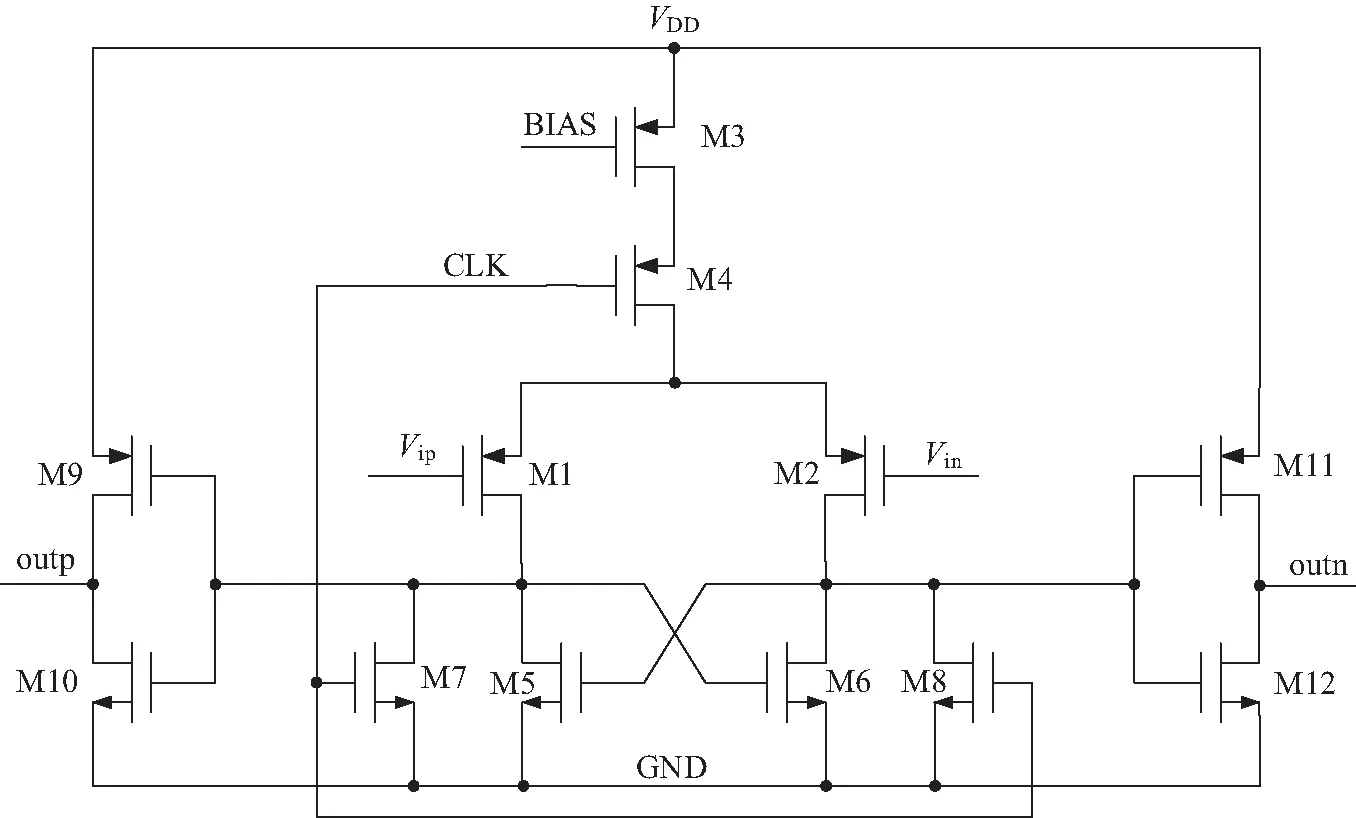

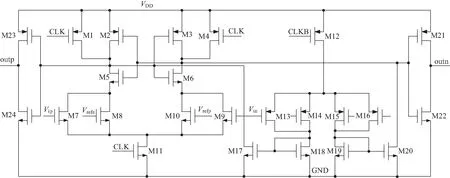

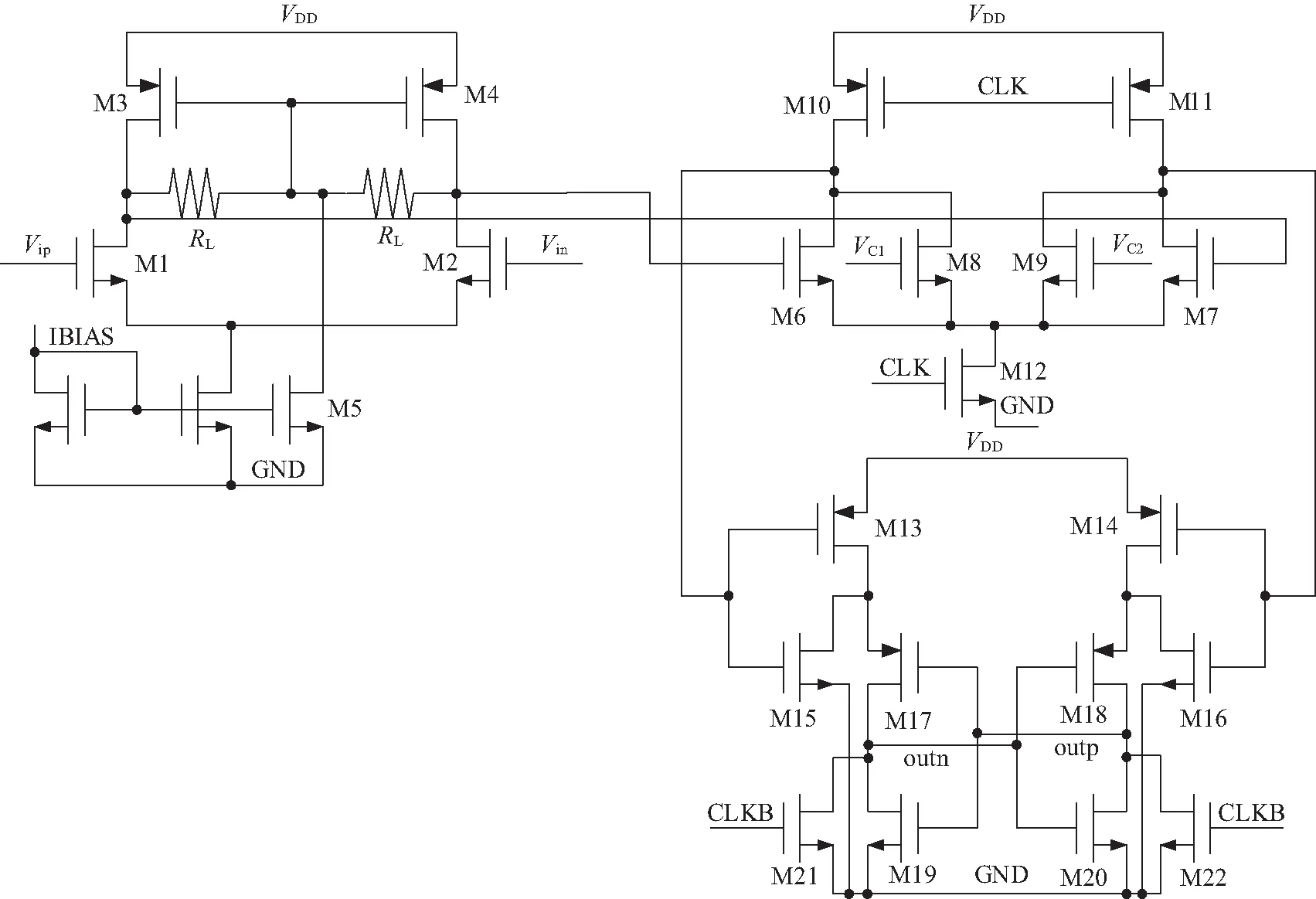

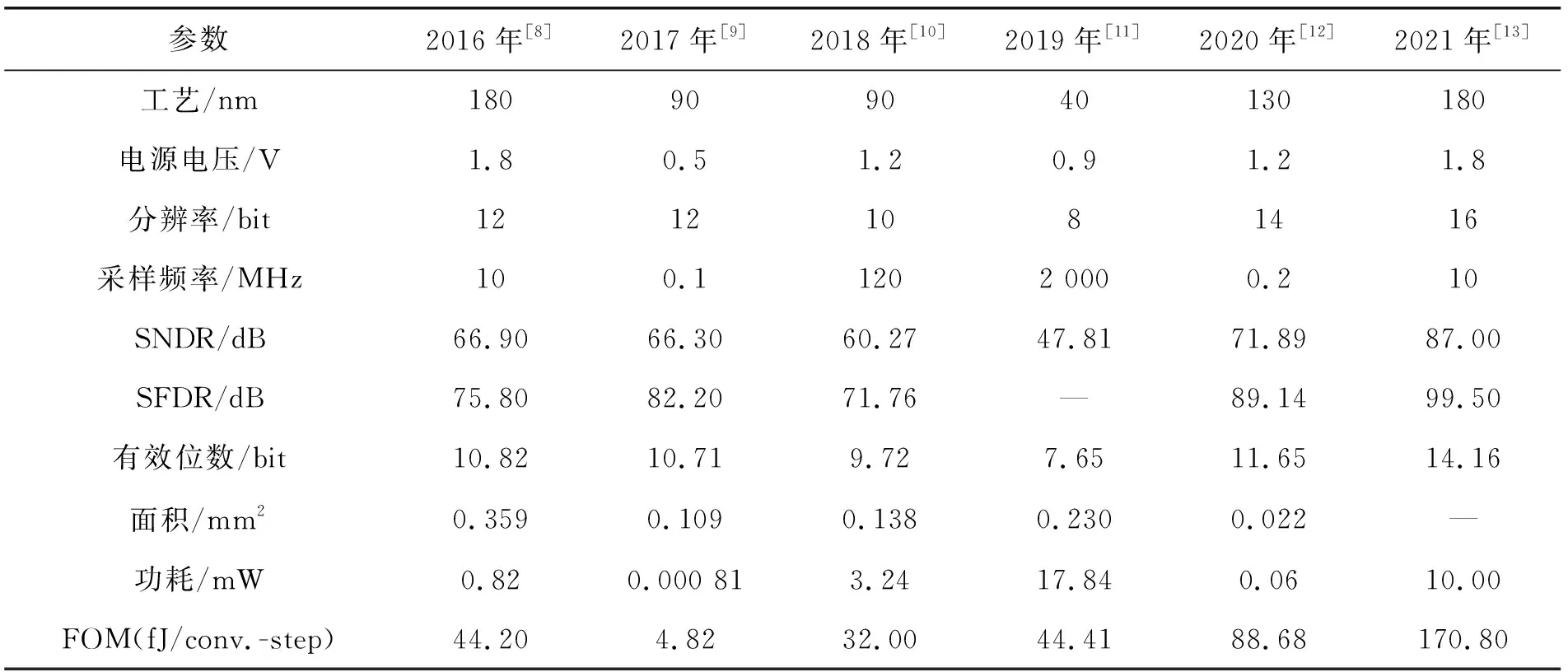

当ΔV>0时,VP1>VN1,B1=1,与预置结果相同,电容阵列开关接法保持不变;当ΔV<0时,VP1 第3项工作进行次高位的转换。假设B1=1,将次高位电容2C预置为1,同理,将比较器正端次高位电容下极板接Vrefp,其余位电容接Vrefn,比较器负端与之相反。此时比较器正负两端电荷量变化为: Q+=(22+21)C(VP2-Vrefp)+21(VP2-Vrefn)C, (9) Q-=(22+21)(VN2-Vrefn)C+21(VN2-Vrefp)C。 (10) 由式(1)、(3)和(9)可得,此时比较器正端电压变化为 (11) 由式(2)、(3)和(10)可得,此时比较器负端电压变化为 (12) 因此,比较器正负两端电压差值为 (13) 当ΔV>0时,VP2>VN2,B2=1,与预置结果相同,电容阵列开关接法保持不变;当ΔV<0时,VP2 (14) SAR ADC由采样电路、电容阵列DAC、比较器、SAR逻辑时序电路组成。表1对SAR ADC结构以及各模块采用的技术进行对比。通过对比可知,大多数SAR ADC都选择栅压自举开关作为采样开关,因其具有较高的线性度和良好的DNL、INL性能参数,而用于降低电位的控制开关可选择结构简单、功耗更低的传输门开关。在采样方式的选择上,顶板采样与大多数开关切换策略具有良好的适配性,可减少切换过程中的能耗。但对于10 bits以上的SAR ADC来说,电荷注入和时钟馈通效应导致电路不能满足高精度要求,因此选择底板采样较为合适。电容数量随着ADC位数呈指数上升,引入桥接电容可降低电容阵列数量和面积。此举同样可以降低对采样开关的线性度要求,加快CDAC建立时间[3-7]。另外,由于电容阵列是SAR ADC功耗的主要来源之一,各种可以降低功耗的新型开关切换策略也是屡见不鲜。对于比较器的选择,动态比较器具有全摆幅输出、静态功耗为0、输入阻抗高的优点。在满足电路设计的基础上,再结合高速、低噪声等需求选取双尾比较器、低噪声动态锁存比较器等。异步逻辑时序电路通常作为时序设计的首选,因为该逻辑的信号状态由前一时刻信号决定,可对每一转换周期的时间按需分配。并且时序逻辑电路作为SAR ADC结构中又一能量消耗模块,要尽可能降低电路规模减小功耗。 表1 SAR ADC结构对比 DAC的实现方式多种多样,主要分为电压定标型、电流定标型、电荷定标型和混合型DAC。电荷定标型DAC,又称电荷重分配DAC,由于电容具有存储电荷且不需要单独采样保持电路的特性,成为DAC的首选。此外,与CDAC相结合的开关切换策略是提高ADC性能的关键技术。 文献[14]提出分裂电容技术,将MSB位电容拆分成子电容,减少了开关动作的次数和电容充放电的繁琐过程,在切换过程中节约了能量。文献[15]提出适用于生物医疗等低功耗场景的节能开关序列,与传统切换技术相比节省56%的能量。文献[16]提出单调开关切换策略。该方案省略了传统方法中对预置位进行纠错的过程,减少了能量消耗。但缺点是共模电平会不断下降,且比较过程中电压值的偏差会导致精度不够[17-19]。文献[20]提出Vcm-based开关切换方法。该方法中比较器正负两端开关动作对称,差分输入信号的逐次逼近过程也是对称的。若比较器失调电压随共模电平变化,将影响DAC线性度进而破坏ADC的动态性能。当比较器中构成正反馈的晶体管发生阈值失配时,比较器失调电压随共模电平增高而增大。当共模电平由300 mV升高至450 mV时,比较器失调电压变化幅度为1.66 mV[21]。可以通过减小晶体管尺寸的方法降低比较器失调影响。相比于单调开关切换方法,该方法的共模电平保持不变,因而很好地改善了共模电平衰减带来的比较器失调问题[22]。文献[23]提出一种新型开关切换策略,该方法只需2N-1个电容,并且由于1/2Vref充放电至Vref或地的电位都是原来值的一半,DAC电容阵列的建立时间也缩短一半。文献[24]中将单调开关切换方法和Vcm-based开关切换方法相结合[8,10,12,24-28]进行改进。此类方法除了省去采样至采样结束这一阶段的开关切换能量外,还将最高位电容所接参考电平设置为与第一次比较相同的电位,便可将第一次比较阶段的切换能量也省去,并且在设计过程中避免了比较器失调电压随共模电平变化带来的影响。文献[29]中提出利用2个桥接电容将电容阵列分为三段,并通过冗余位和权重比例实现电容值分配;设计几个冗余位电容便有几次纠错的机会,文中16位SAR ADC的有效位数可达15.87位[29]。该方法还将高位电容拆分成多个单位子电容从而减少能量的消耗。表2展示了以10 bits CDAC为例,不同类型开关策略与传统开关策略相比节省的能耗对比。 表2 开关策略能耗对比 基于传统开关切换技术的SAR ADC能耗不能满足当今便携式设备的低功耗要求,尽管多年来研究人员提出的方案可降低开关切换能耗,但这些方法仍存在诸多问题。例如,单调开关切换技术存在共模电平下降、线性度差的缺点。虽然引入一个共模电平可以解决该问题,但需要额外的共模电平产生电路,这也提升了ADC整体能耗。若改变这种传统开关切换技术,将可以降低SAR ADC能耗的同时提升其线性度,线性度得到了改善,ADC的精度也会得到提升。 SAR ADC逐步向高精度ADC领域发展,而在高精度领域常采用底板采样的工作模式,因此与底板采样适配且相较于传统方案功耗更低的Vcm-based开关切换方法成为研究人员的首选。另外,能够平衡能源效率、实现良好共模控制的分裂电容技术也是选择的主要方案。总的来说,分裂电容技术和Vcm-based开关切换方法相结合的新型开关切换策略有着良好的发展前景,并且在此基础上能够检测跳变的开关降耗技术也是今后研究的重点内容。对于算法的优化,根据信号的变化方式预先判断对开关进行设置来减少切换动作从而降低功耗的LSB-first逐次逼近算法也是今后研究的主要方向。 比较器结构一般分为开环比较器和动态锁存比较器2种,但传统的比较器不能满足如今的设计需求。因此,带有前置放大器的动态锁存比较器、轨对轨输入比较器等新的设计方案陆续被提出。图3是一个基本动态锁存比较器结构[9,11,30-33]。该比较器工作过程分为复位和比较两阶段。当CLK为高电平时,比较器处于复位阶段,M7、M8导通将输入对管漏端电压拉至地,从而输出端outp、outn复位至高电平。此时电路中没有形成通路,因此没有静态功耗。当CLK为低电平时,比较器处于比较阶段,M1、M2、M5、M6构成2对交叉耦合电路形成正反馈,将输入信号拉至两极从而outp、outn输出相反电平。 图3 动态锁存比较器[30]Fig.3 Dynamic latch comparator[30] 图4 轨到轨动态锁存比较器[34]Fig.4 Rail-to-rail dynamic latch comparator[34] 随着技术规模的不断发展,对器件尺寸、电源电压、功耗等要求都更加严格。电源电压逐步降低,输入范围也随之降低。因此文献[34]提出轨对轨动态锁存比较器以补偿共模范围降低的损失,如图4所示。该结构由PMOS和NMOS作为输入对管的2组动态锁存器,将其中一个输入端相连而成。当CLK为低电平时,比较器将输出复位至低电平;当CLK为高电平时,比较器两端同时比较,迅速输出比较结果。其优点是可以增加输入摆幅范围,具有更短的建立时间,获得更高的有效位数。为了避免比较器失调的影响,应注意输入对管的尺寸与匹配问题[35-39]。 文献[13]提出一种前置放大器和动态锁存相结合的低噪声比较器,如图5所示。该结构由第一级高增益、高带宽的前置运算放大器和第二级动态锁存结构组成。该前置放大结构可降低晶体管失配带来的比较器失调电压的影响,并通过对其增益的调整实现噪声动态配置,还利用一个保护电路避免反冲噪声对运放的影响。第二级动态锁存结构同样利用正反馈使得输入信号迅速分离得到比较结果,其中晶体管M13、M14不仅起到了预充电的作用,还作为第二级的输入对管使用。因此通过对第二级运放增益的调整可提高比较器精度。相较于传统比较器,该低噪声比较器在电源电压VDD为1 V,采样频率为4 GHz,共模电平Vcm为0.6 V的条件下,比较器失调电压由21.5 mV降低至13.5 mV,比较器噪声由2.1 mV降低至0.66 mV,降低了约3倍[40-41]。 另外,双动态锁存结构比较器[42-43]的两路锁存电路交替工作,当一个锁存器复位时,另一个进行比较,比较完成后二者交换工作状态。无论哪一路锁存器工作,从整体上来看,比较器没有复位状态始终进行比较工作。因此相较传统比较器而言,该比较器节省了一半的量化时间,提高了ADC的速度。文献[44]提出的改进型SR锁存比较器,在1.5 V电源电压,0.1 MHz时钟频率下,其分辨率达到0.732 mV,功耗仅为0.19 nW,实现了高分辨率低失调电压的稳定输出[44]。一种多比较器结构可以分别设计高精度比较器和高速度比较器结合使用。当比较CDAC高位时,可进行粗量化,要求速度快;当比较CDAC低位时,可放慢速度追求比较的准确性,要求高精度。比较器性能需要在速度和增益之间折衷,而增益主要受噪声影响。提高比较器速度可以通过增大动态比较器的尾电流管和输入对管尺寸来实现,但此法会引入CDAC的反冲噪声。提高比较器增益可以选取级联结构、双尾比较器或浮动逆变放大器等结构。总的来说,一种能够保持良好噪声性能,又能提高比较器速度的延迟交叉耦合技术和基于VCO-based比较器的速度提高改进技术是今后研究的重点。此外,随着先进工艺不断发展,与时域比较器相结合的多比较器结构也是人们重点关注的对象。 图5 低噪声比较器[38]Fig.5 Low noise comparator[38] 由于电源或地的寄生效应、Vref的驱动能力有限或比较器噪声等因素,数字输出码发生转换错误,且模拟输入电压值与数字输出码是一一映射的,因此二进制电容阵列的逐次逼近过程不允许有任何转换错误,为解决此问题提出了冗余校准技术。对一个输入电压值进行量化,其正确量化结果为“0100”,如图6(a)所示;若其次高位错误量化为“0”,为弥补该失误,后两位将不断逼近正确值“0100”,如图6(b)所示;现增加一冗余位,其权重值为7、4、2、1、1,量化过程如图6(c)所示,输出结果为“00111”;假设在权重值“4”时比较错误,则权重“2+1+1”仍可对该错误进行弥补,如图6(d)所示,输出结果为“01000”,与正确量化结果相同。虽然冗余技术增加了一次比较过程,但可以确保比较结果的准确性。此外,在一些情况下,该技术还可以提高采样率[45-48]。 图6 冗余校准Fig.6 Redundancy calibration 文献[49]提出改进型数字自校准技术。该技术通过校正电容校正比较器的静态偏移和电容阵列的失配,在采样频率为200 kHz,输入信号频率为46 kHz条件下,有效位数由10.64 bits变为11.59 bits,提高了一位,SNDR由65.85 dB提高至71.55 dB,SFDR由78.83 dB提高至91.82 dB[49]。自校准技术属于前台校准方法,分为校准模式和工作模式2个阶段。时钟产生电路提供2组时钟:一组用于误差估计,根据比较器的比较结果选择合适的补偿电容,并对比较器的失调误差进行校正,再对电容阵列的失配进行检测;另一组用于正常电路的逐次逼近转换,通过比较器得到数字输出码,再反馈到电容阵列进行下一次比较的配置。这2组时钟通过一个使能信号来选择工作模式,将正常转换下的数字码与产生的误差码求和得到最终结果[50-53]。 校准技术主要针对比较器失调和电容失配两大问题而展开,校准技术的选择基于所设计电路的本身特性。利用数字逻辑电路校正电容器得到的校正码控制电容阵列开关切换技术、利用伪随机码抵消抖动的数字后校准技术和与输入信号无关的动态段指定法等都有效地提高了ADC精度[54-63],并成为今后研究的主要方向。 表3 SAR ADC参数对比 本文总结了SAR ADC设计的一些经典结构与方案,如传统电容阵列开关切换、动态锁存比较器等,也介绍了一些新的设计方法,如混合型开关切换策略、低功耗噪声可配置比较器、冗余校准等,但这些方法仍然存在一些不足和局限性,值得探讨与改进。 工艺的演进使得数字集成电路飞速发展,却给模拟集成电路设计带来了很大的局限性。首先,工艺尺寸的缩小导致版图寄生效应增大,晶体管沟道长度的缩小带来了严重失配、线性度降低的问题。并且随着电源电压的不断下降,信噪比也随之下降。因此在低电源电压下,通过消除采样开关KT/C噪声技术维持高信噪比并降低功耗是一个值得研究的问题。其次,与SAR ADC相结合的各类混合架构也具有良好的发展前景,Flash-SAR ADC结合了Flash高速的优势但受比较器个数的限制,通常只做到3位;Pipelined-SAR ADC分别结合了二者高速和低功耗的优势,但对于实现高性能运放的设计有一定困难;多通道的时域交织ADC可以实现高转换速率,但也增加了功耗,因此要对二者折衷考虑。上述结构皆属于奈奎斯特型ADC,而噪声整型ADC属于过采样型ADC,高精度是其最显著的特征,也是如今最主流的研究方向。利用失配误差整形技术解决器件失配,改善电路线性度和噪声整形技术,降低对高性能模拟电路的依赖性并提高对先进工艺的兼容性是ADC主要解决的问题。总体而言,SAR ADC正向高速度、高精度、低功耗的方向稳定发展。

2 电容阵列DAC的开关切换技术

3 比较器

4 数字校准

4.1 冗余技术

4.2 自校准技术

5 模数转换器

6 展望